4

ет to

4

Изобретение относнто.я к автоматике и вычислительной технике и может е)ыть использовано в растровых устройствах отображения графической информации.

Цель изобретения - псвышение быстродействия устройства.

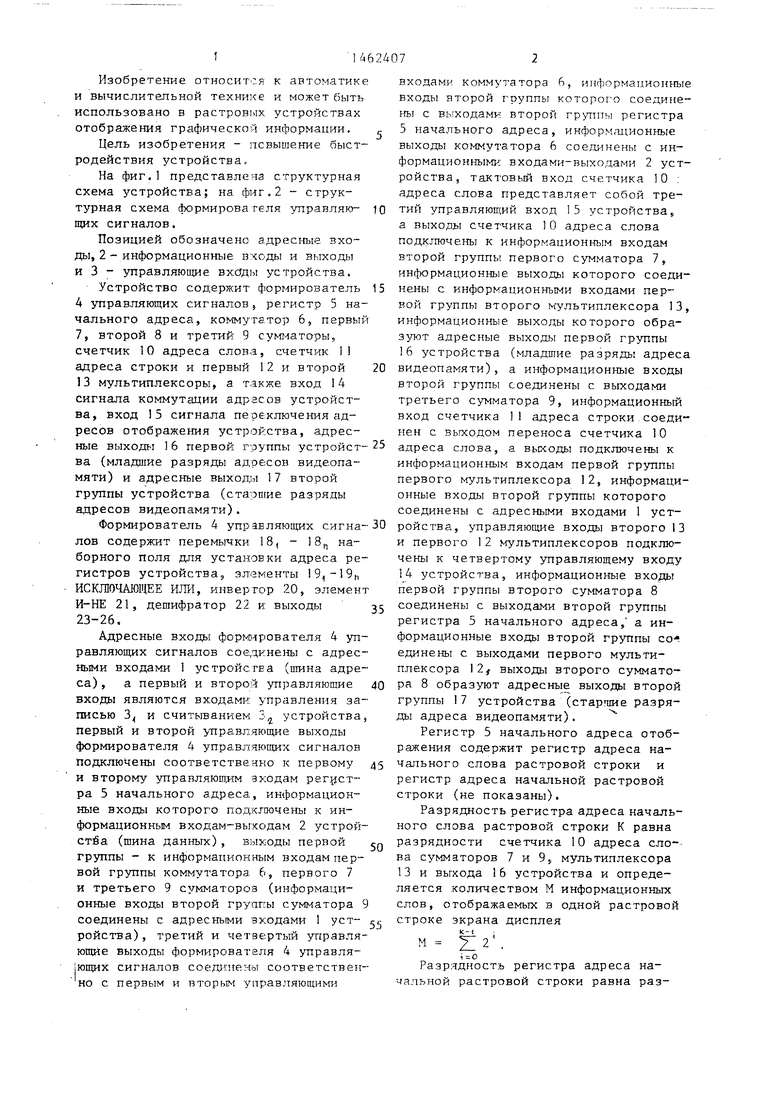

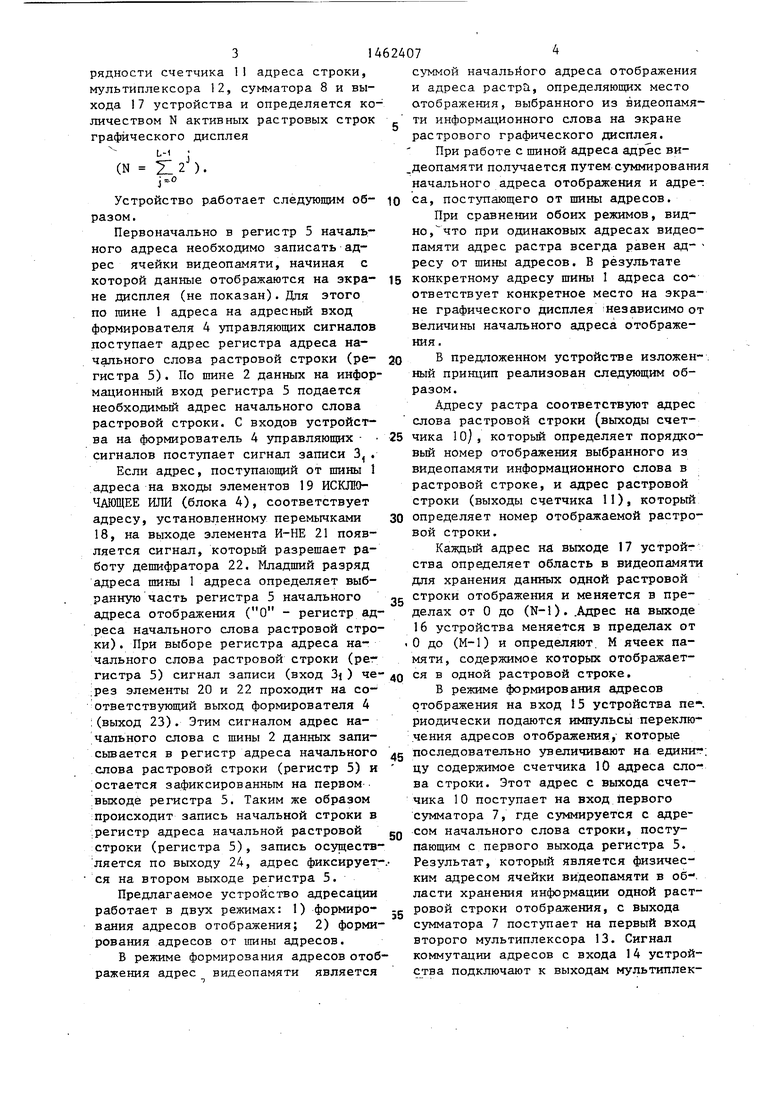

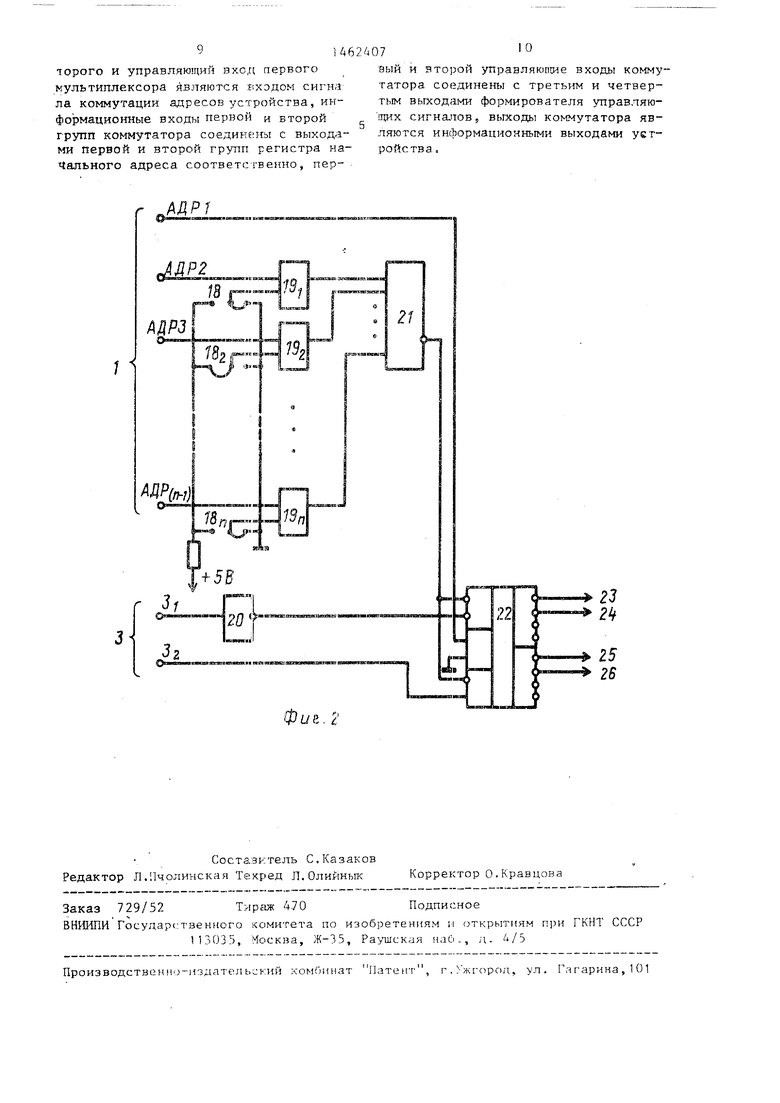

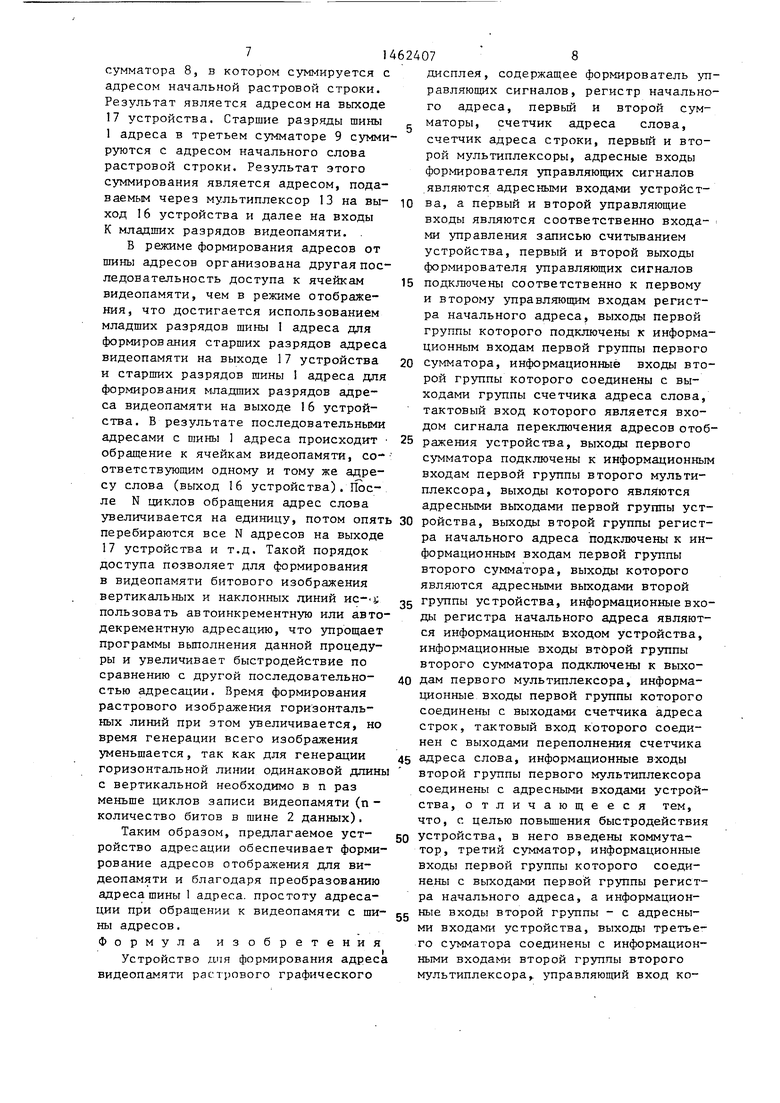

На фиг.1 представлена структурная схема устройства; на фиг.2 - структурная схема фс1рмирова геля управляю- щих сигналов.

Позицией обозначено адресные входы, 2 -информационные входы и выходы и 3 - управлягоп95е вхОды устройства.

Устройство содержит формирователь 4 управляющих сигналов, регистр 5 начального адреса, коммутатор 6, первый 7, второй 8 и третий 9 сум1 1аторы,, счетчик 10 адреса слова, счетчик 1 адреса строки и первый 12 и второй 13 мультиплексоры, а также вход 14 сигнала коммутации адресов устройства, вход 15 сигнала переключения адресов отображения устройства, адресные выходы 6 первой группы устройства (младшие разряды адресов видеопамяти) и адрес1й1е выходы 17 второй группы устройства (старшие разряды адресов видеопамяти).

Формирователь 4 управляющих сигналов содержит перемычки 18, - 18 наборного поля для установки адреса регистров устройства, злементы 19,-19„ ИСКЛЮЧАЮЩЕЕ ИЛ1, инвертор 20, элемент И-НЕ 21, дешифратор 22 и: выходы 23-26,

Адресные входы форг п рователя 4 управляющих сигналов соединены с адресными входами 1 устройства (шина адреса) , а первый и второй управляющие входы являются входами: управления записью 3 и считыванием 3 устройства первый и второй управляющие выходы формирователя 4 управляющих сигналов Подключены соответственно к первому и второму управляюшдм зходам регуст- ра 5 начального адреса, информационные входы которого подкгоочены к информационным входам:-вьгходам 2 устройства (щина данных) , Е1з х-оды первой группы - к информапионным входам первой группы кoм lyтaтopa 6, первого 7 и третьего 9 сумматоров (информационные входы второй группы сумматора 9 соединены с адресными входами 1 уст- ройства), третий и четвертый управляющие выходы формирователя 4 управляющих сигналов соединены соответственно с первым и вторым управляющи га

входами коммутатора 6, информационны входы второй группы которого соеди е ны с выходами второй группы регистра 5 начального адреса, информационные выходы коммутатора 6 соединены с ин- формационными- входами-выходами 2 устройства, тактовый вход счетчика 10 ; адреса слова представляет собой третий управляющий вход 15 устройства, а выхода счетчика 10 адреса слова подключены к информационным входам второй группы первого сумматора 7, информационные выходы которого соединены с информационными входами первой группы второго мультиплексора 13 информационнь е выходы которого образуют адресные выходы первой группы 16 устройства (младшие разряды адрес видеопамяти), а информационные входы второй группы соединены с выходами третьего сумматора 9, информационный вход счетчика 1 адреса строки.соеди нен с выходом переноса счетчика 10 адреса слова, а выходы подключены к информационным входам первой группы первого мультиплексора 12, информационные входы второй группы которого соединены с адресными входами 1 устройства, управляющие входы второго 13 и первого 12 мультиплексоров подключены к четвертому управляющему входу 14 устройства, информационные входы первой группы второго сумматора 8 соединены с выходами второй группы регистра 5 начального адреса, а информационные входы второй группы со единены с выходами первого мультиплексора 12 выходы второго сумматора 8 образуют адресные выходы второй группы 17 устройства (старшие разряды адреса видеопамяти).

Регистр 5 начального адреса отображения содержит регистр адреса начального слова растровой строки и регистр адреса начальной растровой строки (не показаны).

Разрядность регистра адреса начального слова растровой строки К равна разрядности счетчика 10 адреса ело-- ва сумматоров 7 и 9, мультиплексора 13 и выхода 16 устройства и определяется количеством М информационных слов, отображаемых в одной растровой строке экрана дисплея

K-l

М 21 2

Разрядность регистра адреса начальной растравой строки равна разрядности счетчика 1 адреса строки, мультиплексора 12, сумматора 8 и выхода 7 устройства и определяется количеством N активных растровых строк графического дисплея L-i ;

(N Z 2 ) . j.o

Устройство работает следующим образом.

Первоначально в регистр 5 начального адреса необходимо записать адрес ячейки видеопамяти, начиная с которой данные отображаются на экране дисплея (не показан). Для этого по шине 1 адреса на адресный вход формирователя 4 управляющих сигналов поступает адрес регистра адреса начального слова растровой строки (регистра 5). По шине 2 данных на информационный вход регистра 5 подается необходимый адрес начального слова растровой строки. С входов устройства на формирователь 4 управляющих сигналов постзшает сигнал записи 3.

Если адрес, поступающий от пганы 1 адреса на входы элементов 19 ИСКЛЮЧАЮЩЕЕ ИЛИ (блока 4), соответствует адресу, установленному перемычками 18, на выходе элемента И-НЕ 21 появляется сигнал, который разрешает работу дешифратора 22. Младший разряд адреса шины 1 адреса определяет выбранную часть регистра 5 начального адреса отображения (О - регистр адреса начального слова растровой строки) . При выборе регистра адреса начального слова растровой строки (per гистра 5) сигнал записи (вход 3i) че рез элементы 20 и 22 проходит на соответствующий выход формирователя 4 ; (выход 23). Этим сигналом адрес начального слова с щины 2 данных запи- сьшается в регистр адреса начального слова растровой строки (регистр 5) и остается зафиксированным на первом- выходе регистра 5. Таким же образом :происходит запись начальной строки в регистр адреса начальной растровой строки (регистра 5), запись осуществ ляется по выходу 24, адрес фиксирует ся на втором выходе регистра 5.

Предлагаемое устройство адресации работает в двух режимах: 1) формиро- вания адресов отображения; 2) формирования адресов от шины адресов.

В режиме формирования адресов отображения адрес видеопамяти является

10

20

30

Q .-

-

62407

суммой началъйого адреса отображения и адреса растра, определяюш 1Х место отображения, выбранного из видеопамяти информационного слова на экране растрового графического дисплея.

При работе с шиной адреса адрес ви- деопамяти получается путем суммирования начального адреса отображения и адрег са, поступающего от шины адресов.

При сравнении обоих режимов, видно,что при одинаковых адресах видеопамяти адрес растра всегда равен ад- - ресу от шины адресов. В результате 15 конкретному адресу шины 1 адреса соответствует конкретное место на экране графического дисплея -независимо от величины начального адреса отображения.

В предложенном устройстве изложен-, ный принцип реализован следующим образом.

Адресу растра соответствуют адрес слова растровой строки (выходы счет- 25 чика 10), который определяет порядко- вый номер отображения выбранного из видеопамяти информационного слова в растровой строке, и адрес растровой строки (выходы счетчика П), который определяет номер отображаемой растровой строки.

Каждый адрес на выходе 17 устройства определяет область в видеопамяти для хранения данных одной растровой строки отображения и меняется в пределах от О до (N-i). .Адрес на выходе 16 устройства меняется в пределах от О до (М-1) и определяют. М ячеек памяти, содержимое которых отображается в одной растровой строке,

В режиме формирования адресов отображения на вход 15 устройства пе-. риодически подаются импульсы переключения адресов отображения, которые последовательно увеличивают на единит; цу содержимое счетчика Ю адреса слова строки. Этот адрес с выхода счетчика 10 поступает на вход первого сумматора 7, где суммируется с адресом начального слова строки, поступающим с первого выхода регистра 5. Результат, который является физическим адресом ячейки видеопамяти в об-, ласти хранения информации одной растровой строки отображения, с выхода сумматора 7 поступает на первый вход второго мультиплексора 13. Сигнал коммутации адресов с входа 14 устройства подключают к выходам мультиплек35

45

50

сора 12 и 13 адреса с их первых входов, поэтому адрес с выхода первого сумматора 7 поступает н-а выход 16 мл&дших разрядов видеопамяти,

В начале отображения каледого кадр :содержимое счетчиков 10 и Г1 равно 0 Отображение начинается с ячейки ви- деопамяти, адрес которой записа;; з |регистр.е 5, Последоватально узеля- :чивая содержимое счетчике, 10, на зи- деопамять с выхода. 16 устройства подают последоватб льные адреса ячеек памяти, содержимое которых отображается в первой растроЕюй строке При этом циклически перебираются все М адресов в области младших разрядов видеопамяти (выход 16 устройства).

После формирования а.дреса последнего отображаемого информационного слова первой растровой строки (когда адрес слова растровой строки равен М-1), импульс с входа 15 устройства проходит на выход переноса счетчика 10 и увеличивает на единицу содержимое счетчика 11 адреса строки. После этого опять перебираются М адресов ячеек видеопамяти, содерясш-юе которых отображается во второй растровой строке, и т.д.

Адрес растровой строки (выход счетчика П) через первьй мультиппек сор. 12 проходит на вход второго сумматора 8, на вход которого поступает адрес начальной растровой строки со второго выхода регистра 5. .Каждый адрес на выходе с:,т матора 8 (выход 17 устройства) определяет г руп пу из М ячеек памяти,. Этот адрес во время отображения всей информации из видеопамяти цикли Jecки м:еняется с единичным шагом начиная с a,qpeca начальной растровой строки,

Во время работы дисплея периодиче ски необходимо засинхронизировать СЧЕТЧИКИ 10 и II с разверткой растра на экране отобр аженргя. С этой це,пью можно использовать в;адро1 ые синхроимпульсы для обнуления счетчиков 0 и 1I (реализация зависит от конкретного дисплея).

, Циклический сдвиг адресов на выходах 16 и 17 можно использовать для независимого панорам рсвания в горизонтальном и вертикальном направлениях.

При горизонтальном riaHOpaMHpoEia- нии необходимо перио,Ц1чески с едиггшч ным шагом увеличить или -yivseвыпить

Ь

5

0

5

0

5

0

5

адрес начального слова растровой строки (первый выход регистра 5). Для этого по шинам 1-3 производится цикл считывание-модификация-запись с дан- , ными в регистре начального слова растровой строки (регистра 5), для чего на пшне адреса выставляется адрес соответствующего регистра на шине 3 управления - сигнал считывания. При соответствии адреса разрешается работа дешифратора 22 блока 4, Сигнал считывания через дешифратор 22 проходит на первый Т равляюш11Й вход коммутатора 6 (выход 25). который подключает к шине 2 данных адрес с первого выхода регистра 5 начального адреса отображения. Устройство, утгравляющее работой д тсплея, считанный адрес изменяет на единиду, снимает сигнал 3 считывания, выставляет сигнал записи и записывает в регистр 5 новое значение адреса начального слова ра стровой строки. После этого отображение содержимого видеопамяти начинается с нового, сдвинутого на единицу, адреса начального слова растровой строки.

Меняя содер55аимое регистра адреса начальной растровой, строки (регистра 5)3 таким же образом организуют пано раг Шрова,ние в вертикальном направле- нрги. При этом сигнал Зд, считьшания по выходу 26 проходит на второй вход управлеьшя коммутатора 6. к шине 2 данных подключается адрес с второго вьгхода регистра 5, новый адрес начальной растровой строки записьшает- ся в регистр 5 сигналом на выходе 24.

Сдвиг по точкам внутри информационного слова при панорамировании в горизонтальном направлении должен обеспечиваться вне предлагаемого устройства адресации.

В режиме формирования адресов от шины адресов на вход устройства от шины поступает адрес ячейки видеопамяти в коор;щнатах экрана дисплея. Этот адрес делится на две части: L младших разрядов поступают на второй вход первого мультиплексора 12 К старших разрядов - на второй ВХ9Д третьего суж- атора 9.

Сигнгит коммутации адресов с входа 14 устройства переключает мультиплексоры 12,, 13 таким образом, что на их выходы проходят адреса с вторых вхо - дов. Тогда адрес через первый мультиплексор 12 проходит на второй вход

сумматора 8, в котором суммируется с адресом начальной растровой строки. Результат является адресом на выходе 17 устройства. Старшие разряды шины 1 адреса в третьем сумматоре 9 суммируются с адресом начального слова растровой строки. Результат этого суммирования является адресом, подаваемым через мультиплексор 13 на выход 16 устройства и далее на входы К младших разрядов видеопамяти. .

В режиме формирования адресов от шины адресов организована другая последовательность доступа к ячейкам видеопамяти, чем в режиме отображения, что достигается использованием младших разрядов шины I адреса для формирования старших разрядов адреса видеопамяти на выходе 17 устройства и старших разрядов шины 1 адреса для формирования младших разрядов адреса видеопамяти на выходе 16 устройства. В результате последовательными адресами с шины 1 адреса происходит обращение к ячейкам видеопамяти, соответствующим одному и тому же адресу слова (выход 16 устройства).После N циклов обращения адрес слова

25 ражения устройства, выходы первого сумматора подключены к информационным входам первой группы второго мультиплексора, выходы которого являются адресными выходами первой группы устувеличивается на единицу, потом опять 30 ройства, вьпсоды второй группы регистперебираются все N адресов на выходе 17 устройства и т.д. Такой порядок доступа позволяет для формирования в видеопамяти битового изображения вертикальных и наклонных диний ис- i; пользовать автоинкрементную или автодекрементную адресацию, что упрощает программы выполнения данной процедуры и увеличивает быстродействие по сравнению с другой последовательностью адресации. Время формирования растрового изображения горизонтальных линий при этом увеличивается, но время генерации всего изображения уменьшается, так как для генерации горизонтальной линии одинаковой длины с вертикальной необходимо в п раз меньше циклов записи видеопамяти (п - количество битов в шине 2 данных).

Таким образом, предлагаемое устройство адресации обеспечивает формирование адресов отображения для видеопамяти и благодаря преобразованию адреса щины 1 адреса, простоту адресации при обращении к видеопамяти с ши- gg ны адресов, Формула изобретения

Устройство дчя формирования адреса видеопамяти растрового графического

ра начального адреса подключены к информационным входам первой группы второго сумматора, выходы которого являются адресными выходами второй

35 группы устройства, информационные входы регистра начального адреса являются информационным входом устройства, информационные входы втйрой группы второго сумматора подключены к выхо40 дам первого мультиплексора, информационные входы первой группы которого соединены с выходами счетчика адреса строк, тактовый вход которого соединен с выходами переполнения счетчика

45 адреса слова, информационные входы второй группы первого мультиплексора соединены с адресными входами устройства, отличающееся тем, что, с целью повьшения быстродействия устройства, в него введены коммутатор, третий сумматор, информационгше входы первой группы которого соединены с выходами первой группы регистра начального адреса, а информационные входы второй группы - с адресными входами устройства, выходы третьего сумматора соединены с информационными входами второй группы второго мультиплексора,, управляющий вход ко50

дисплея, содержащее формирователь уп- равляюпщх сигналов, регистр начального адреса, первый и второй сум- маторы, счетчик адреса слова, счетчик адреса строки, первый и второй мультиплексоры, адресные входы формирователя управляюш тх сигналов являются адресньми входами устройства, а первый и второй управляющие

входы являются соответственно входа- ми управления записью считыванием устройства, первый и второй выходы формирователя управляющих сигналов

подключены соответственно к первому и второму управляющим входам регистра начального адреса, выходы первой группы которого подключены к информационным входам первой группы первого

сумматора, информационные входы второй группы которого соединены с выходами группы счетчика адреса слова, тактовый вход которого является входом сигнала переключения адресов отображения устройства, выходы первого сумматора подключены к информационным входам первой группы второго мультиплексора, выходы которого являются адресными выходами первой группы устройства, вьпсоды второй группы регистg

ра начального адреса подключены к информационным входам первой группы второго сумматора, выходы которого являются адресными выходами второй

5 группы устройства, информационные входы регистра начального адреса являются информационным входом устройства, информационные входы втйрой группы второго сумматора подключены к выхо0 дам первого мультиплексора, информационные входы первой группы которого соединены с выходами счетчика адреса строк, тактовый вход которого соединен с выходами переполнения счетчика

5 адреса слова, информационные входы второй группы первого мультиплексора соединены с адресными входами устройства, отличающееся тем, что, с целью повьшения быстродействия устройства, в него введены коммутатор, третий сумматор, информационгше входы первой группы которого соединены с выходами первой группы регистра начального адреса, а информационные входы второй группы - с адресными входами устройства, выходы третьего сумматора соединены с информационными входами второй группы второго мультиплексора,, управляющий вход ко0

торого и управляющий вход аервого мультиплексора йвляются входом сигна ла коммутации адресов устройства, информационные входы первой и второй групп коммутатора соединены с выходами первой и второй групп регистра на Чального адреса соответственно, перU62407 О

йый и управляюпме входы коммутатора соединены с третьим и четвертым вьгхода1 -ш формирователя управляю- щих сигналов, выходы коммутатора являются информадионными выходами устройства ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вывода графической информации | 1990 |

|

SU1833858A1 |

| Устройство для отображения радиолокационной информации на экране электронно-лучевой трубки | 1988 |

|

SU1509985A1 |

| Устройство для вывода графической информации | 1989 |

|

SU1698885A1 |

| Система ввода телевизионных изображений в ЭВМ | 1989 |

|

SU1665391A1 |

| Устройство для формирования адресов считывания видеопамяти для растрового графического дисплея | 1988 |

|

SU1603430A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1987 |

|

SU1522272A1 |

| Устройство для обработки и отображения видеоинформации | 1988 |

|

SU1748284A1 |

| Электронная вычислительная машина | 1988 |

|

SU1520533A1 |

| Устройство для формирования видеосигнала | 1990 |

|

SU1741124A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1991 |

|

SU1807516A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в растровых устройствах отображения графической информации. Цель изобретения - повышение быстродействия устройства - достигается введением коммутатора 6 и третьего с мматора 9 и соответсг вующих функциональных связей. Изобретение позволяет увеличить быстродействие устройства за счет преобразования адреса на входах устройства, и упрощения адресации при обращении к видеопамяти с шины адресов. В результате возможно изменение устройства в растровых устройствах отображения графической информации с возможностью панорамирования. 2 ил. (Л

&

АДР1

МЕ1

АДРЗ о

/ 1

AfiP{n-j) о

Фик.1

| Тилинин Д.А., Глазачев Н.К., Айсанов Р.Б | |||

| Русская печь | 1919 |

|

SU240A1 |

| Микропроцессорные средства и системы, 1986, № 4, с. | |||

| Патент США № 4491834, кл | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

Авторы

Даты

1989-02-28—Публикация

1987-07-27—Подача