23

Q

$S

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1985 |

|

SU1312557A1 |

| Устройство для управления вводом информации | 1988 |

|

SU1566337A1 |

| Преобразователь параллельного кода в последовательный | 1988 |

|

SU1587643A2 |

| Преобразователь последовательного кода в параллельный | 1983 |

|

SU1159164A1 |

| Устройство для ввода графичес-КОй иНфОРМАции | 1979 |

|

SU798916A1 |

| Устройство ввода-вывода информации | 1988 |

|

SU1619283A1 |

| Преобразователь последовательного кода в параллельный | 1986 |

|

SU1376244A1 |

| Устройство для сопряжения ЭВМ с абонентом по последовательному каналу связи | 1987 |

|

SU1442997A1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Преобразователь параллельного кода в последовательный | 1984 |

|

SU1243097A1 |

Изобретение относится к вычислительной технике, может быть использовано при построении преобразователей, входящих в состав аппаратуры сопряжения с двухпроводными каналами связи и обеспечивает сопряжение преобразователя как с полудуплевским двухпроводным каналом связи, так и со световодной системой передачи информации, чем достигается расширение области использования преобразователя. Преобразователь последовательного кода в параллельный содержит семь элементов И 1,2,3,4,15,16 и 17, три . триггера 5,6 и 14, четыре счетчика 7, 8,9 и 19, элемент ИЛИ 10, два элемента НЕ 11 и 18, генератор 12 импульсов и регистр 13 сдвига. 2 ил.

а

Ф

00 ел

N)

I Изобретение относится к вычисли- I тельной технике и может быть исполь- I эовано при построении преобразователей, входящих в состав аппаратуры сопряжения с двухпроводными каналами связи.

Целью изобретения является распш- рёние области применения преобразова теля за счет преобразования последовательности однополярных сигналов закодированных длительностью импуль- I сов.

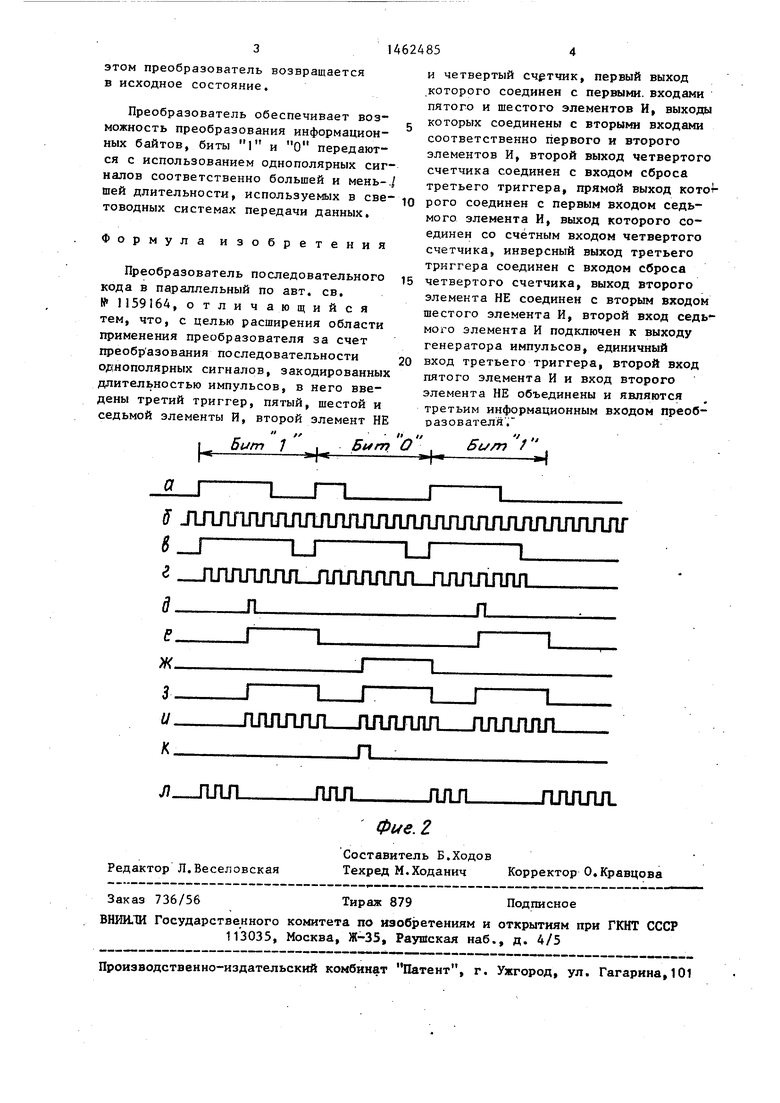

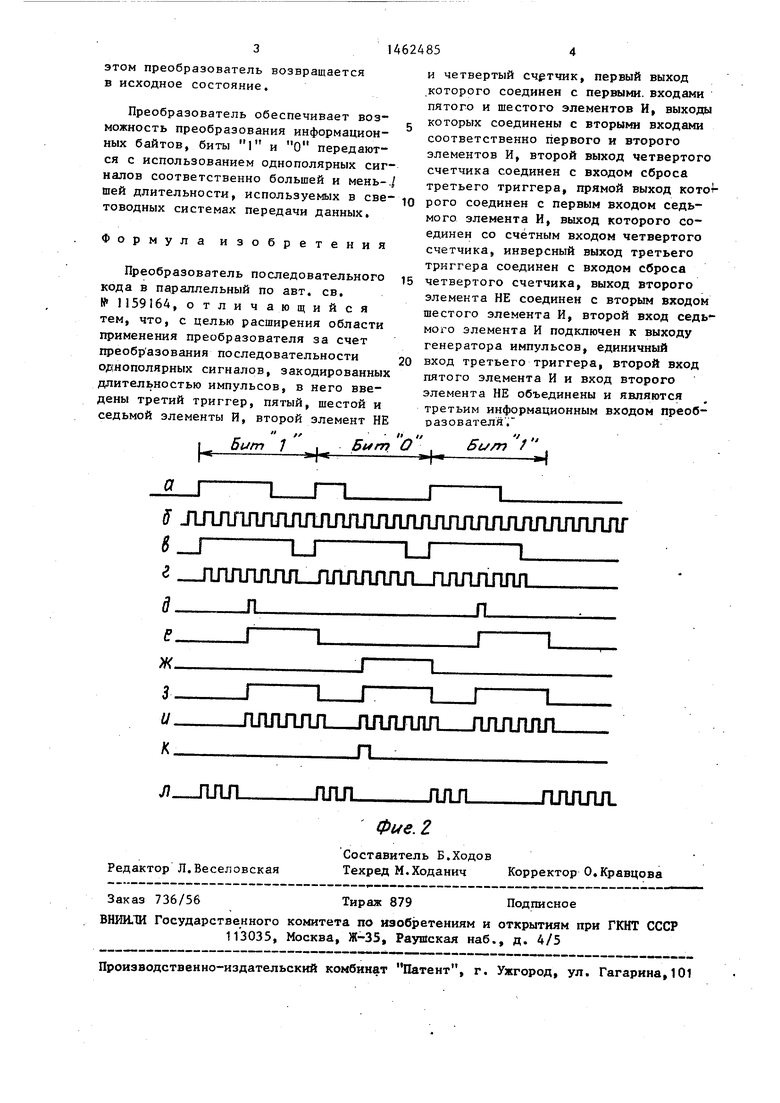

I На фиг.1 приведена блок-схема I преобразователя; на фиг,2 - временные диаграммы, поясняющие его работу.

Преобразователь содерзшт первый - ; четвертый элементы И 1 - 4, первый

5 и второй 6 триггеры, первый - тре- I тий счетчики 7-9, элемент ИЛИ 10, I первый элемент НЕ 1I, генератор 12 : импульсов, регистр 13 сдвига, третий триггер 14, пятый - седьмой элементы И 15 - 17, второй элемент НЕ 18 и четвертый счетчик 19.

На фиг.1 позициями 20, 21 и 22 обозначены соответственно первый - третий информационные входы преобразователя, позициями 23 и 24 - соот ветственно информационный выход и выход разрешения считывания преобразователя.

На входе 2 обозначены: а - сигнал :на входе 22; б - сигнал на выходе I генератора 12; в - сигнал нашрямом :выходе триггера 14; г - сигнал на выходе элемента И 17; д - сигнал на выходе третьего элемента И 15; е - сигнал на прямом выходе триггера 5; ж - сигнал на прямом выходе триггера 6; 3 - сигнал на выходе элемента ИЛИ 10; и,- сигнал на выходе элемента И 4; к - сигнал на выходе элемента И 16; л - сигнал на выходе элемента И 3.

Преобразователь последовательного кода в параллельный работает следующим образом.

В исходном состоянии сигналы с выхода генератора 12, поступают через элемент 3 на счетный вход счетчика В, а все остальные счетчики 7, 9 и 19 и все триггеры 5,6 и 14 находятся в состоянии О. Состояние ре- гистра1 13 может быть любым. Работа преобразователя заключается в преобразовавши последовательно поступающих на его вход 22 информационных

11-разрядных байтов в параллельный код и формировании сигнала сопровождения параллельного кода на выходе с счетчика 7.

Для передачи каждого бита необходимо время, равное Т. Информационные байты, следуют друг за другом через время t , 2Т.

10 При поступлении первого бита 1 информационного байта на вход 22 преобразователя устанавливается в состояние 1 триггер 14, в результате чего начинает работать счетчик 19.

15 Сигнал с первого счетчика 19 через элементы И 15 и 1 устанавливает в. состояние 1 триггер 5, после чего появляется сигнал на выходе элемента ИЛИ 10. Этот сигнал производит

20 сдвиг информации в регистре 13, изменяет состояние счетчика 7 на единицу, устанавливает счетчик 8 в состояние О и вызывает работу счетчика 9 под воздействием импульсов, посту

25 пающих на его счетный вход с выхода генератора 12 через элемент И 4. Триггер 14 возвращается в исходное состояние О при появлении сигнала на втором выходе счетчика 19, после 30 чего счетчик-19 также устанавливается в состояние О. При работе счетчика 9 появляется сигнал на его выходе для сброса триггеров 5 и 6, после чего прекращается сигнал на выходе элемен35 та 10, а сигнал с выхода элемента НЕ 11 производит сброс счетчика 9 и разрешает работу счетчика 8 до поступления следующего бита.

40 При поступлении на вход 22 преобразователя второго бита о работа триггера 14 и счетчика 19 повторяется однако сигнал с первого выхода счетчика 19, пройдя элементы И 16 и 2,

д5 устанавливает в состояние 1 триггер 6, при этом сигнал с выхода эле- мента ИЛЛ 10 производит те же действия, что и при поступлении на вход 22 преобразователя бита . При приеме

2Q последуюпщх битов работа преобразователя повторяется, однако в момент приема последнего одиннадцатого бита информационного байта на выходе счетчика 7 вырабатывается сигнал сопровож

5J дения информации, введенной в регистр 13. До поступления.на вход 22 преобразователя очередного информационного байта в результате работы счетчика 8 производится сброс счетчика 7, при

этом преобразователь возвращается в исходное состояние.

Преобразователь обеспечивает возможность преобразования информационных байтов, биты 1 и О передаются с использованием однополярных сигналов соответственно большей и мень-. шей длительности, используемых в све- товодных системах передачи данных.

Формула изобретения

Преобразователь последовательного кода в параллельный по авт. св. № 1159164, о т л и ч а ю щ и и с я тем, что, с целью расширения области применения преобразователя за счет преобр азования последовательности однополярных сигналов, закодированных длительностью импульсов, в него введены третий триггер, пятый, шестой и седьмой элементы И, второй элемент НЕ

-ПЛЛIlГlЛЛЛЛJ JLШШЛJLЛЛnГ

-JLJ -LJ1

-ПЛnлЛЛЛ ПЛЛЛJШЛUlЛЛ

дП

и четвертый счетчик, первый выход которого соединен с первыми, входами пятого и шестого элементов И, выходы 5 которых соединены с вторыми входами соответственно первого и второго элементов И, второй выход четвертого счетчика соединен с входом сброса третьего триггера, прямой выход котог

0 рого соединен с первым входом седьмого элемента И, выход которого соединен со счётным входом четвертого счетчика, инверсный выход третьего триггера соединен с входом сброса четвертого счетчика, выход второго элемента НЕ соединен с вторым входом шестого элемента И, второй вход седьмого элемента И подключен к выходу генератора импульсов, единичный

0 вход третьего триггера, второй вход пятого элемента И и вход второго элемента НЕ объединены и являются

третьим информационным входом преобразователя .

5

| 0 |

|

SU159164A1 | |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-02-28—Публикация

1986-12-08—Подача