сд

00

: Изобретение относится к 1зычисли- I тельной технике, может быть исполь- I човано при построении преобразовате лей, входящих в состав аппаратуры сопряжений с двухпроводным каналом связи, и является усовершенствованием преобразователя по авт. св. № 1243097.

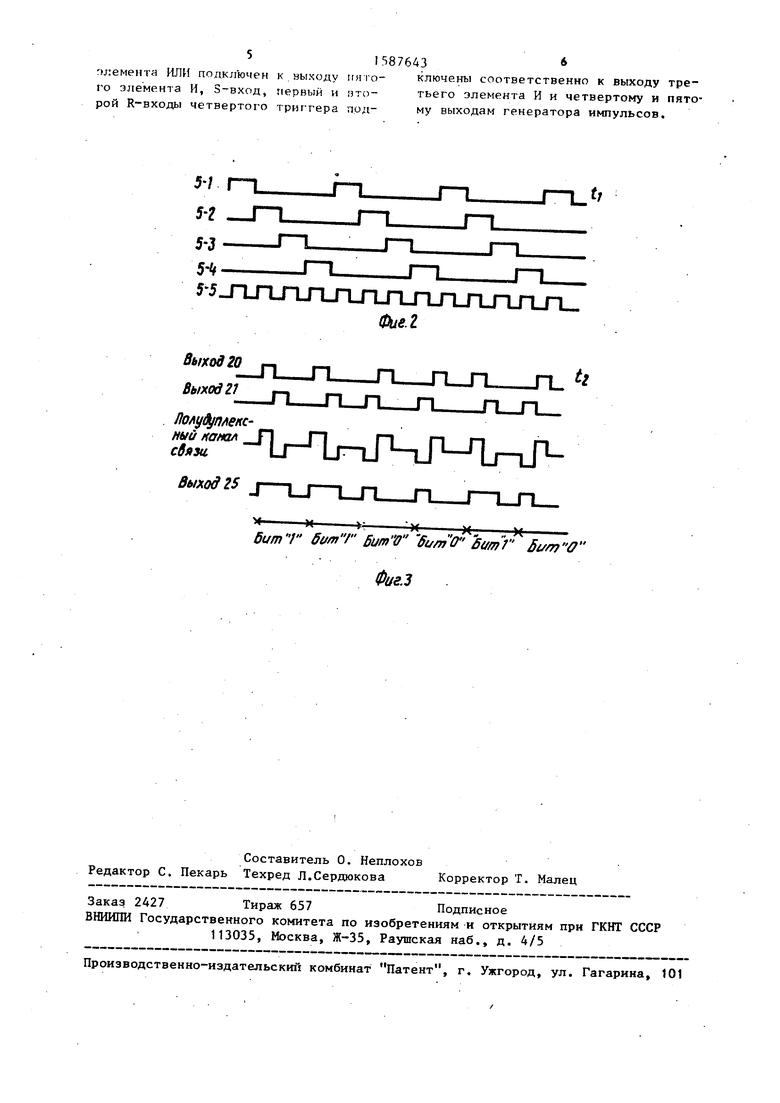

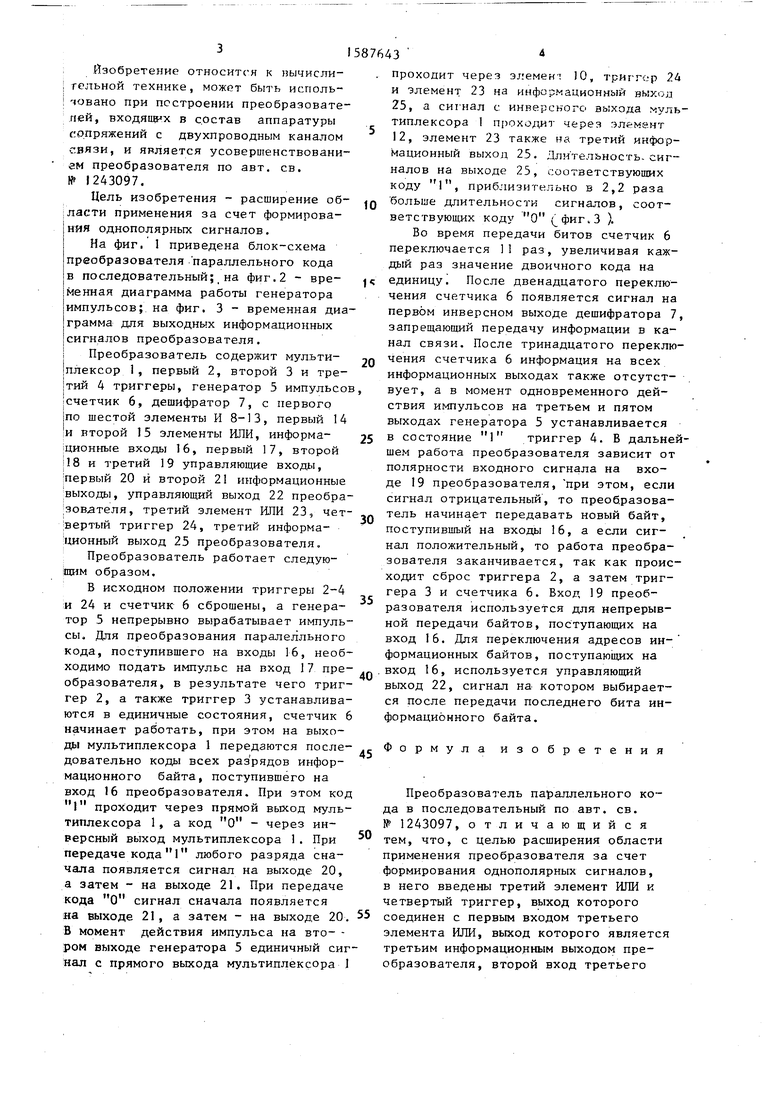

Цель изобретения - расширение об ;ласти применения за счет формирова- Iняя однополярных сигналов. I На фиг, 1 приведена блок-схема .преобразователя параллельного кода IB последовательный;, на фиг.2 - вре- |менная диаграмма работы генератора импульсов; на фиг. 3 - временная диаграмма для выходных информационных I сигналов преобразователя. I Преобразователь содержит мульти- |плексор 1, первый 2, второй 3 и тре- |тий 4 триггеры, генератор 5 импульсо |счетчик 6, дешифратор 7, с первого |по шестой элементы И 8-13, первый 14 :И второй 15 элементы ИЛИ, информа- |дионные входы 16, первый 17, второй и третий 19 управляющие вход1.1, |первый 20 и второй 21 информационные ;выходы, управляющий выход 22 преобра зовлтеля, третий элемент ИЛИ 23, чет ;вертый триггер 24, третий информационный выход 25 преобразователя.

Преобразователь работает следую- пщм образом.

В исходном положении триггеры 2-4 и 24 и счетчик 6 сброшены, а генератор 5 непрерывно вырабатывает импульсы. Для преобразования паралелльного кода, поступившего на входы 16, необходимо подать импульс на вход 17 преобразователя, в результате чего триггер 2, а также триггер 3 устанавливаются в единичные состояния, счетчик начинает работать, при этом на выходы мультиплексора 1 передаются после довательно коды всех раз рядов информационного байта, поступившего на вход 16 преобразователя. При этом ко

1 проходит через прямой выход мультиплексора 1, а код о - через инверсный выход мультиплексора 1. При передаче кода 1 любого разряда сначала появляется сигнал на выходе 20, а затем - на выходе 21. При передаче кода О сигнал сначала появляется яа выходе 21, а затем - на выходе 20 В момент действия импульса на вто- ром выходе генератора 5 единичный синал с прямого выхода мультиплексора

0

ч

с о

0

5

0

5

0

проходит через элемен-т 10, триггор 24 и элемент 23 на информационный выход 25, а сигнал с инверсного выхода мультиплексора I проходит через элемент 12, элемент 23 также на третий информационный выход 25, Длительность, сигналов на выходе 25, соответствующих коду 1, приблизительно в 2,2 раза больше длительности сигналов, соответствующих коду О ( фиг.З ).

Во время передачи битов счетчик 6 переключается 1 раз, увеличивая каждый раз значение двоичного кода на единицу. После двенадцатого переключения счетчика 6 появляется сигнал на первом инверсном выходе дешифратора 7, запрещаюпшй передачу информации в канал связи. После тринадцатого переключения счетчика 6 информация на всех информационных выходах также отсутствует, а в момент одновременного действия импульсов на третьем и пятом выходах генератора 5 устанавливается в состояние 1 триггер 4. В дальнейшем работа преобразователя зависит от полярности входного сигнала на входе 19 преобразователя, при этом, если сигнал отрицательный, то преобразователь начинает передавать новый байт, поступившый на входы 16, а если сигнал положительный, то работа преобразователя заканчивается, так как происходит сброс триггера 2, а затем триггера 3 и счетчика 6. Вход 19 преобразователя используется для непрерывной передачи байтов, поступающих на вход 16. Для переключения адресов информационных байтов, поступающих на вход 16, используется управляющий выход 22, сигнал на котором выбирается после передачи последнего бита информационного байта.

рмула изобретения

о

Преобразователь параллельного кода в последовательный по авт. св. № 1243097, отличающийся тем, что, с целью расширения области применения преобразователя за счет формирования однополярных сигналов, в него введены третий элемент ИЛИ и четвертый триггер, выход которого соединен с первым входом третьего элемента ИЛИ, выход которого является третьим информационным выходом преобразователя, второй вход третьего

15876436

г,:еменга ИЛИ подключенк выходу„иго- ключены соответственно к выходу трего злемента И, S-вход.первый ипго- тьего элемента И и четвертому и пяторои R-входь, четвертоготриггерапод- му выходам генератора импульсов

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь параллельного кода в последовательный | 1984 |

|

SU1243097A1 |

| Преобразователь последовательного кода в параллельный | 1986 |

|

SU1462485A2 |

| Устройство для управления вводом информации | 1988 |

|

SU1566337A1 |

| Преобразователь последовательного кода в параллельный | 1983 |

|

SU1159164A1 |

| Преобразователь последовательного кода в параллельный | 1986 |

|

SU1376244A1 |

| Устройство для ввода информации | 1985 |

|

SU1312557A1 |

| Устройство для приема и обработки информации | 1989 |

|

SU1603418A1 |

| Устройство для обмена данными | 1985 |

|

SU1297067A1 |

| Устройство для ввода графичес-КОй иНфОРМАции | 1979 |

|

SU798916A1 |

| Многоканальный преобразователь последовательного кода в параллельный | 1990 |

|

SU1751859A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении преобразователей, входящих в состав аппаратуры сопряжений с двухпроводным каналом связи. Цель изобретения - расширение области применения преобразователя за счет формирования однополярных сигналов. Преобразователь содержит мультиплексор 1, первый - третий 2 - 4 триггеры, генератор 5 импульсов, счетчик 6, дешифратор 7, первый - шестой 8 - 13 элементы И, первый 14, второй 15 элементы ИЛИ, информационные входы 16, первый - третий 17 - 19 управляющие входы, первый 20, второй 21 информационные выходы, управляющий выход 22 преобразователя, третий 23 элемент ИЛИ, четвертый 24 триггер, третий информационный выход 25 преобразователя. 3 ил.

Выход 20 Выход 2 J

Полудуплексный канал связи,

-Tj-nj-LP-LP-Tj-LTLВыход 25

бит-Г 6игп- О В1,, Фаг.З

| Преобразователь параллельного кода в последовательный | 1984 |

|

SU1243097A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-08-23—Публикация

1988-05-23—Подача