Изобретение относится к вычисли тельной технике и может быть исполь зовано при построении преобразователей, входящих в состав аппаратуры сопряжения цифровых устройств с полу- j дуплексными двухпроводными каналами связи.

Целью изобретения является расширение класса решаемых задач за счет обеспечения возможностипреобраэования о при различныхскоростях передачи . данных и при различных формах передаваемых сигналов.

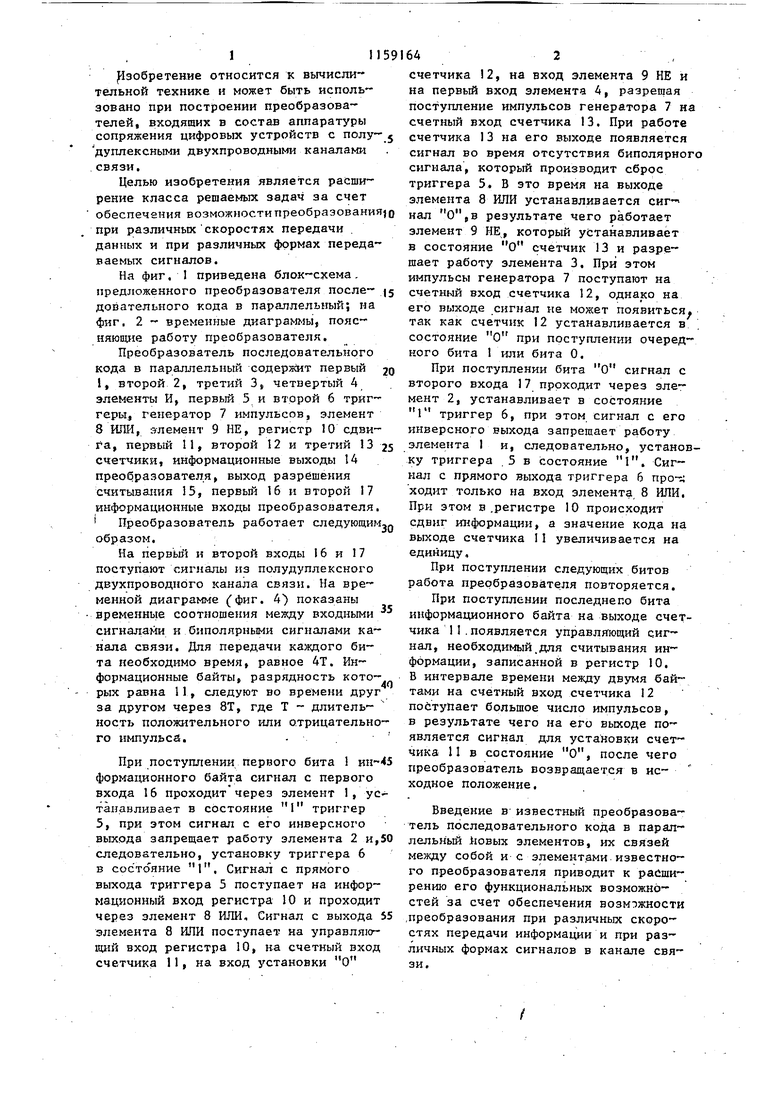

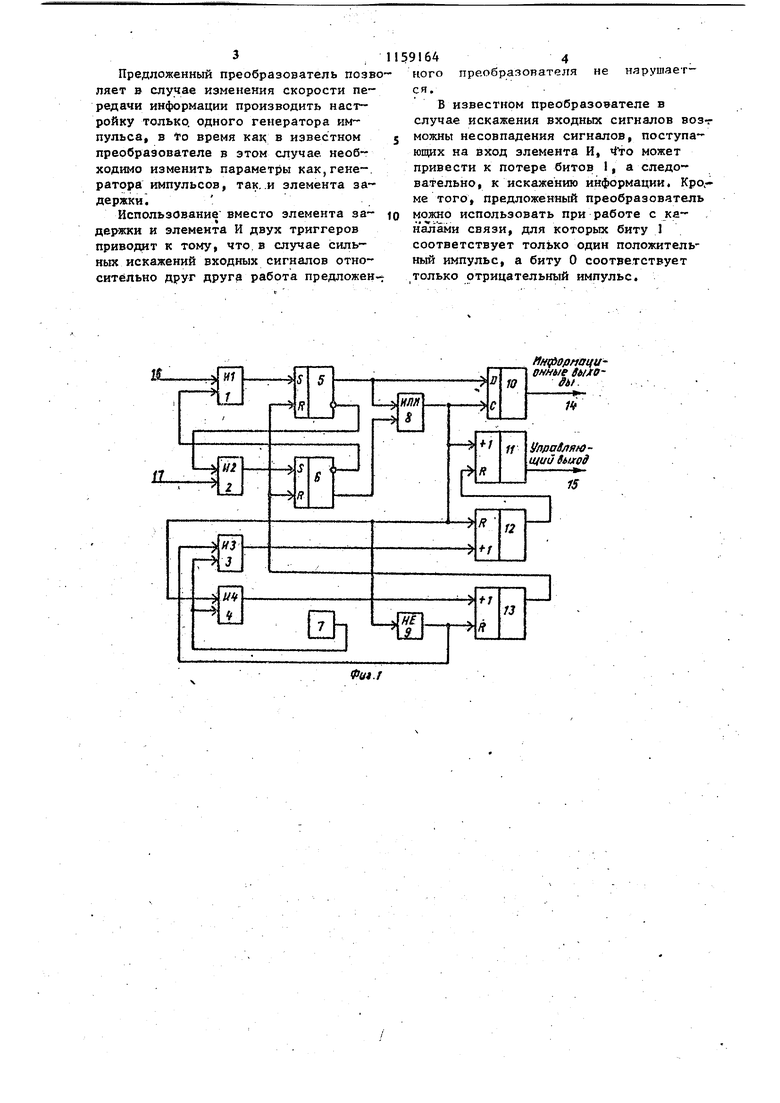

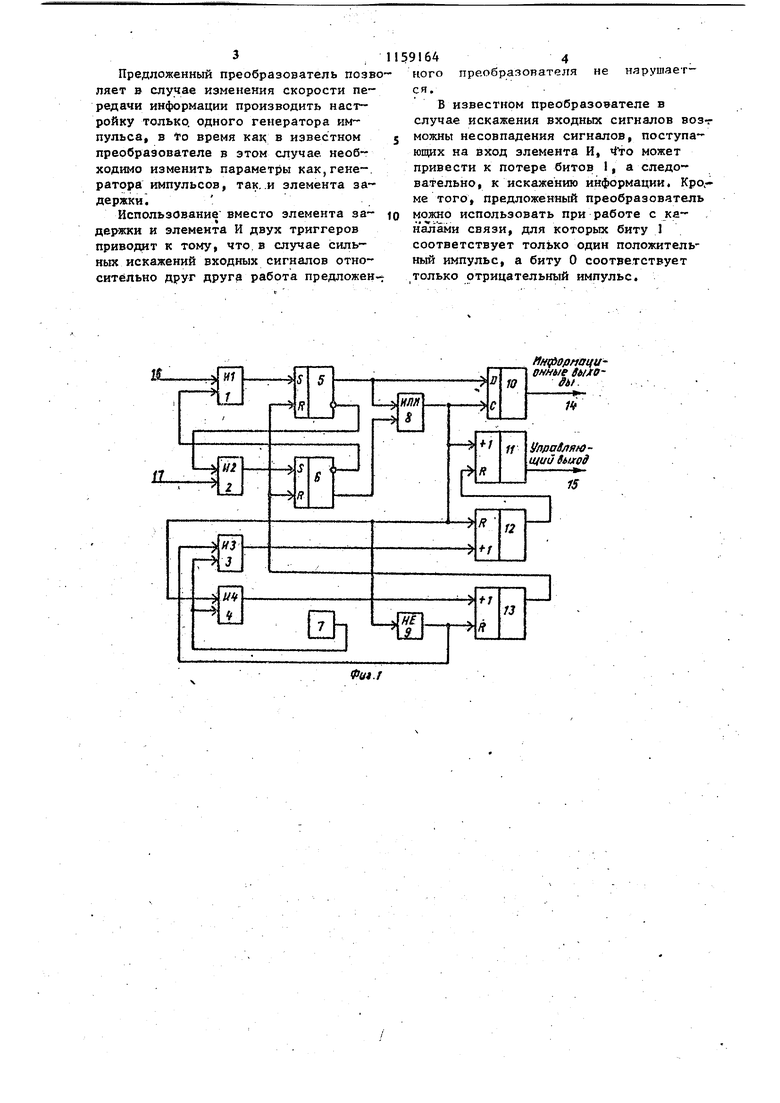

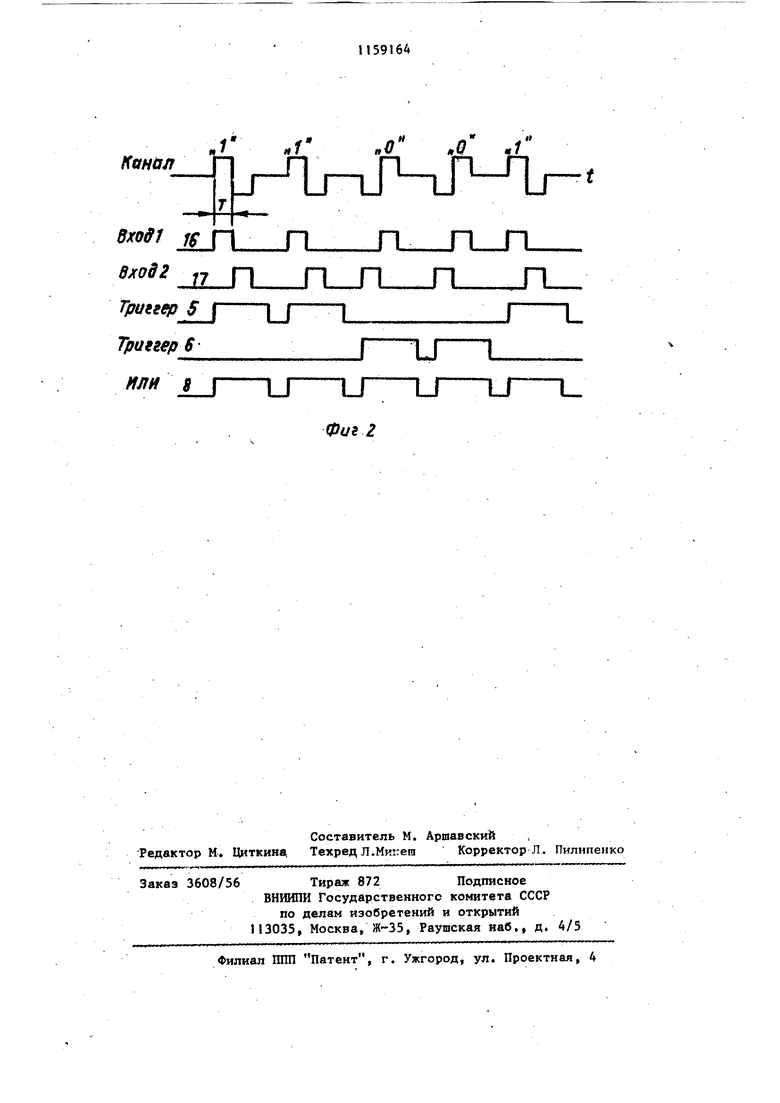

На фиг. I приведена блок-схема, предложенного преобразователя после- 15 довательного кода в параллельный; на фиг, 2 - временные диаграь.ы пояс- няюпше работу преобразователя.

Преобразователь последовательного кода в параллельный содерлйит первый 20 I, второй 2, третий 3, четвертый 4 элементы И, первый 5 и второй 6 триггеры, генератор 7 импульсов, элемент 8 ИЛИ, элемент 9 НЕ, регистр 10 сдвига, первый П, второй 12 и третий 13 75 счетчики, информационные выходы 14 преобразователя, выход разрешения считывания 15, первый 16 и второй 17 информационные входы преобразователя. Преобразователь работает следующим д образом.

На первый и второй входы 16 и 17 поступают сигналы из полудуплексного двухпроводного канала связи. На временной диаграмме фиг. 4) показаны временные соотношения между входными сигналами и биполярными сигналами канала связи. Для передачи каждого бита необходимо время, равное 4Т. Информационные байты, разрядность кото4

рых равна 11, следуют во времени друг за другом через 8Т, где Т - длительность положительного или отрицательного импульсй.

При поступлении первого бита 1 формационного байта сигнал с первого входа 16 проходит через элемент 1, устанавливает в состояние I триггер 5, при этом сигнал с его инверсного вькода запрещает работу элемента 2 и,50 следовательно, установку триггера 6 в состояние I. Сигнал с прямого выхода триггера 5 поступает на информационный вход регистра 10 и проходит через элемент 8 ИЛИ, Сигнал с выхода 55 элемента 8 ИЛИ поступает на управляюlUinl вход регистра 10, на счетный вход счетчика 11, на вход установки О

счетчика 2, на вход элемента 9 НЕ и на первый вход элемента 4, разрешая поступление импульсов генератора 7 н счетный вход счетчика 13. При работе счетчика 13 на его выходе появляется сигнал во время отсутствия биполярно сигнала, который производит сброс триггера 5. В это время на выходе элемента 8 ИЛИ устанавливается сигнал о,в результате чего работает элемент 9 НЕ, который устанавливает в состояние О счетчик 13 и разрешает работу элемента 3. При этом импульсы генератора 7 поступают на счетный вход счетчика 12, однако на его выходе сигнал не может появиться так как счетчик 12 устанавливается в состояние О при поступлении очередного бита 1 или бита 0.

При поступлении бита О сигнал с второго входа 17 проходит через элемент 2, устанавливает в состояние 1 триггер 6, при этом сигнал с его инверсного выхода запрещает работу элемента I и, следовательно, устаноку триггера .5 в состояние 1. Сигнал с прямого выхода триггера 6 про-т; ходит только на вход элемента, 8 ИЛИ. При этом в .регистре 10 происходит сдвиг информации, а значение кода на выходе счетчика 11 увеличивается на единицу.

При поступлении следующих битов работа преобразователя повторяется.

При поступлении последнего бита информационного байта на выходе счетчика П.появляется управляющий сигнал, необходимый.для считывания информации, записанной в регистр 10. В интервале времени между двумя байтами на счетный вход счетчика 12 поступает большое число импульсов, в результате чего на его выходе появляется сигнал для установки счетчика П в состояние О, после чего преобразователь возвращается в исходное положение.

Введение в известный преобразователь последовательного кода в параллельньй 11ОВЫХ элементов, их связей между собой и с элементами известного преобразователя приводит к расширению его функциональных возможностей за счет обеспечения возм:5жности .преобразования при различных скоростях передачи информации и при различных формах сигналов в канале связи. Предложенный преобразователь позв ляет в случае изменения скорости передачи информации производить настройку только, одного генератора импульса, в То время как в известном преобразователе в этом случае необ ходимо изменить параметры как,гене-. ратрра импульсов, так..и элемента задержки. Использование вместо элемента задержки и элемента И двух триггеров приводит к тому, что.в случае сильных искажений входных сигналов относительно друг друга работа предложен 1644 кого преобразонателя не нярушаетВ известном преобразователе в случае искажения входных сигналов возт можны несовпадения сигналов, поступающих на вход элемента И, fтo может привести к потере битов 1, а следовательно, к искажению информации. Кроме того, предложенный преобразователь можно использовать при работе с каналами связи, для которых биту 1 соответствует только один положительный импульс, а биту О соответствует только отрицательный импульс.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь последовательного кода в параллельный | 1986 |

|

SU1462485A2 |

| Преобразователь последовательного кода в параллельный | 1986 |

|

SU1376244A1 |

| Устройство для управления вводом информации | 1988 |

|

SU1566337A1 |

| Преобразователь параллельного кода в последовательный | 1984 |

|

SU1243097A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| Устройство для ввода информации | 1985 |

|

SU1312557A1 |

| Преобразователь последовательного кода переменной длины в параллельный | 1985 |

|

SU1290538A1 |

| ЭЛЕКТРОННАЯ РЕВЕРСИВНАЯ НАГРУЗКА | 1996 |

|

RU2109328C1 |

| ИМИТАТОР КАНАЛА | 1994 |

|

RU2079878C1 |

| Устройство для передачи информации | 1989 |

|

SU1700571A1 |

ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ, содержащий первый элемент И, генератор импульсов, регистр сдвига, первый и второй счетчики, выход второго счетчика соединен с входом сброса первого счетчика, выход которого является выходом, разрешения считьшания преобразователя, информационные выходы которого соединены с выходами регистра сдвига, отличающийся тем, что, с целью расшфения класса решаем.х задач засчет обеспечения возможности преобразования при различных скоростях передачи данных и при различных формах передаваемых сигналов, в него введены три элемента И, первый и второй триггеры, элемент ИЛИ, элемент НЕ и третий счетчик, выход которого соединен с входами сброса первого и второго триггера, единичные входы которых соединены с выходами первого и второго элементов И, первые входы которых соединены соответственгно с инверсными выходами второго и первого триггеров, единичные выходы которых соединены с входами элемента ИЛИ, выход которого соединен с син хровходами регистра сдвига, со счетным входом первого счетчика, с входом сброса второго счетчика и с первьм входом третьего элемента И, а через элемент НЕ - с входом сброса третьего счетчика и с первым входом четвертого элемента И, выход которого (О соединен со счетным входом счетчика, а второй вход соединен с выходом генератора импульсов и вторым входом третьего элемента И, выход которого соединен со счетным входом третьего счетчика, вьпсод первого триггера соединен с информационным входом регистра сдвига, вторые входы первого и второго элементов И соединены соответел ственно с информационными входами первого и второго каналов преобразователя. S 4

НнфорпациГ

f

Lr-nj-iP-LT-OjSxofff jg

n

У7 n n л n « JJ-TJ 1

Триггереr TJ

j LJ LT LJ

Фиг 2

Q. 4L

n

n

J

L.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Преобразователь последовательного кода в параллельный | 1980 |

|

SU924696A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для синхронизации координатных пультов ввода информации | 1982 |

|

SU1045238A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-05-30—Публикация

1983-12-21—Подача