Изобретение относится к электросвязи и может быть использовано для анализа состояния каналов связи, подверженных воздействию помех, приводящих к появлению ошибок группового характера с изменяющейся степенью группирования.

Известно устройство для контроля качества канала связи, содержащее реверсивный счетчик, на счетный вход которого подан сигнал ошибки, а вход вычитания соединен с выходом элемента ИЛИ. один из входов которого соединен с выходом делителя с переменным коэффициентом деления, на вход которого подан входной сигнал, другие входь элемента ИЛИ соединены с выходами блоков умножения.

Однако такое устройство ориентировано на каналы с независимыми ошибками и имеет невысокую точность контроля каналов связи с группированием ошибок.

Известно также устройство для контроля канала связи, которое обеспечивает повышение точности оценивания состояния канала связи с различной степенью группирования ошибок за счет введения элементов ИЛИ. счетчика проб, элементов совпадения, регистра сдвига и новых связей.

Однако эвристический выбор интервала пакетирования и коэффициентов множителей в этом устройстве, основанный на интуиции разработчика, не гарантирует требуемого качества оценивания степени группирования ошибок. Кроме того, устройство дает только две градации состояния канала - Авария и Норма, что недостаточно для эффективного управления процессом передачи информации по каналу.

Наиболее близким к предлагаемому является устройство для контроля канала связи, которое обеспечивает повышение

точности оценивания состояния канала связи с различной степенью группирования ошибок за счет введения элементов НЕ, второго реверсивного счетчика, второго регистра и новых связей.

В данном устройстве выделяется три степени группирования ошибок: низкая, средняя и высокая. Для оценивания степени группирования ошибок в канале вычисляют условную вероятность неискаженного приема блока при условии, что предыдущий блок принят с ошибками, и сравнивают полученную оценку с предварительно вычисленными пороговыми значениями. Условная вероятность неискаженного приема оценивается по результатам приема N блоков в соответствии с формулой

- Ч /

ро/1 Zr zr / 2/ «I

где XI - признак приема Ьго блока, принимающий значения О при неискаженном приеме, Г при искаженном приеме:

ZI - случайная величина, принимающая значение Г, если имеет место неискаженный прием при условии искаженного предыдущего приема, О - в противном случае.

Пороговые значения вероятности рф определяются по формуле ро/1 ,

где а- показатель группирования ошибок, который принимает значения от О до 1 и соответствует различным степеням группирования ошибок.

Полученная по результатам анализа N блоков оценка условной вероятности po/i сравнивается с предварительно вычисленными по формуле (2) значениями, соответствующими трем выбранным степеням группирования, и принимается решение о степени группирования ошибок в канале.

Недостатком известного устройства является невысокая точность оценивания, обусловленная следующими обстоятельствами.

Дляполучения высокой точности оценивания необходим большой объем контролируемой выборки N. Величина N равна разрядности сдвиговых регистров, что приг водит к большим аппаратурным затратам при их реализации. Поэтому область применения устройства ограничивается малым обьемом выборки N, что не обеспечивает достаточную точность оценивания состояния канала связи.

Цель изобретения - повышение точности контроля качества канала связи с изменяющейся степенью группирования ошибок.

Поставленная цель достигается тем, что в устройство контроля качества канала связи, содержащее последовательно соединённые первый реверсивный счетчик, первый

делитель и дешифратор, второй реверсивный счетчик, выход которого подключен к второму входу первого делителя, последовательно соединенные элемент НЕ и триггер и последовательно соединенные второй

0 делитель и первый элемент И, инверсный выход и второй вход которого соединены соответственно с входом сброса триггера и с выходом элемента НЕ, вход которого является входом сигнала ошибки устройства

5 для контроля качества канала связи, тактовым входом и выходами которого являются соответственно вход второго делителя и соответствующие выходы дешифратора, введены одновибратор, блок управления,

0 второй, третий, четвертый и пятый элементы И, первый и второй блоки памяти и первый и второй адресные счетчики. Выход второго делителя подключен к входам первого и второго адресных счетчиков и блока управления, первый выход которого подключен к входам разрешения записи первого и второго блоков памяти и к первым входам второго и четвертого элементов И, выходы которых подключены к входам сложения соответственно первого и второго реверсивных счетчиков. Второй выход блока управления подключен к входам разрешения считывания первого и второго блоков памяти и к первым входам третьего и пятого

5 элементов И, выходы которых подключены к входам вычитания соответственно первого и второго реверсивных счетчиков. Выход первого адресного счетчика подключен к адресному входу первого блока памяти, информационный вход и выход которого соединены соответственно с входом элемента НЕ и с вторыми входами второго и третьего элементов И, а выход второго адресного счетчика подключен к адресному

5 входу второго блока памяти, выход и информационный вход которого соединены соответственно с вторыми входами четвертого и пятого элементов И и с выходом одновибратора, вход которого соединен с выходом

0 триггера.

Обеспечение повышения точности оценки состояния канала с изменяющейся степенью группирования ошибок достигается введением двух блоков памяти, двух

5 адресных счетчиков, четырех элементов И, одновибратора. устройства управления и новых связей.

Повышение точности контроля качества канала связи с изменяющейся степенью группирования ошибок обусловлено тем,

что в предлагаемом устройстве исключены применяемые в известном устройстве многоразрядные (N-разрядные) сдвиговые регистры, а используемые счетчики имеют разрядность logaN «N, что позволяет при равных аппаратурных затратах получить больший объем контролируемой выборки, а значит повысить точность контроля.

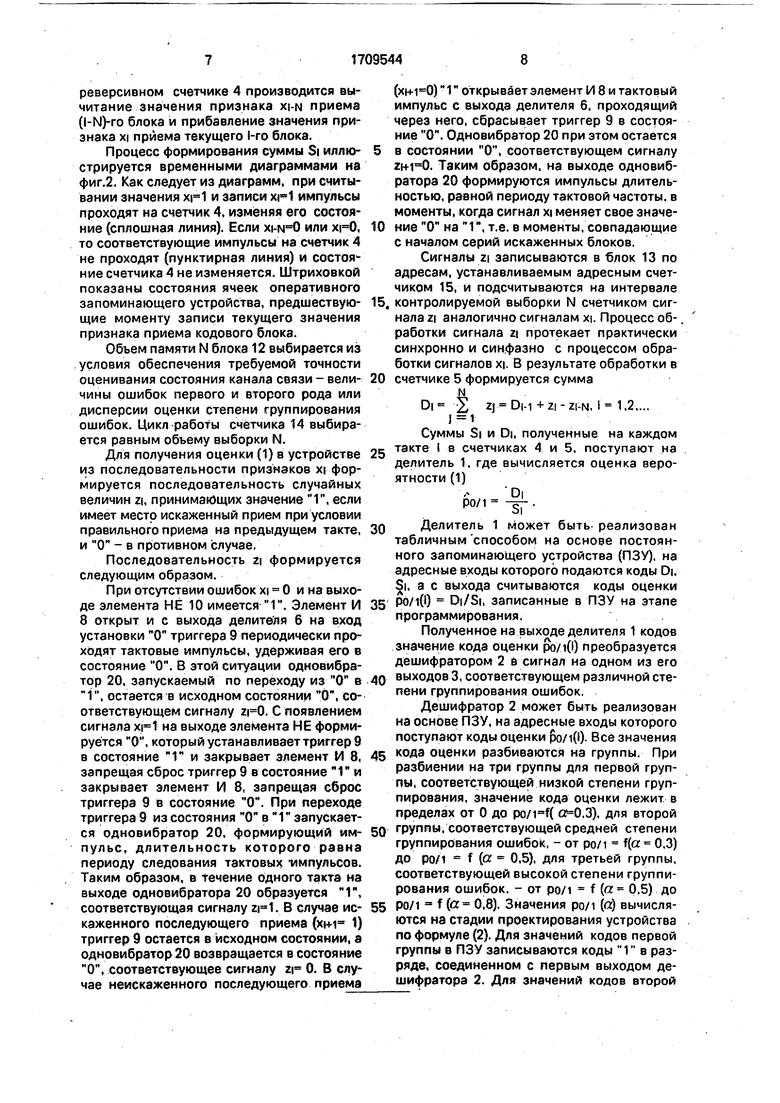

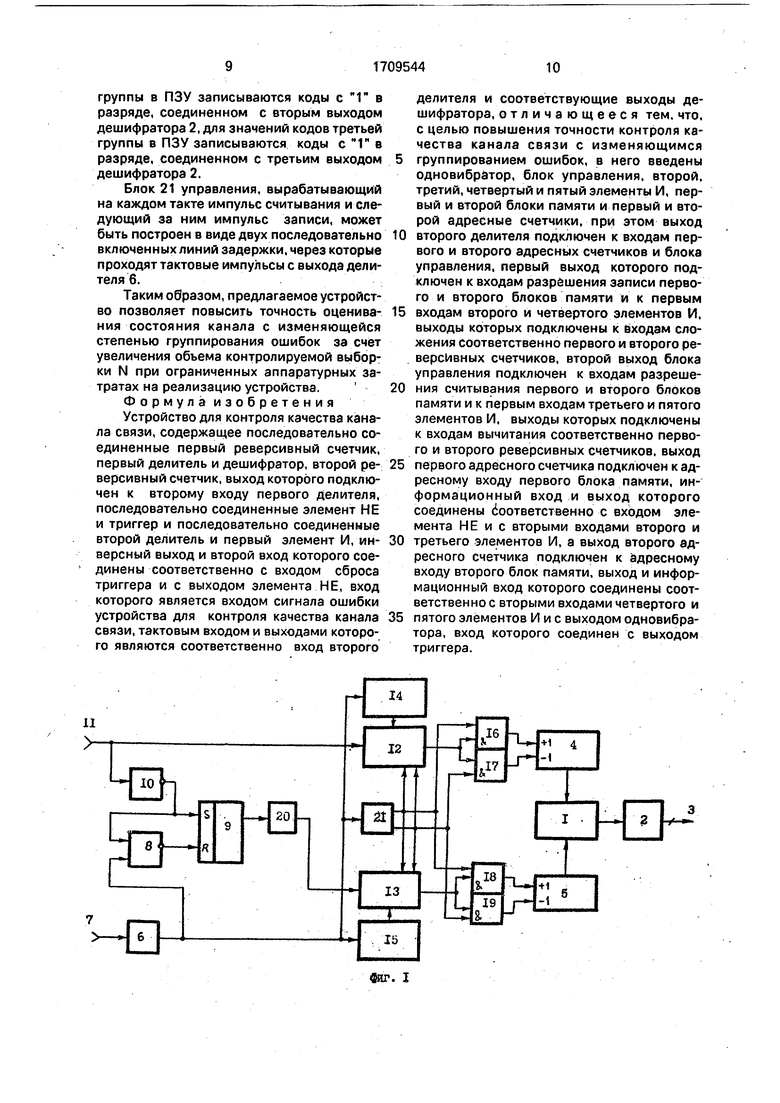

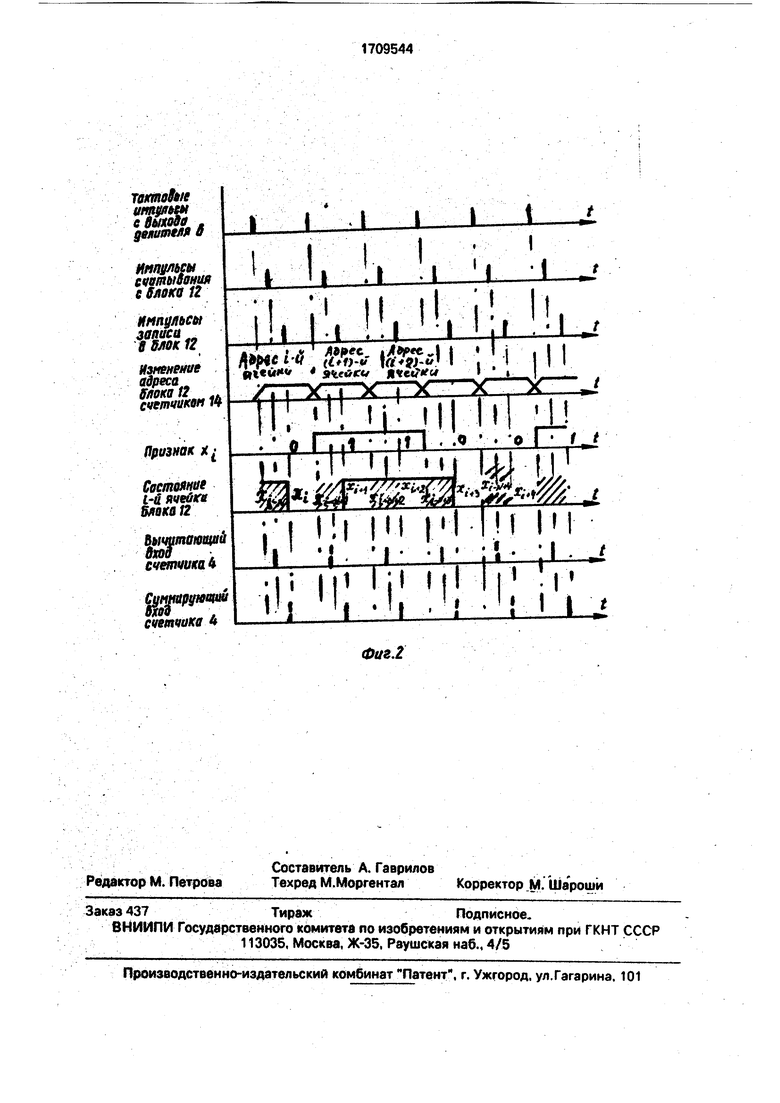

На фиг. 1 представлена структурная схема предлагаемого устройства; на фиг.2 - временные диаграммы, иллюстрирующие его работу.

Устройство для контроля качества канала связи содержит последовательно соединенные первый делитель 1 и дешифратор 2, выходы 3 которого являются выходами устройства, первый 4 и второй 5 реверсивные счетчики, соединенные соответственно с первым и вторым входами первого делители 1, второй делитель 6, вход которого подключен к входу 7 Тактовая частота, а выход соединен с первым входом первЬго элемента И 8, выход которого соединен с входом установки О триггера 9, а второй вход подключен к входу установки 1 триггера 9 и выходу элемента НЕ 10, вход которого является входом 11 Ошибка устройства, а также первый 12 и второй 13 блоки памяти, первый 14 и второй 15 адресные счетчики, второй - пятый элементы И 16 - 19, одновибратор 20, а также блок 21 управления. Информационный вход первого блока 12 памяти соединен с входом 11 Ошибка устройства, а информационный вход второго блока 13 памяти подключен к.выходу одновибратора 20, соединенного своим входом с выходом триггера 9. Адресною входы первого 12 и второго 13 блоков памяти соединены соответственно с выходами первого 14 и второго 15 адресных счетчиков,, счетные входы которых соединены с выходом второго делителя 6 и входом блока 21 управления, первый выход которого соединен с входами записи блоков 12 и 13 памяти и первыми входами второго элемента И 16 и четвертого элемента И 18, а второй выходс входами считывания блоков 12 и 13 памяти и первым входами третьего элемента И 17 и пятого элемента И 19. Выход первого блока 12 памяти подключен через второй вход второго элемента И 16 к суммирующему входу-первогр реверсивного счетчика 4, а через второй вход третьего элемента И 17-к вычитающему входу этого счетчика. Выход второго блока 13 памяти подключен через четвертый элемент И 18 к суммирующему входу второго реверсивного счетчика 5, а через второй вход пятого элемента И 19 - к вычитающему входу этого счетчика. ;

Устройство для контроля качества канала связи работает следующим образом.

В исходном состоянии счетчики 4, 5, 14 и 15, блоки 12 и 13 памяти и триггер 9 обнулены. Процесс контроля состояния канала связи сводится к вычислению оценки (1), получаемой на выходе делителя 1, и сравнению этой оценки с пороговыми значениями (2), осуществляемыми дешифратором 2.

С выхода блока обнаружения ошибок (не показан) на вход 11 Ошибка поступают XI искаженного;, и правильного приема кодовых блоков в виде последовательности 1 и О, которые подаются на

информационный вход первого блока 12 па-, мяти емкостью в N слов по 1 биту каждое, где N - объем контролируемой выборки или длина выборки. Одновременно с поступлением признаков XI на суммирующий вход

адресного счетчика 14 с выхода делителя 6 поступают тактовые импульсы, период поступления которых равен периоду следования признаков XI, совпадающему с периодом следования кодовых блоков. Очередной тактовый импульс устанавливает на выходах счетчика 14 код адреса, по которому импульсом считывания с второго выхода блока 21 управления считывается признак X(.N. записанный по этому же адресу на (i-N)-M такте

(при KN считывается значение , установленное в начале работы устройства).

После считывания на вход записи блока 12 с первого выхода устройства 21 управления поступает импуйьс записи, который

производит запись признака х) по этому адресу на место считанного признака XI-N. Считанный из блока 12 признак хж поступает через схему совпадения И 17, открытую в момент действия импульса считывания с

второго выхода блока 21 управления, на вычитающий вход реверсивного счетчика 4. Записываемый в оперативное запоминающее устройство признак xi поступает через элемент И 16, открытый в момент действия

импульса записи с п«рвого выхода устройства 21 управления, на суммирующий вход счетчика 4. По истечении п тактов с начала работы устройства в блоке 12 запоминается последовательность признаков, характеризующих прием последних N кодовых блоков, а в счетчике 4 образуется код, числовое

значение которого равно сумме

XJ и

j - 1

формируется в соответствии с выражением

Si Si-i + Xi-xi-N, i t,2,...

Таким образом, в оперативном запоминающем устройстве 12 хранятся признаки приема последних N кодовых блоков, а в

реверсивном счетчике 4 производится вычитание значения признака XI-N приема (l-N)-ro блока и прибавление значения признака XI приема текущего 1-го блока.

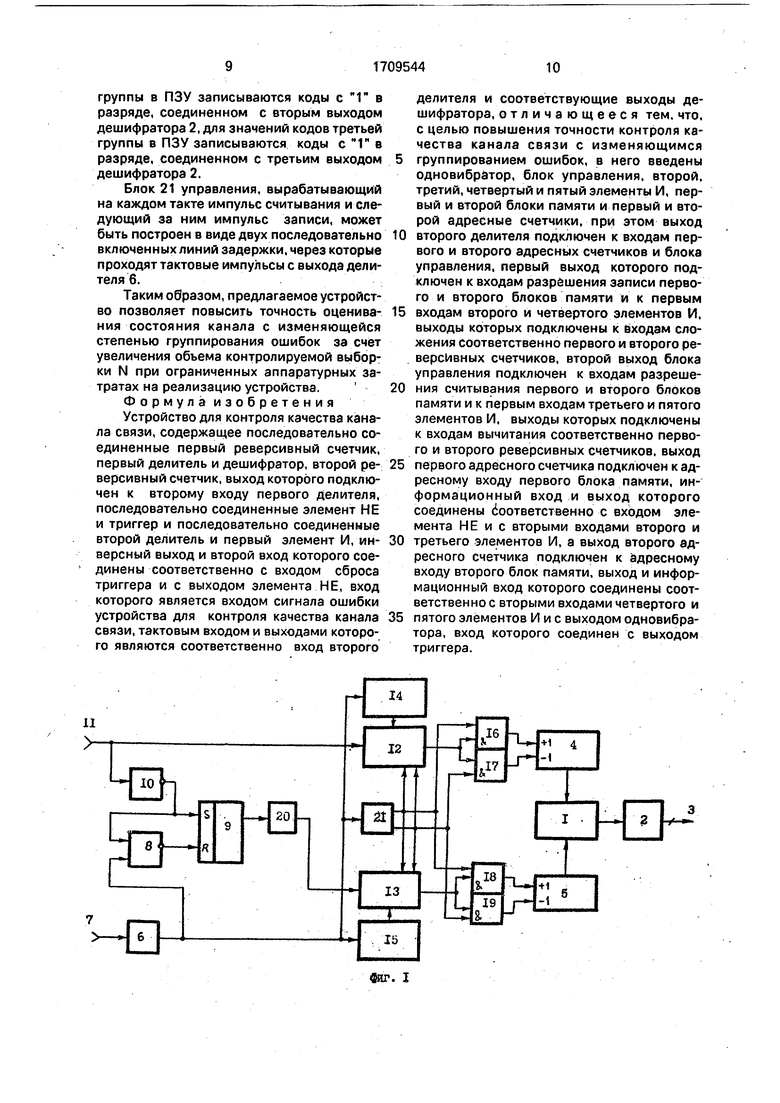

Процесс формирования суммы Si иллюстрируется временными диаграммами на фиг.2. Как следует из диаграмм, при считывании значения и записи х)1 импульсы проходят на счетчик 4. изменяя его состояние (сплошная линия). Если xi-№0 или , то соответствующие импульсы на счетчик 4 не проходят (пунктирная линия) и состояние счетчика 4 не изменяется. Штриховкой показаны состояния ячеек оперативного запоминающего устройства, предшествующие моменту записи текущего значения признака приема кодового блока.

Объем памяти N блока 12 выбирается из условия обеспечения требуемой точности оценивания состояния канала связи - величины ошибок первого и второго рода или дисперсии оценки степени группирования ошибок. Цикл работы счётчика 14 выбирается равным объему выборки N.

Для получения оценки (1) в устройстве из последовательности признаков xi формируется последовательность случайных величин ZI, принимающих значение 1, если имеет место искаженный прием при условии правильного приема на предыдущем такте, и О - в противном случае.

Последовательность zi формируется следующим образом.

При отсутствии ошибок XI О и на выходе злемента НЕ 10 имеется 1. Элемент И 8 открыт и с выхода делитейя 6 на вход установки О триггера 9 периодически проходят тактовые импульсы, удерживая его в состояние О. В зтой ситуации одновибратор 20, запускаемый по переходу из О в 1. остается в исходном состоянии О, соответствующем сигналу . С появлением сигнала на выходе злемента НЕ формируется О, который устанавливает триггер 9 в состояние Г и закрывает элемент И 8, запрещая сброс триггер 9 в состояние Г и закрывает злемент И 8, запрещая сброс триггера 9 в состояние О. При переходе триггера 9 из состояния О в 1 запускается одновибратор 20, формирующий импульс, длительность которого равна периоду следования тактовых импульсов. Таким образом, в течение бдного такта на выходе одновибратора 20 образуется Т, соответствующая сигналу . В случае искаженного последующего приема (хи-1° 1) триггер 9 остается в исходном состоянии, а одновибратор 20 возвращается в состояние О, соответствующее сигналу zi 0. В случае неискаженного последующего приема

() 1 открывает элемент И 8 и тактовый импульс с выхода делителя б, проходящий через него, сбрасывает триггер 9 в состояние О. Одновибратор 20 при зтом остается

в состоянии О, соответствующем сигналу ZH-i°0. Таким образом, на выходе одновибратора 20 формируются импульсы длительностью, равной периоду тактовой частоты, в моменты, когда сигнал xi меняет свое значение О на 1, т.е. в моменты, совпадающие с началом серий искаженных блоков.

Сигналы ZI записываются в лок 13 по адресам, устанавливаемым адресным счетчиком 15, и подсчитываются на интервале

контролируемой выборки N счетчиком сигнала ZI аналогично сигналам xi. Процесс об-. работки сигнала zi протекает практически синхронно и синфазно с процессом обработки сигналов XI. В результате обработки в

счетчике 5 формируется сумма

DI

ZJ DM + Z1 - ZI-N, 1 1.2....

1

Суммы Si и DI, полученные на каждом такте i в счетчиках 4 и 5, поступают на делитель 1, где вычисляется оценка вероятности (1)

DI

РО/1

Si

Делитель 1 может быть- реализован абличным способом на основе постоянного запоминающего устройства (ПЗУ), на адресные входы которого подаются коды Di. Si, а с выхода считываются коды оценки

Po/i(0 PI/SI, записанные в ПЗУ на зтапе программирования..

Полученное на выходе делителя 1 кодов значение кода оценки ро/() преобразуется дешифратором 2 6 сигнал на одном из его

выходов 3, соответствующем различной степени группирования ошибок.

Дешифратор 2 может быть реализован на основе ПЗУ, на адресные входы которого поступают коды оценки po/i(0- Все значения

кода оценки разбиваются на группы. При разбиении на три группы для первой группы, соответствующей низкой степени группирования, значение кода оценки лежит в пределах от О до ( .3), для второй

группы, соответствующей средней степени группирования ошибок, - от po/i f(ct 0.3) до ро/1 f (а 0,5), для третьей группы, соответствующей высокой степени группирования ошибок. - от ро/1 f (« 0.5) до

ро/1 f (lor 0,8). Значения po/i {«) вычисляются на стадии проектирования устройства по формуле (2). Для значений кодов первой группы в ПЗУ записываются коды 1 в разряде, соединенном с первым выходом дешифратора 2. Для значений кодов второй

группы в ПЗУ записываются коды с Г в разряде, соединенном с вторым выходом дешифратора 2, для значений кодов третьей группы в ПЗУ записываются коды с Г в разряде, соединенном с третьим выходом дешифратора 2.

Блок 21 управления, вырабатывающий на каждом такте импульс считывания и следующий за ним импульс записи, может быть построен в виде двух последовательно включенных линий задержки, через которые проходят тактовые импульсы с выхода делителя б.

Таким образом, предлагаемое устройство позволяет повысить точность оценивания состояния канала с изменяющейся степенью группирования ошибок за счёт увеличения объема контролируемой выборки N при ограниченных аппаратурных затратах на реализацию устройства.

Формула из обре тения

Устройство для контроля качества канала связи, содержащее последовательно соединенные первый реверсивный счетчик, первый делитель и дешифратор, второй реверсивный счетчик, выход которого подключен к второму входу первого Делителя, последовательно соединенные элемент НЕ и триггер и последовательно соединенные второй делитель и первый элемент И, инверсный выход и второй вход которого соединены соответственно с входом сброса триггера и с выходом элемента НЕ, вход которого является входом сигнала ошибки устройства для контроля качества канала связи, тактовым входом и выходами которого являются соответственно вход второго

делителя и соответствующие выходы дешифратора, отличающееся тем. что, с целью повышения точности контроля качества канала связи с изменяющимся группированием ошибок, в него введены одновибрдтор, блок управления, второй, третий, четвертый и пятый элементы И, первый и второй блоки памяти и первый и второй адресные счетчики, при этом выход второго делителя подключен к входам первого и второго адресных счетчиков и блока управления, первый выход которого подключен к входам разрешения записи первого и второго блоков памяти и к первым входам второго и четвертого элементов И, выходы которых подключены к входам сложения соответственно первого и второго реверсивных счетчиков, второй выход блока управления подключен к входам разрешения считывания первого и второго блоков памяти и к первым входам третьего и пятого элементов И, выходы которых подключены к входам вычитания соответственно первого и второго реверсивных счетчиков, выход первого адресного счетчика подключен к адресному входу первого блока памяти, информационный вход и выход которого соединены Соответственно с входом элемента НЕ и с вторыми входами второго и третьего элементов И, а выход второго адресного счетчика подключен к адресному входу второго блок памяти, выход и информационный вход которого соединены соответственное вторыми входами четвертого и пятого элементов И и с выходом одновибратора, вход которого соединен с выходом триггера. TeKinofM unuiffbW e выхтв ffnaffflKu еуатываная sSaaxan ннпдлъси запаса 8 SMK12 Изненетге адреса KSA i Признак x СветоячаеL-й aveuifu S/ioKa 12 Ъьттвюща ev&nwxa 4 cvemWKa

Фиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля качества канала связи | 1990 |

|

SU1716610A2 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА КАНАЛА СВЯЗИ | 1991 |

|

RU2050693C1 |

| Устройство для контроля качества канала связи | 1990 |

|

SU1830186A3 |

| Устройство контроля дискретных каналов | 1989 |

|

SU1707770A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА КАНАЛА СВЯЗИ | 2002 |

|

RU2216865C1 |

| Устройство контроля дискретных каналов | 1989 |

|

SU1626406A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1987 |

|

SU1462492A1 |

| Устройство передачи и приема шумоподобных сигналов | 1989 |

|

SU1707771A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1596464A1 |

| Устройство для контроля качества канала связи | 1979 |

|

SU856023A1 |

Изобретение относится к электросвязи. Цель изобретения - повышение точностиконтроля качества канала связи с изменяющимся группированием ошибок. Устройство содержит два делителя, дешифратор, дв'а реверсивных счетчика, элемент НЕ, триггер, пять элементов И, два блока памяти, два адресных счетчика/одновибратор. блок управления. Оценка состояния канала ведется путем вычисления условной вероятности неискаженного приема кодового блока. Увеличение объема выборки способствует повышению точности индентифика- ции степени группирования ошибок в канале связи. 2 ил.

| Авторское свидетельство СССР N! 1592949 | |||

| кл | |||

| кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Механизм для сообщения поршню рабочего цилиндра возвратно-поступательного движения | 1918 |

|

SU1989A1 |

Авторы

Даты

1992-01-30—Публикация

1990-07-02—Подача