Изобретение касается электросвязи и может быть использовано при построении аппаратуры передачи данных, в которой для обеспечения требуемой верности передачи применяют избыточный код в режиме обна - ружения ошибок с непрерывной последовательной передачей кодовых комбинаций и решающей обратной связью (РОС) при работе на каналах низкого качества, характеризующихся изменением параметров в широких пределах,

Цель изобретения - повышение достоверности приема.

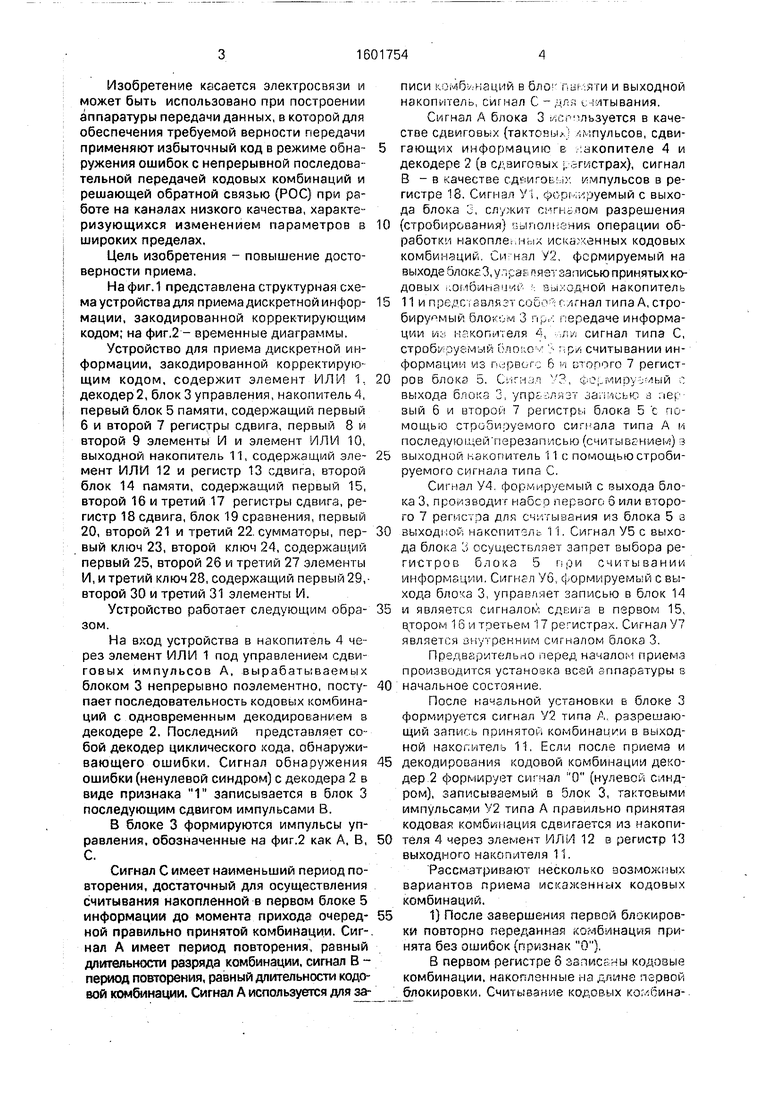

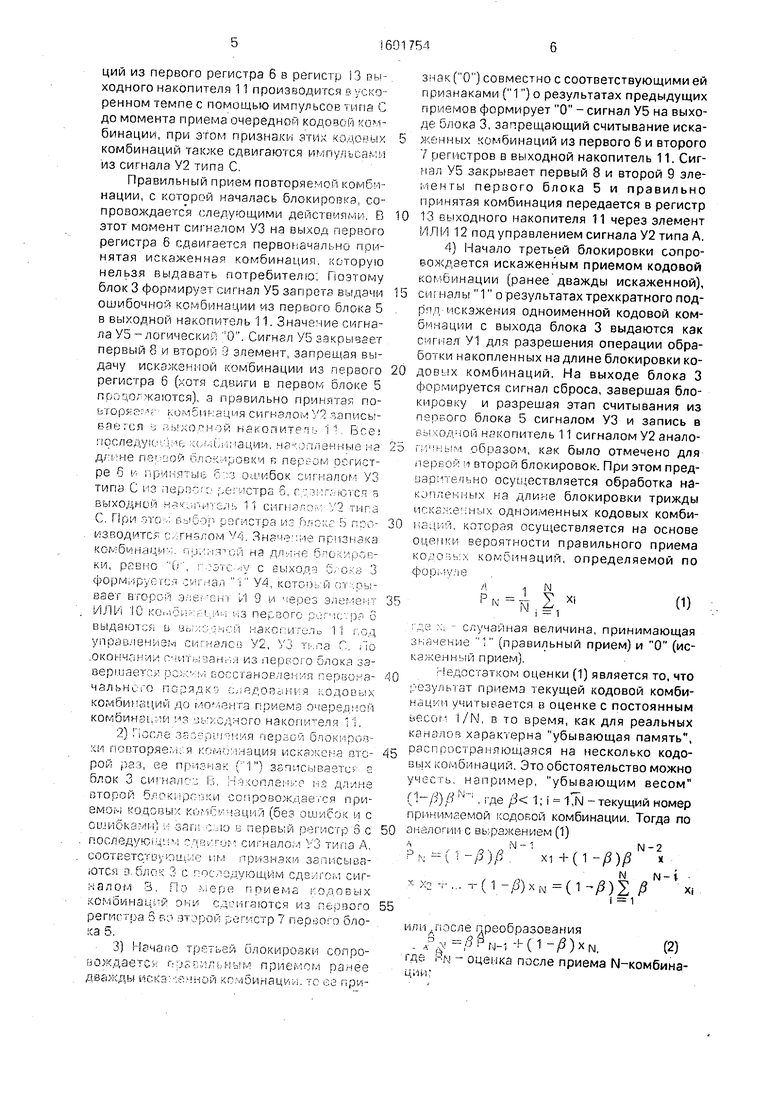

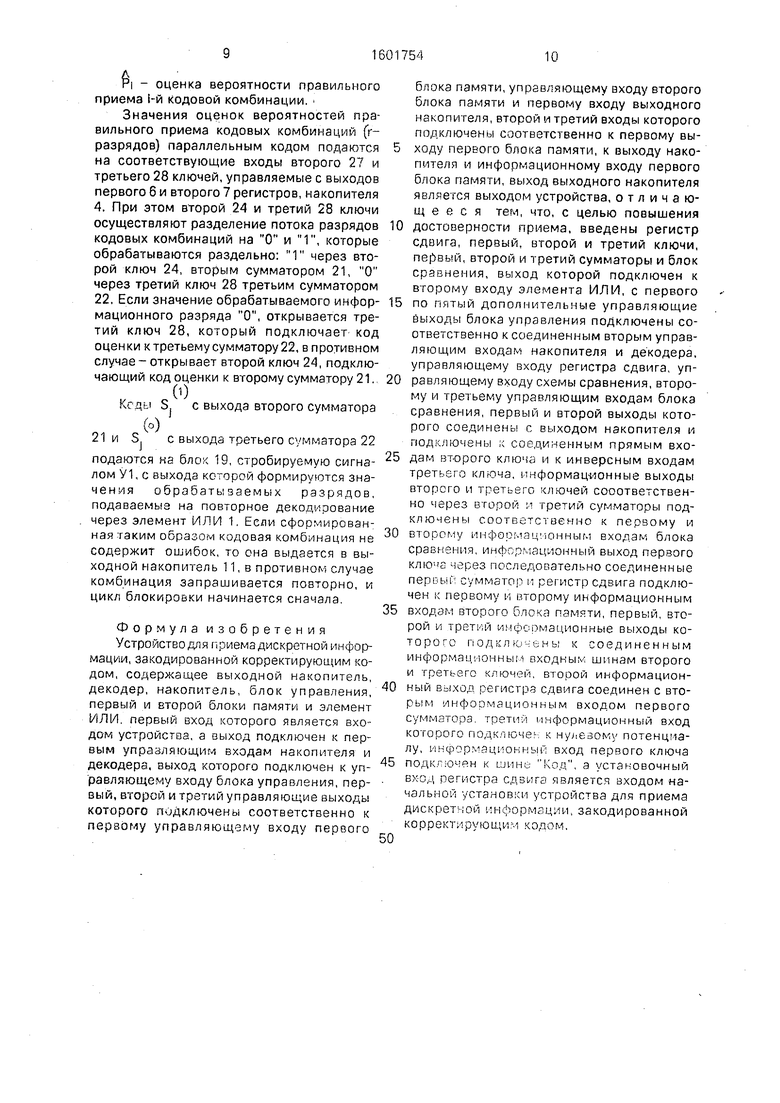

На фиг. 1 представлена структурная схема устройства для приема дискретной инфор- мации, закодированной корректирующим кодом; на фиг.2 - временные диаграммы.

Устройство для приема дискретной информации, закодированной корректирующим кодом, содержит элемент ИЛИ 1, декодер2, блокЗ управления, накопитель4, первый блок 5 памяти, содержащий первый 6 и второй 7 регистры сдвига, первый 8 м второй 9 элементы И и элемент ИЛИ 10, выходной накопитель 11, содержащий эле- мент ИЛИ 12 и регистр 13 сдвига, второй блок 14 памяти, содержащий первый 15, второй 16 и третий 17 регистры сдвига, регистр 18 сдвига, блок 19 сравнения, первый 20, второй 21 и третий 22. сумматоры, пер- вый ключ 23, второй ключ 24, содержащий первый 25, второй 26 и третий 27 элементы И, и третий ключ 28, содержащий первый 29,- второй 30 и третий 31 элементы И.

Устройство работает следуюа им обра- зом.

На вход устройства в накопитель 4 через элемент ИЛИ 1 под управлением сдвиговых импульсов А, вырабатываемых блоком 3 непрерывно поэлементно, посту- пает последовательность кодовых комбинаций с одновременным декодированием в декодере 2, Последний представляет собой декодер циклического кода, обнаруживающего ошибки. Сигнал обнаружения ошибки (ненулевой синдром) с декодера 2 в виде признака 1 записывается в блок 3 последующим сдвигом импульсами В.

В блоке 3 формируются импульсы управления, обозначенные на фиг.2 как А, В, С.

Сигнал С имеет наименьший период повторения, достаточный для осуществления считывания накопленной в первом блоке 5 информации до момента прихода очеред- ной правильно принятой комбинации. Сигнал А имеет период повторения, равный длительности разряда комбинации, ситал В - период поеторения, равный длительности кодовой комбинации. Сигнал А используется для записи коиблнаций в бло па( ляти и выходной накоп1 тель, сигнал С - для с- |;1тывания.

Сигнал А блока 3 1/;сг ътьзуется в качестве сдвиговых (тактовыл) /.мпульсов, сдвигающих информацию в /;акопителе 4 и декодере 2 (в сдвиговых i. агмстрах), сигнал В - в качестве с.двигоь.;/. импульсов в регистре 18. Сигнал V1, 9Орм;фуемый с выхода блока 3, служит СНГНЁЛОМ разрешения (стробирования) иыполги ния операции обработки накопле.ных иска кенных кодовых комбинаций, Ситзл У2, формируемый на выходе ,у,1раБ пяэтзаписьюпринятыхко довых uor.i6i iHaij /if :. выходной накопитель 11 и пре,аставлязт сооо: ; о/и нал типа А, стро- биру мый блоко. 3 Г1р,л передаче информации i/iii накопителя 4, сигнал типа С, строб лру8мый L osvGv 3 npi считывании информации из гч-jpBorc 6 i i второго 7 регистров блока 5. Снгнзл УЗ, Ф0|., с выхода блока 3, упрьзяяэт зап;, 1ьью з пер вый 6 и второй 7 регистры блока 5 с помощью стробмруемого сиг|--ала типа А и последующей перезаписью (считывгнием) з выходной накопитель 11 с помощью строби- руемого сигнала типа С.

Сигнал У4. формируемый с выхода блока 3, прО Зводит набср первого 6 или второго 7 регистра для сч ггывания из блока 5 а выходной накопитель 11. Сигнал У5 с выхода блока 3 осуществляет запрет выбора регистров бло кз 5 Г1ри считывании информзцми. Сигнал У6, формируемый с выхода блока 3, управ.пяет записью в блок 14 и является сигналов сдвига в первом 15, гором 16 и третьем 17 регистрах. Сигнал У7 является внутренним сигналом блока 3.

Предварительно перед началом приема производится устаноэка всей аппаратуры Б начальное состояние.

После начальной установки в блоке 3 формируется сигнал У2 типа А, разрешающий запись принятой комбинации в выходной накопитель 11, Если после приема и декодирования кодовой комбинации декодер.2 я ормирует сигнал О {нулевой синдром), записываемый в блок 3, тактовыми импульсами У2 типа А правильно принятая кодовая комбинация сдвигается из накопителя 4 через элемент ИЛИ 12 в регистр 13 выходного накопителя 11.

Рассматривают несколько аозмож - ых вариантов приема искаженных кодовых комбинаций.

1) После завершения первой блокировки повторно переданная комбинация принята без ошибок (признак О),

В первом регистре 6 записаны кодовые комбинации, накопленные на длина первой блокировки. Считывание кодовых комбина-.

ций из первого регистра 6 в регистр 13 выходного накопителя 11 производится в ускоренном темпе с помощью импульсов типа С до момента приема очередной кодовой комбинации, при этом признаки этих кодовых 5 комбинаций также сдвигаются иг/шульсами из сигнала У2 типа С.

Правильный прием повторяемой комбинации, с которой началась блокировка, сопровождается следующими действиями. В 10 этот момент сигналом УЗ на выход первого регистра 6 сдвигается пepвo iaчaльнo принятая искаженная комбинация, которую нельзя выдавать потребителю: Поэтому блок 3 формирует сигнал У5 запрета выдачи 15 ошибочной комбинации из первого блока 5 в выходной накопитель 11. Значение сигнала У5 - логический О. Сигнал У5 закрывает первый 8 и второй Э элемент, запрещая выдачу искажанной комбинации из первого 20 регистра 6 (хотя сдвиги в первом блоке 5 пооцогжаются), а правильно принятая по- ьторяйг. Г комоикация сигналом У2 записы- еаегся j ль холной накопител:. М . Все; псследуюиЬ ь . накопленные на 25 д/:1. первой блокировки в осгист- ре 6 и iipi-ii-iHToie и::з сигналом УЗ типа С из nepnofo регистра 5, с,-:1;:г уются 8 выходной на«ч; - итель 11 cмг iзлo: : У2 типа С. При зто:.: выбор рйгмстра из Ьлс-кс 5 поо- 30 изводится с/;гнзлом V4. Значе::ие признака кo :бинaци ;. пи. мя- ой на длине 5лок:, ;ров- ки, равно О -, г.:этс-.-|у с выходд б/ Окз 3 формируется сигнал 1 У4, ,:й пт::.рь1- вает второй И 9 и через элемент 35 ИЛИ 10 ко.1си- :;ч и.1 ;.;з первого Dor-icvo,n 6 выдаются в вь: ;:;;;:;нсй накопи-гело 11 год управлением сигналов У2, УЗ Пм-а П По .окончании г; Н1ть;занг:Я из перБого блока завершается pOKVM Босстаноеле -1ия первона- 40 чального порядк9 С;;едовс1ния кодовых комбинаций до момента приема очере.апой комбина1,;.1И мз зь: ;одного накопи еля и,

2) Мосле ззоери -; -;ия пераой блокировки повторяемая комоинация искажена DTC- 45 рой раз, ее признак { Г } записываете - Е блок 3 сигнале:.; В. Н копле --/ ;-- цин второй блокирозки сог1ровождае,-ся приемом кодовых комСичациЯ (без ошибок и с ошибками) и заги в первый регистр 6 с 50 последую Ц11м сигналом УЗ типа А. соотЕетсгг зуюн1ие им признака записываются з.илок 3 с ПОС.ПЭДУЮЩИМ сдвигом сиг- ;-i ало М 3. Но i е р е приема к о .ц о в ы х комбинац1 й они сд1:игзются из первого 5В регистра 6 во зторой регистр 7 пеово -о бло- ;са 5,

3 Начапо третьей блокировки сопровождается Г м;;п;, ;льНЫМ ПрИбМОМ рЗНве

важды искз-гбнной комбинации, то ее гфи J

знак (О) совместно с соответствующими ей признаками (1) о результатах предыдущих приемов формирует О - сигнал У5 на выходе блока 3, запрещающий считывание искаженных комбинаций из первого 6 и второго 7 регистров в выходной накопитель 11. Сигнал У5 закрывает первый 8 и второй 9 элементы первого блока 5 и правильно принятая комбинация передается в регистр 13 выходного накопителя 11 через элемент И.Г1И 12 под управлением сигнала У2 типа А. 4) Начало третьей блокировки сопровождается искаженным приемом кодовой комбинации (ранее дважды искаженной), сигналы 1 о результатах трехкратного подряд искажения одноименной кодовой комбинации с выхода блока 3 выдаются как сигнал У1 для разрещения операции обра- оотки накопленных на длине блокировки кодовых комбинаций. На выходе блока 3 формируется сигнал сброса, завершая блокировку и разрешая этап считывания из первого блока 5 сигналом УЗ и запись в ьэыходгпой накопитель 11 сигналом У2 анало- гипным образом, как было отмечено для первой и второй блокировок-. При этом предварительно осуидествляется обработка на- коплен1-1ых на длине блокировки трижды искзл б пных одноименных кодовых комби- |-:аций. которая осуществляется на основе оценки вероятности правильного приема кодовь:х комбинаций, определяемой по фор|-.-1..че

. N

1

V

i 1

(1)

- случайная величина, принимающая зкйчение 1 (правильный прием) и О (искаженный прием.

|- едостатком оценки (1) является то, что результат приема текущей кодовой комбинации учитывается в оценке с постоянным ьесом 1/N, в то время, как для реальных каналов характерна убывающая память, распространяющаяся на несколько кодо- Bbix комбинаций. Это обстоятельство можно учесть, например, убывающим весом где /3 1; I -текущий номер принимаемой кодовой комбинации. Тогда по аналоги1 1 с вь:-ражением (1) N - 2

Р--( -/3)/3, XI-1-(1-/3)/3 ,...-(l-/)xi,(l-)2 ,

или после преобразования

/ЗРы-1-Ь(1-/5)хг,,

где b,N - оценка после приема Nцин;

X N признак приема N-й комбинации. Оценка (2) допускает простую техниче- Ькую реализацию: если взять 2 , где t - Цисло разрядов, то вычисление оценки

(1-2 )XN {сводится к организации сдвига на t разрядов в сторону младших разрядов значения юценки Р N-1 предыдущего шага и сложения JC постоянным кодом (1-2) при правильном приеме (признак 1), при искаженном приеме (признак О) второе слагаемое не учитывается. Подобная оценка аппаратно реализуется с помощью первого ключа 23, первогосумматора20, регистра 18. При без- ошибочном приеме признак О с выхода декодера 2 открывает первый ключ 23, раз- j решая считывание по шине Код г-разря- дов значения кода (1-2) на первый 1 сумматор 20. По шине Код подается г-раз- i рядов значения кода (1-2 являющегося i слагаемым оценки (2), поэтому первый ключ I 23 является многовходовым элементом И, управляемым стробом с декодера 2.

На другие входы первого сумматора 20- поступает значение другого слагаемого, являющегося оценкой PN-I предыдущего шага.

На начальном этапе необходимо опое- делить предыдущее значение оценки - Ко, которое выбирается произвольно. Однако целесообразно провести предварительное исследование статистических характеристик канала и выбрать среднее или наибольшее значение оценки Ро. Тогда перед началом приема необходимо произвести начальную установку регистра 18 для последующего использования Ро в формировании оценки. Последующие операции (умножение) требуют предварительного сдвига предыдущих значений оценок в сторону младших разрядов на t разрядов, что можно провести путем отбрасывания младших разрядов значения оценки предыдущего шага (t разряды регистра 18 не участвуют в формировании следующей оценки), а другие (г-г разряды подключают к соответствующим (г-г входом первого сумматора 20 как второго слагаемого. При этом оставшиеся свободными t-входы старших разрядов второго слагаемого первого сумматора 20 подключают к нулевому входу (уровень О).

Вычисляемая на каждом такте оценка с первого сумматора 20 под управлением импульсов В записывается в регистр 18, который хранит оценку (г-разрйдов) для использования ее в дальнейшем, как оценку предыдущего шага. С выхода регистра 18 полученная оценка параллельным кодом записывается в первый регистр 15 второго блока 14 сигналом У6. Следующее значение оценки может быть записано (не записано) в зависимости от сигнала У6; если запись сигналом У6 разрешается, значение ранее записанной оценки сдвигается во второй регистр 16, а в первый регистр 15 записывается новое значение и т.д. Таким образом после трехкратного подряд искаженного 0 приема в регистрах 15-17 сигналом У6 записаны соответствующие им значения оценок вероятностей правильного приема на момент приема этих комбинаций, при этом в первом блоке 5 и накопителе 4 зафик- 5 сированы соответствующие комбинации (т.е. трижды подряд искаженные). В этом случае начинается обработка накопленных на длине блокировки комбинаций, заключающаяся в следующем.

0 Одноименные информационные разряды трех искаженных кодовых комбинаций, накопленных на трех блокировках, разделяются на два отдельных типа (О и 1), каждый из которых обрабатывается отдельно. 25 Обработка заключается в суммировании кодов оценок вероятностей правильного приема кодовых комбинаций, выступающих как весовые коэффициенты, для однотипных разрядов (отдельно для О и 1) и сравне- 30 ние их между собой. Для этого вычисляются значения кодов Sj по формуле (3) отдельно

(о) для одноименных разрядов О - S, и от0)

35 дельно для 1 - S , а затем их сравнение.

(1) (о) При этом, если S S . принимается

решение о принятом j-м единичном разря(i) (о) де, в противном случае (S, S, )

s ° iio ii-p;

J 1 1

(1) mЛ

S, S li i}-Pi

j 1 ,n,

(3)

где n - разрядность кодовой комбинации;

m - число переспросов кодовой комбинации (число повторений кодовой комбинации, принятой с ошибками):

показатель, равный Г. если j-й разряд 1-й кодовой комбинации равен О, и равный О в противном случае;

li i - показатель, равный Г, если j-й разряд 1-й кодовой комбинации равен Г, и равный О в противном случае;

Pi - оценка вероятности правильного приема 1-й кодовой комбинации.

Значения оценок вероятностей правильного приема кодовых комбинаций fr разрядов) параллельным кодом подаются на соответствующие входы второго 2 и третьего 28 ключей, управляемые с выходов первого 6 и второго 7 регистров, накопителя 4. При этом второй 24 и третий 28 ключи осуществляют разделение потока разрядов кодовых комбинаций на О и 1, которые обрабатываются раздельно: 1 через второй ключ 24, вторым сумматором 21, О через третий ключ 28 третьим сумматором 22. Если значение обрабатываемого инфор- мационного разряда О, открывается третий ключ 28, который подключает код оценки к третьему сумматору 22, в противном случае-открывает второй ключ 24, подключающий код оценки к второму сумматору 21.

0) Кеды S с выхода второго сумматора

(о)

21 и Sj с выхода третьего сумматора 22 подаются на блок 19, стробируемую сигна- лом У1, с выхода которой формируются значения о5рабатызаемь х разрядов, подаваемые на повторное декодирование через элемент ИЛИ 1. Если сформированная таким образом кодовая комбинация не содержит ошибок, то она выдается в выходной накопитель 11, в противном случае комбинация запрашивается повторно, и цикл блокировки начинается сначала.

Формула изобретения Устройство для приема дискретной информации, закодированной корректирующим кодом, содержащее выходной накопитель, декодер, накопитель, блок управления, первый и второй блоки памяти и элемент ИЛИ. первый вход которого является входом устройства, а выход подключен к первым управляющим входам накопителя и декодера. которого подключен к управляющему входу блока управления, первый, второй и третий управляющие выходы которого подключены соответственно к первому управляющему входу первого

510 15 20

30

5

0

5

0

блока памяти, управляющему входу второго блока памяти и первому входу выходного накопителя, второй и третий входы которого подключены соответственно к первому выходу первого блока памяти, к выходу накопителя и информационному входу первого блока памяти, выход выходного накопителя является выходом устройства, отличающееся тем, что, с целью повышения достоверности приема, введены регистр сдвига, первый, второй и третий ключи, первый, второй и третий сумматоры и блок сравнения, выход которой подключен к второму входу элемента ИЛИ, с первого по пятый дополнительные управляющие йыходы блока управления подключены соответственно к соединенным вторым управляющим входам накопителя и декодера, управляющему входу регистра сдвига, управляющему входу схемы сравнения,второму и третьему управляющим входам блока сравнения, первый и второй выходы которого соединены с выходом накопителя и подключены к соединенным прямым входам второго ключа и к инверсным входам третьего кльоча, и.чформащ-юнные выходы второго и третьего ключей сооответствен- но через второй и третий сумматоры подключены соответственно к первому и второму информац .юнным входам блока сравнения, информационный выход первого клю га через последовательно соединенные первый сумматор н регистр сдвига подключен к первому и второму информационным входам второго блока памяти, первый, второй и третий информационные выходы которого подключены к соединенным информационным входным шинам второго и третьего ключей, второй информационный выход регистра сдвига соединен с вторым информационным входом первого сумматора, третий информационный вход которого подключен к нулевому потенциалу, информационный вход первого ключа подключен к шине Код, а установочный вход регистра сдвига является входом начальной установки устройства для приема дискретной информации, закодированной корректирующим кодом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1596464A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1987 |

|

SU1462492A1 |

| Устройство для приема дискретной информации,закодированной корректирующим кодом | 1983 |

|

SU1099397A2 |

| Устройство для приема дискретной информации,закодированной корректирующим кодом | 1984 |

|

SU1172022A2 |

| Устройство для приема дискретной информации | 1981 |

|

SU1131031A1 |

| Многоканальная кодоимпульсная система телесигнализации | 1986 |

|

SU1325544A1 |

| АДАПТИВНЫЙ ДЕКОДЕР | 2008 |

|

RU2379833C1 |

| Устройство для приема телесигналов | 1981 |

|

SU1003127A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1408531A1 |

| Многоразрядный генератор испытательных последовательностей | 1983 |

|

SU1133589A1 |

Изобретение относится к электросвязи и может использоваться при построении аппаратуры передачи данных, в которой для обеспечения требуемой верности передачи применяют избыточный код в режиме обнаружения ошибок с непрерывной последовательной передачей кодовых комбинаций и решающей обратной связью при работе на каналах низкого качества, характеризующихся изменением параметров в широких пределах. Цель изобретения - повышение достоверности приема. Для этого устройство содержит эл-т ИЛИ 1, декодер 2, блок управления 3, накопитель 4, блок памяти 5, состоящий из регистров 6 и 7 сдвига, эл-тов И 8 и 9 и эл-та ИЛИ 10, выходной накопитель 11, состоящий из эл-та ИЛИ 12 и регистра 13 сдвига, блок памяти 14, состоящий из регистров 15, 16 и 17 сдвига, регистр 18 сдвига, блок сравнения 19, сумматоры 20, 21 и 22, ключ 23, ключ 24, состоящий из эл-тов И 25, 26 и 27, и ключ 28, состоящий из эл-тов И 29, 30 и 31. 2 ил.

| Устройство для приема дискретной информации,закодированной корректирующим кодом | 1983 |

|

SU1099397A2 |

Авторы

Даты

1990-10-23—Публикация

1988-06-17—Подача