Фиг./

Изобрйтенне относится к вычислительной технике и может быть использовано для контроля интерфейсных последовательностей ,

Целью изобретения является повышение достоверности контроля сигналов .

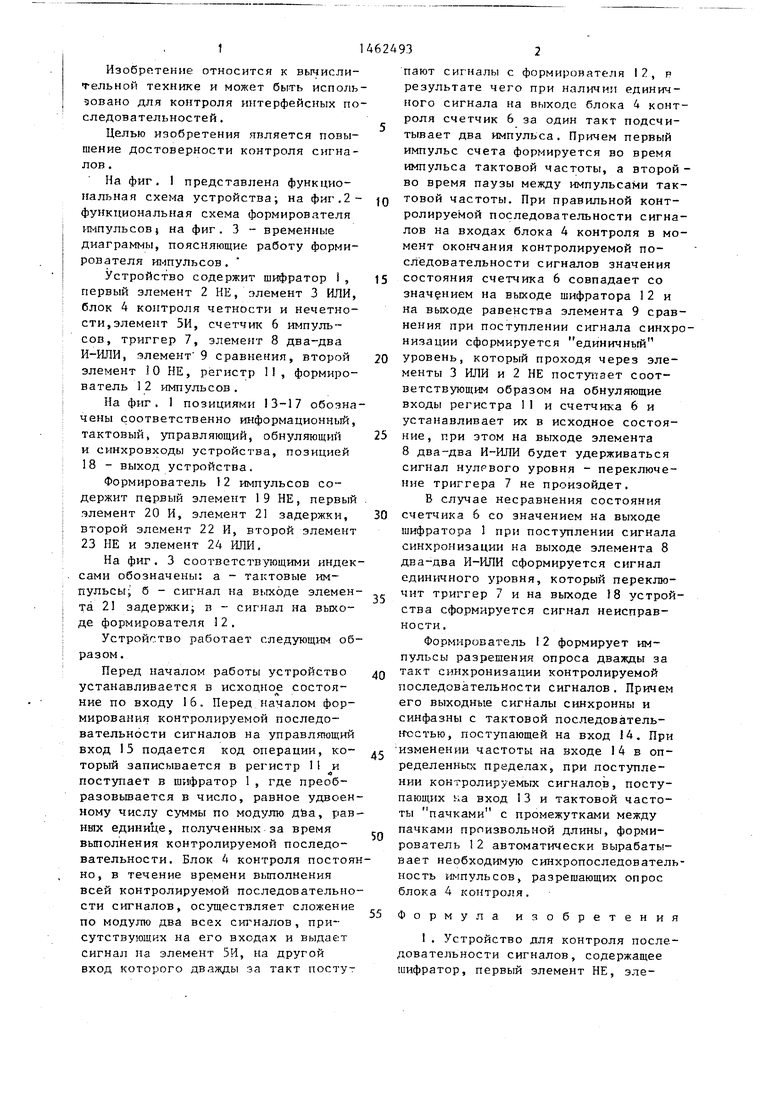

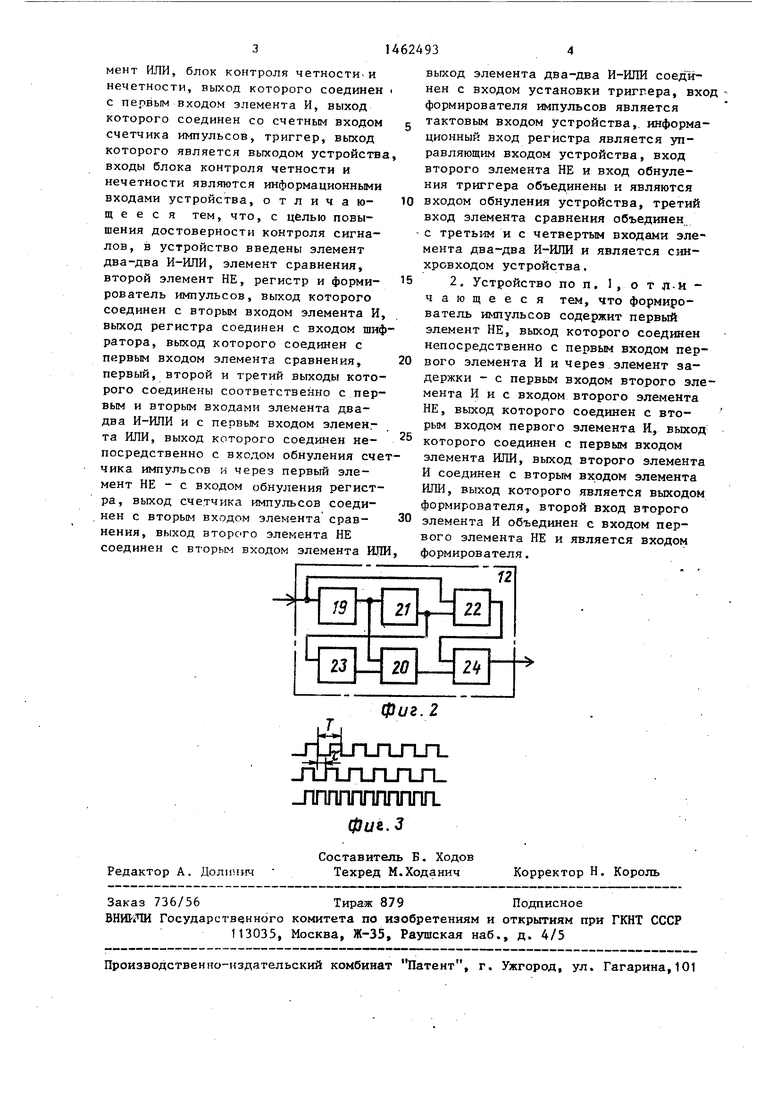

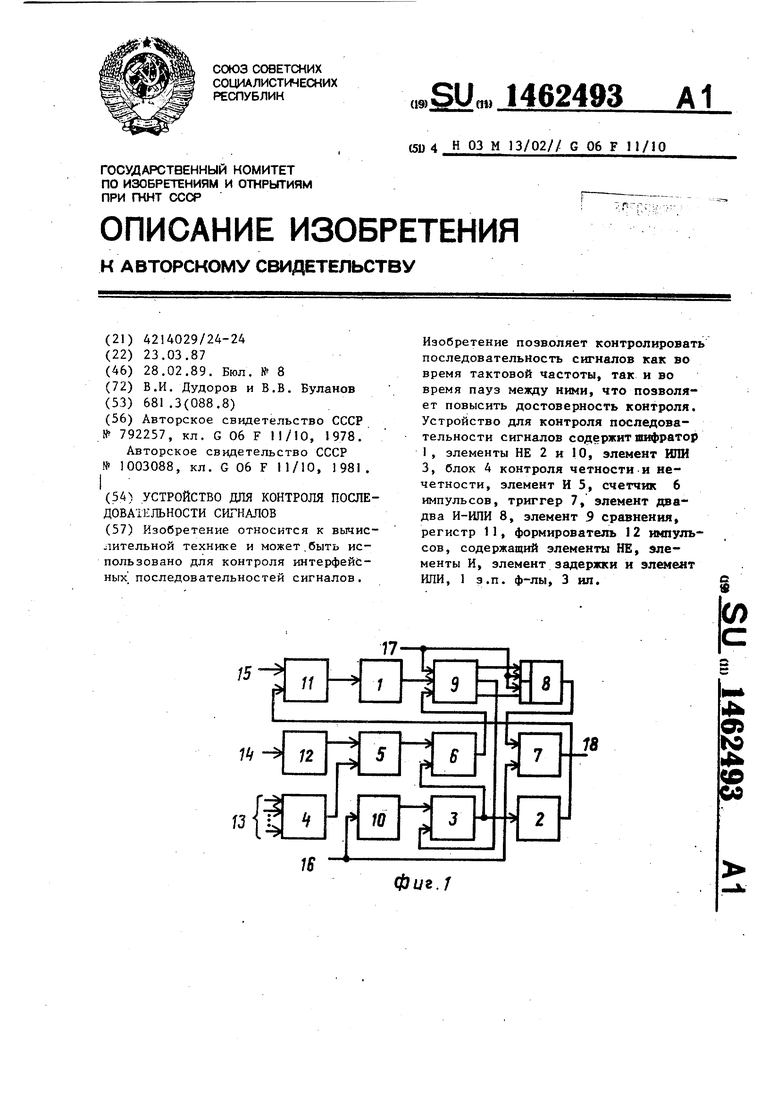

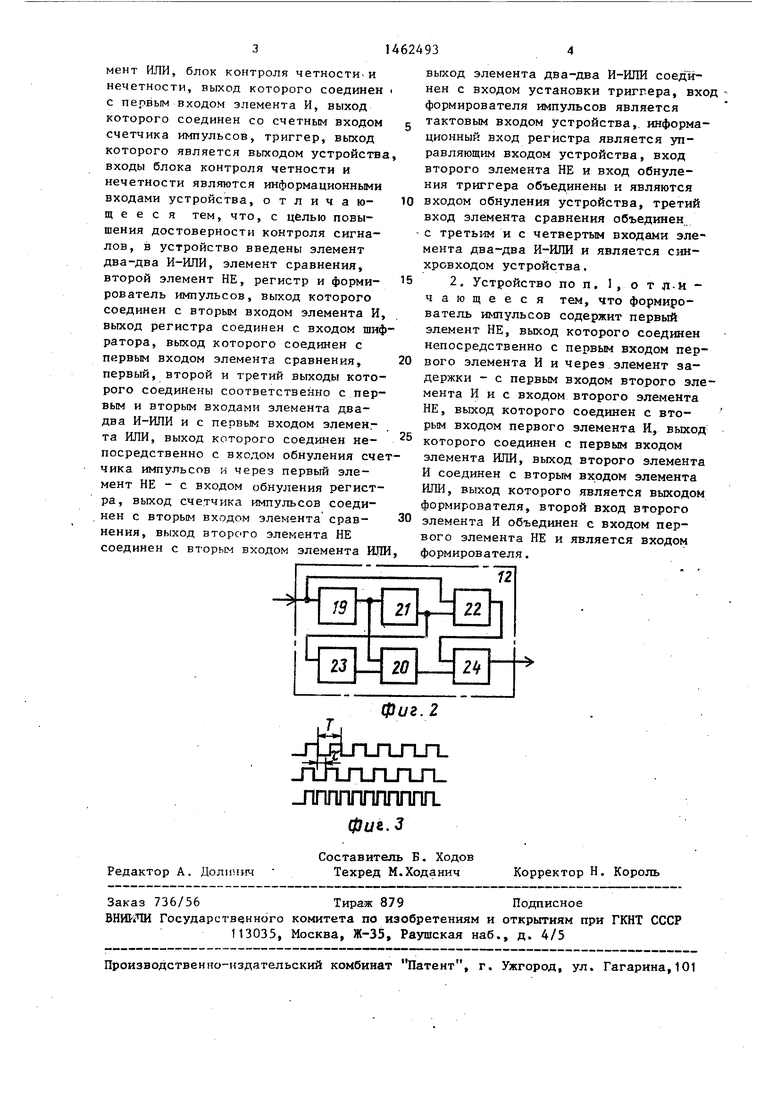

На фиг. I представлена функциональная схема устройства; на фиг.2- функциональная схема формирователя ИМПУЛЬСОВ} на фиг. 3 - временные диаграммы, поясняющие; работу формирователя И 1ПУЛЬСОВ .

Устройство содержит шифратор i , первый элемент 2 НЕ, элемент 3 ИЛИ, блок 4 контроля четности и нечетности, элемент 5И, счетчик 6 импульсов, триггер 7, элемент 8 два-два И-ИЛИ, элемент 9 сравнения, второй элемент 10 НЕ, регистр 1, формирователь 12 импульсов.

На фиг. 1 позициями 13-17 обозначены соответственно информационный, тактовый, управляющий, обнуляющий и синхровходы устройства, позицией 18 - выход устройства.

Формирователь 12 импульсов содержит первый элемент 19 НЕ, первый элемент 20 И, элемент 21 задержки, второй элемент 22 И, второй элемент 23 НЕ и элемент 24 ИЛИ,

На фиг, 3 соответствующими индексами обозначены: а тактовые импульсы б - сигнал на выходе элемента 21 задержки; в - сигнал на выходе формирователя 12.

Устройство работает следующим образом.

Перед началом работы устройство устанавливается в исходное состояние по входу 16, Перед началом формирования контролируемой последовательности сигналов на yпpaвлшoщ й вход 15 подается код операции, который записывается в регистр 11 и поступает в шифратор 1 , где преоб- разовьшается в число, равное удвоенному числу суммы по модулю дйа, рав- них единице, полученных за время выполнения контролируемой последовательности. Блок 4 контроля постоянно, в течение времени выполнения всей контролируемой последовательности сигналов, осуществляет сложение по модулю два всех сш налов, присутствующих на его входах и выдает сигнал на элемент 5И, на другой вход которого дважды за такт посту0

5

0

5

0

5

0

5

0

пают сигналы с формирователя 12, р результате чего при наличии единичного сигнала на выходе блока 4 контроля счетчик 6 за один такт подсчитывает два импульса. Причем первый импульс счета формируется во время импульса тактовой частоты, а второй - во время паузы между импульсами тактовой частоты. При правильной контролируемой последовательности сигналов на входах блока 4 контроля в момент окончания контролируемой последовательности сигналов значения состояния счетчика 6 совпадает со значением на выходе шифратора 12 и на выходе равенства элемента 9 сравнения при поступлении сигнала синхронизации сформируется единичный уровень, который проходя через элементы 3 ИЛИ и 2 ЕЕ поступает соответствующим образом на обнуляющие входы регистра 11 и счетчика 6 и устанавливает их в исходное состояние, при этом на выходе элемента 8 два-два И-ИЛИ будет удерживаться сигнал нулРвого уровня - переключение триггера 7 не произойдет.

В случае несравнения состояния счетчика 6 со значением на выходе шифратора 1 при поступлении сигнала синхронизации на выходе элемента 8 два-два И-ИЛИ сформируется сигнал единичного уровня, который переключит триггер 7 и на выходе 18 устройства сформируется сигнал неисправности .

Формирователь I2 формирует импульсы разрешения опроса двазвды за такт синхронизации контролируемой последовательности сигналов. Причем его выходные сигналы синхронны и синфазны с тактовой последователь- нчзстью, поступающей на вход IA. При изменении частоты на входе 14 в определенных пределах, при поступлении контролируемых сигналов, поступающих ка вход 13 и тактовой частоты пачками с промежутками между пачками произвольной длины, формирователь 2 автоматически вырабатывает необходимую синхропоследователь- ность импульсов, разрешающих опрос блока 4 контроля.

Ф о

мула изобретения

. Устройство для контроля последовательности сигналов, содержащее шифратор, первый элемент НЕ, элемент ИЛИ, блок контроля четности и нечетности, выход которого соединен с первым входом элемента И, выход которого соединен со счетным входом счетчика импульсов, триггер, выход которого является выходом устройства входы блока контроля четности и нечетности являются информационными входами устройства, отличаю- щ е е с я тем, что, с целью повышения достоверности контроля сигналов, в устройство введены элемент два-два И-ИЛИ, элемент сравнения, второй элемент НЕ, регистр и форми- рователь импульсов, выход которого соединен с вторым входом элемента И, выход регистра соединен с входом шифратора, выход которого соединен с первым входом элемента сравнения, первый, второй и третий выходы которого соединены соответственно с первым и вторым входами элемента два- два И-ИЛИ и с первым входом элемен,- та ИЛИ, выход которого соединен не- посредственно с входом обнуления счечика импульсов и через первый элемент НЕ - с входом обнуления регистра, выход сче,тчика импульсов соединен с вторым входом элемента срав- нения, выход второго элемента НЕ соединен с вторым входом элемента ИЛИ

выход элемента два-два И-ИЛИ соединен с входом установки триггера, вхо формирователя импульсов является тактовым входом устройства,, информационный вход регистра является заправляющим входом устройства, вход второго элемента НЕ и вход обнуления триггера объединены и являются входом обнуления устройства, третий вход элемента сравнения объединен - с третьим и с четвертым входами элемента два-два И-ИЛИ и является син- хровходом устройства.

2, Устройство по п. 1,отл-И- чающееся тем, что формирователь и myльcoв содержит первый элемент НЕ, выход которого соединен непосредственно с первым входом первого элемента И и через элемент задержки - с первым входом второго элемента И и с входом второго элемента НЕ, выход которого соединен с вторым входом первого элемента И, выход которого соединен с первым входом элемента ИЛИ, вькод второго элемента И соединен с вторым входом элемента ИЛИ, выход которого является выходом формирователя, второй вход второго элемента И объединен с входом первого элемента НЕ и является входом формирователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА ЦИФРОВОГО СТЕРЕОФОНИЧЕСКОГО РАДИОВЕЩАНИЯ | 1991 |

|

RU2019041C1 |

| ЦИФРОВАЯ СИСТЕМА РАДИОВЕЩАНИЯ | 1992 |

|

RU2048704C1 |

| Устройство для прерывания программ | 1982 |

|

SU1072045A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1084800A2 |

| Устройство для имитации неисправностей | 1985 |

|

SU1273933A1 |

| Устройство для селекции и счета объектов,расположенных беспорядочно | 1985 |

|

SU1325539A1 |

| Устройство обмена информацией между ЭВМ и абонентами | 1990 |

|

SU1835545A1 |

| Устройство для контроля оперативной памяти | 1982 |

|

SU1022225A1 |

| ЦИФРОВОЙ РАДИОТЕЛЕФОН | 1994 |

|

RU2093960C1 |

| Датчик сообщений | 1985 |

|

SU1282348A1 |

Изобретение относится к вычис- тительной технике и может,быть использовано для контроля интерфейсных последовательностей сигналов. Изобретение позволяет контролировать последовательность сигналов как во время тактовой частоты, так и во время пауз между ними, что позволяет повысить достоверность контроля. Устройство для контроля последовательности сигналов содержит шифратор 1, элементы НЕ 2 и 10, элемент ИЛИ 3, блок 4 контроля четности и нечетности, элемент И 5, счетчик 6 импульсов, триггер 7, элемент два- два И-ИЛИ 8, элемент 9 сравнения, регистр 11, формирователь 12 импульсов, содержащий элементы НЕ, элементы И, элемент задержки и элемент ИЛИ, 1 э.п. ф-лы, 3 ил.

23

Т

«-

А. Долииич

gjUTJ-LTL JlJT-TLrLTLrb

-пплллпппппа

Q&i/e.J

Составитель Б. Ходов Техред М.Ходанич

Г2

20

2it

фиг. 2

Корректор Н. Король

| Устройство для контроля последовательности сигналов | 1978 |

|

SU792257A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля блоков управления | 1981 |

|

SU1003088A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-02-28—Публикация

1987-03-23—Подача