входами блока анализа адресного кода, выход первого и второй вход } последнего полусумматоров являются соответственно выходом и управляющим

входом блока анализа адресного кода, второй вход каждого полусумматора соединен с выходом последующего полусумматора,.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков оперативной памяти | 1983 |

|

SU1161993A1 |

| Устройство для контроля блоков оперативной памяти | 1980 |

|

SU924758A1 |

| Устройство для контроля оперативной памяти | 1980 |

|

SU955208A1 |

| Устройство для контроля оперативной памяти | 1982 |

|

SU1024990A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1001182A1 |

| Устройство для контроля оперативной памяти | 1975 |

|

SU547837A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1014041A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

Изобоетение относится к вычисли-.. тельной технике, а именно- к запоми:нающим устройствам. ; .Известно устройство для контроля оперативной памяти, содержащее блок :управления, первый счетчик и регистр числа, подключенные к выходным шинам устройства, триггер, формирователь, элемент И, второй счетчик, предназначенный для подсчета подциклов, третий счетчик, полусумматор, основные и дополнительные коммутаторы. К устройству подключается контролируемый блок оперативной памяти C lНедостаток указанного устройства невысокая эффективность контроля.

Наиболее близким к предлагаемому является устройство для контроля блоков оперативной памяти, содержащее блок управления, .первый счетчик и

,регистр, числа, подключенные к выходным шинам устройства, первый триггер формирователь импульсов, элемент ЗАПРЕТ, второй и третий счетчики, второй-триггер, полусумматор, основные и дополнительные коммутаторы С 2

Недостатком известного устройства является невысокая достоверность кон роля, так как тесты типа Дождь, Адресный код и Шахматный код не обеспечивают полной проверки oneра тивной памяти, В частности, недостаточно эффективно проверяются такие параметры дешифратора адреса, как отсутствие выборки и неоднозначность выборки.

Цель изобретения - повышение достоверности контроля за счет обеспечения возможности формирования устройством как тестов .типа Дождь, Адресный код, Шахматный ко так и теста Четность (нечетность) адреса.

Поставленная цель достигается тем, что в устройство для контроля оперативной памяти, содержащее блок управления, регистр числа, элемент ЗАПРЕТ, два триггера, формирователь импульсов, основные и дополнительные коммутаторы, полусумматор и три счетчика, причем выходы первого счет чика, регистра числа и первый выход блока.управления являются выходами устройства, второй выход блока управления соединен с первым входом фор1«1рователя импульсов, выход которого

подключен к управляющему входу элемента ЗАПРЕТ, выход которого соединен с входом первого счетчика, выход последнего разряда которого соединен с входом первого триггера, выход которого подключен к второму входу формирователя импульсов и входу полусуг аиатора, другой вход которого содинен с выходом последнего разряда третьего счетчика, третий выход блока управления соединен с третьим входом формирователя импульсов, входом третьего счетчика, информационным входом элемента ЗАПРЕТ и счетным входом второго триггера, прямой и инверсный выходы которого соединены соответственно с. первыми и вторыми информационными входами основных коммутаторов, третьи информационные входы которых соединены с выходом полусумматора и входом второго счетчика, выходы второго и третьего счетчиков соединены соответственно с управлякидими и информационными входами дополнительных коммутаторов, выходы которых подключены к четвертым информационным входам основных коммутаторов, первый и второй управляющие чвходы которых соединены соответственно с четвертым и пятым выходами блока управления, один из выходов первого счетчика соединен с третьими управляющими входами основных коммутаторов, выходы которых соединены с входами регистра числа, дополнительно введены блок анализа сщресного кода, третий триггер и 4юрмироватёдь импульса сброса, причем выходы первого счетчика соединены с информационными входами блока анализа адресного кода, выход которого соединен с.пятыми информационными входами основных коммутаторов, выход первого триггера соединен с входом третьего триггера, выход которого соединен с управляющим входом блока анализа адре сного кода, выход первого триггера соединен с входом формирователя импульса сброса, выход которого подключен к входу установки в единичное состояние второго триггера, вход синхронизации регистра числа соединен с третьим выходом блока управления, вход которого соедине с выходом первого триггера.

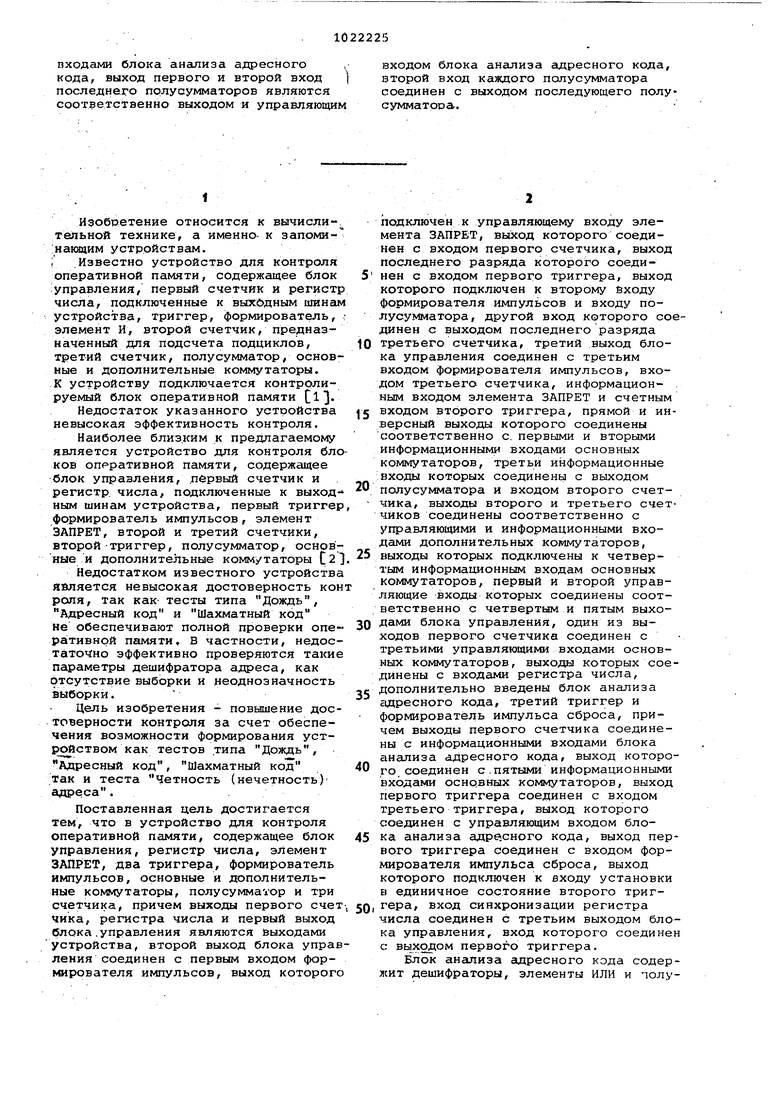

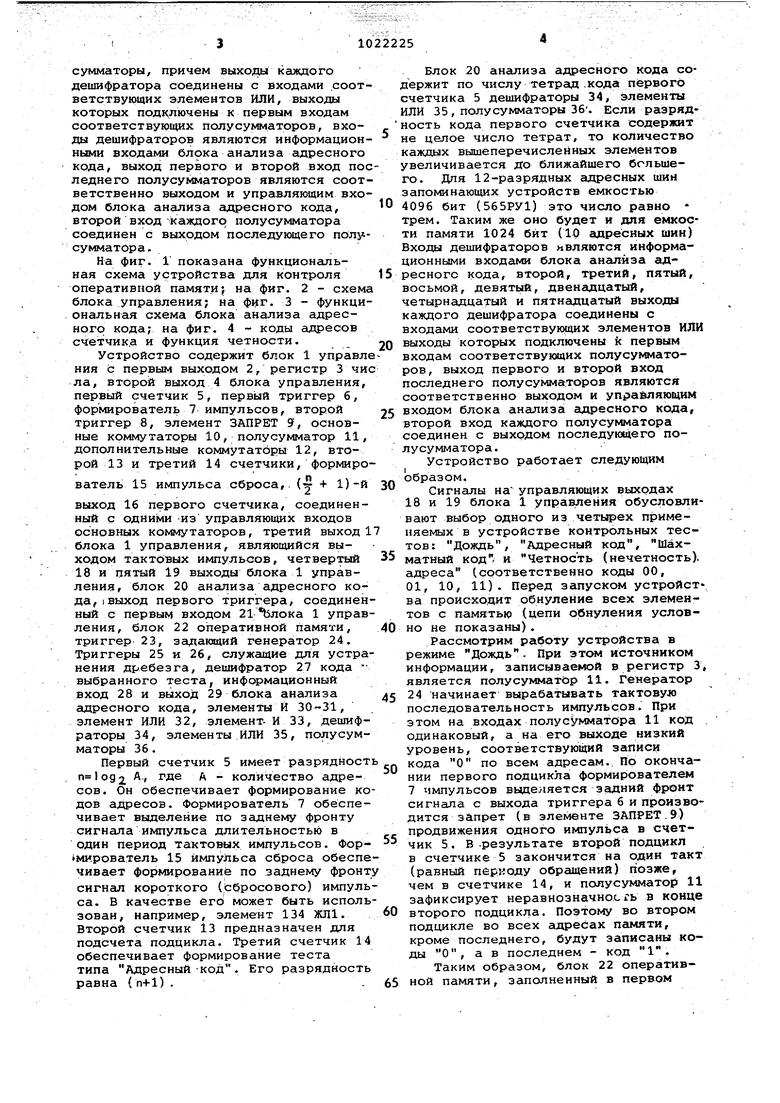

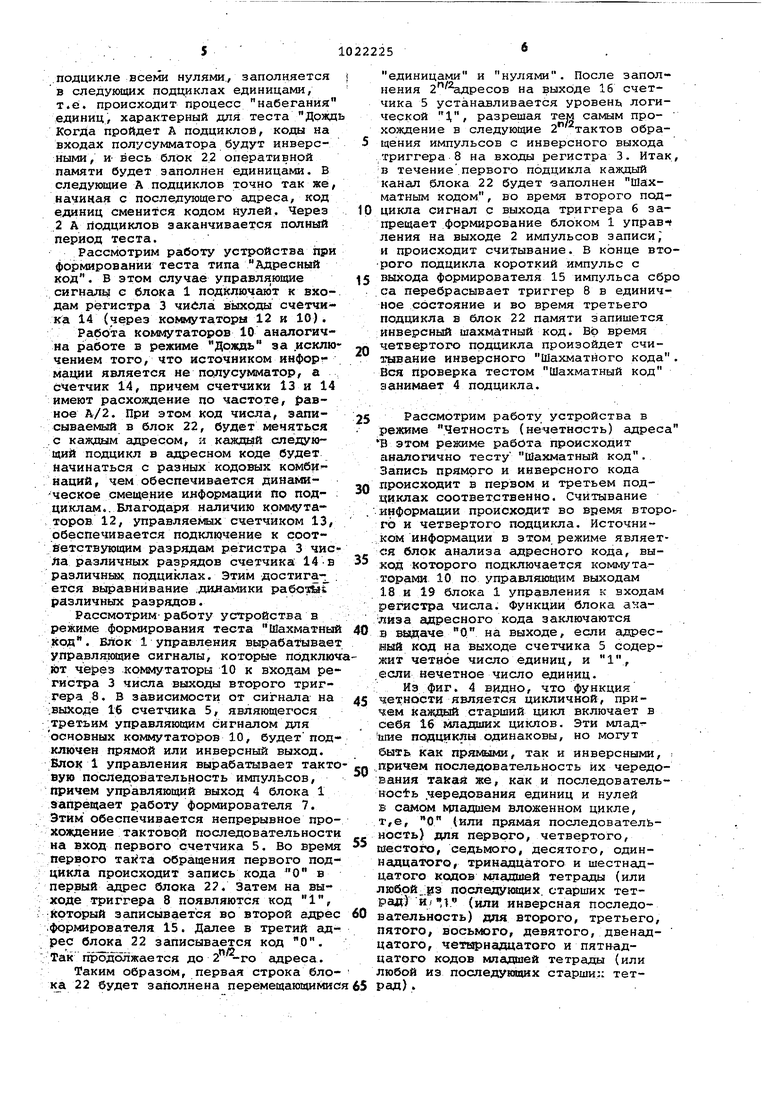

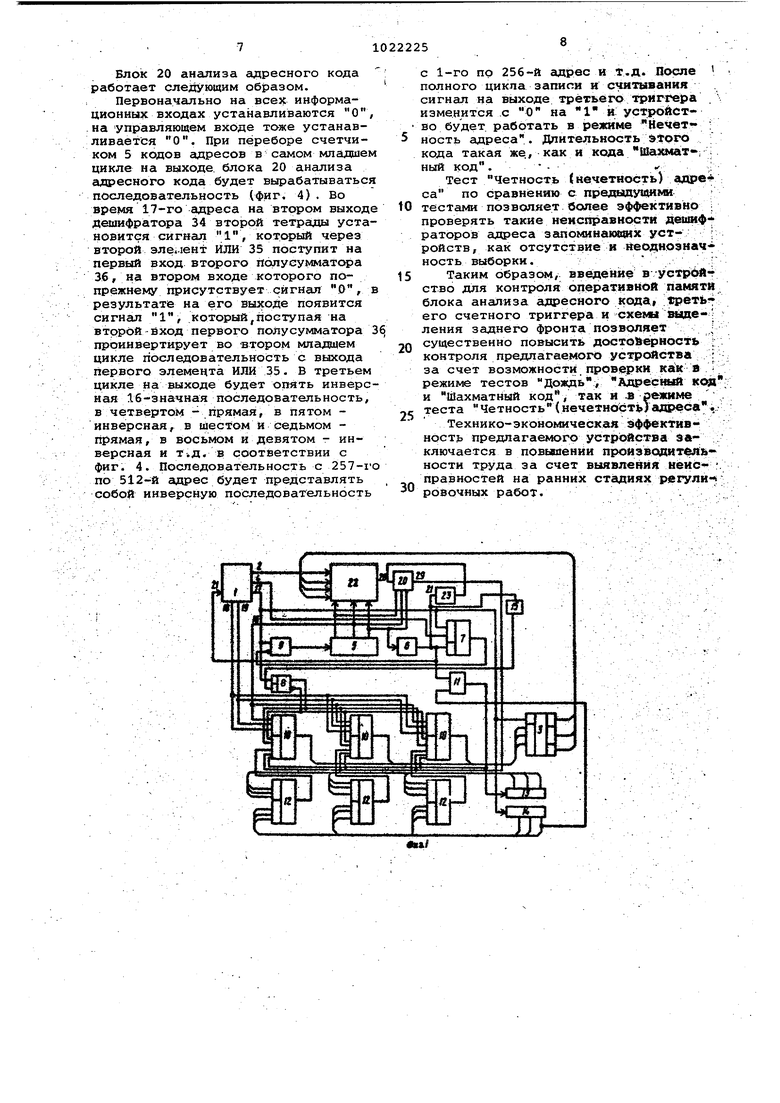

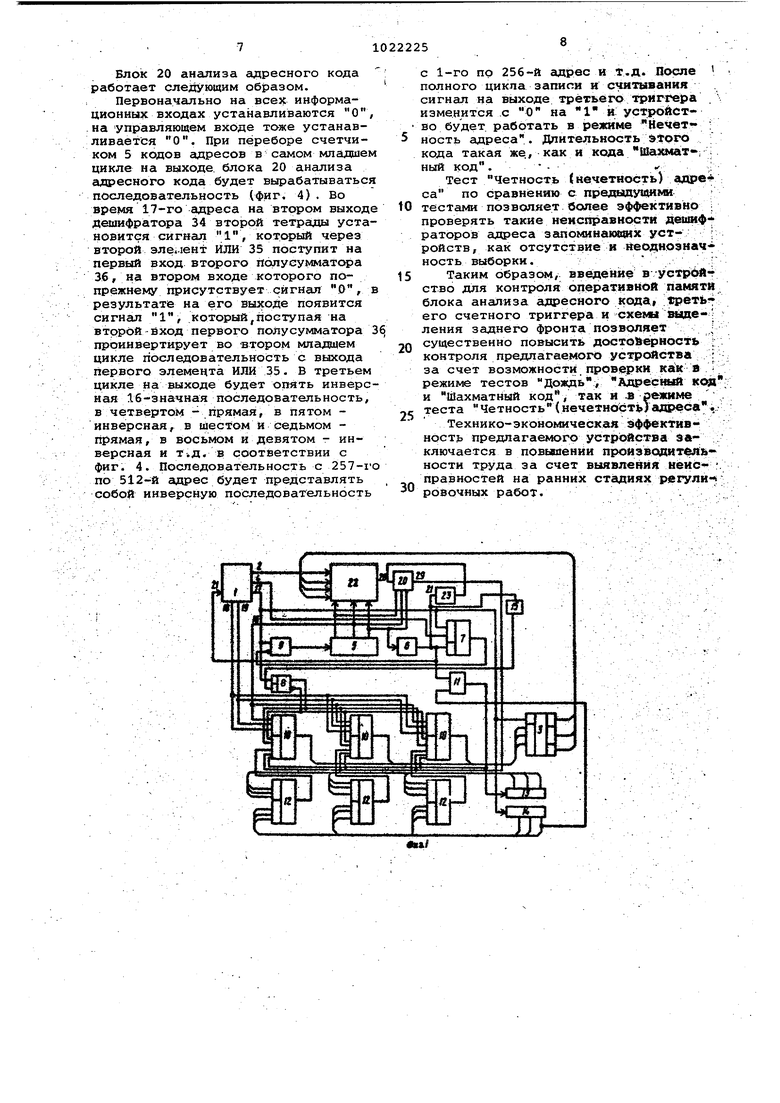

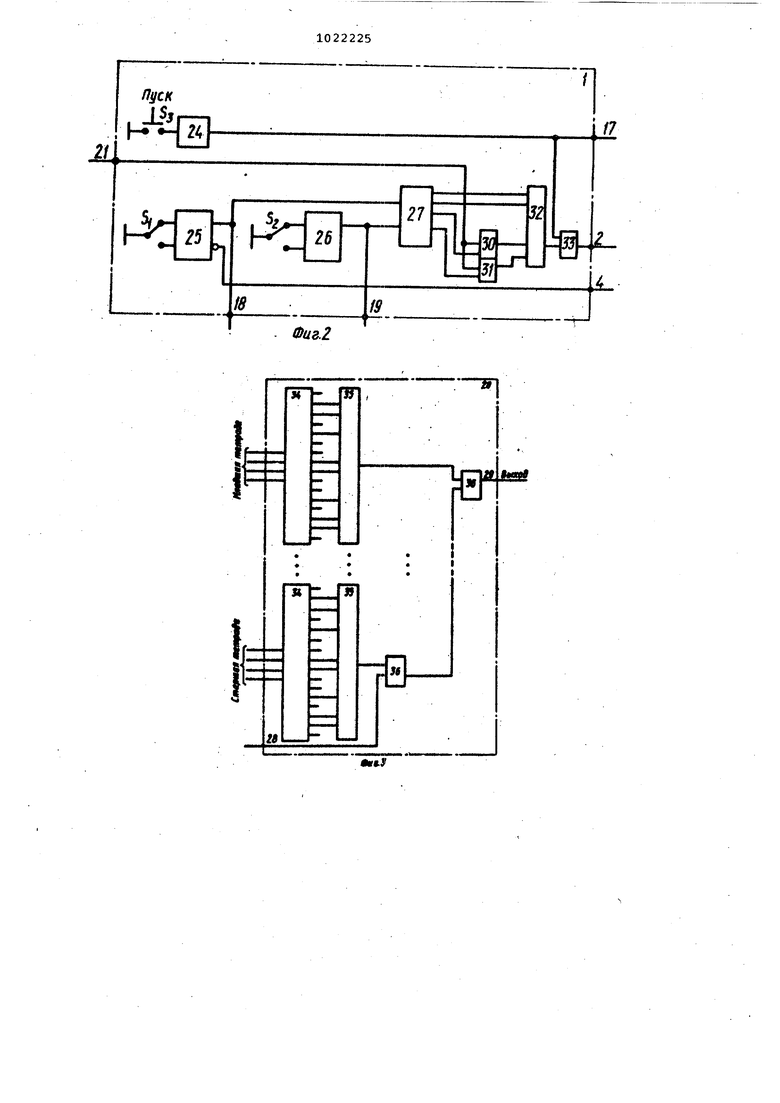

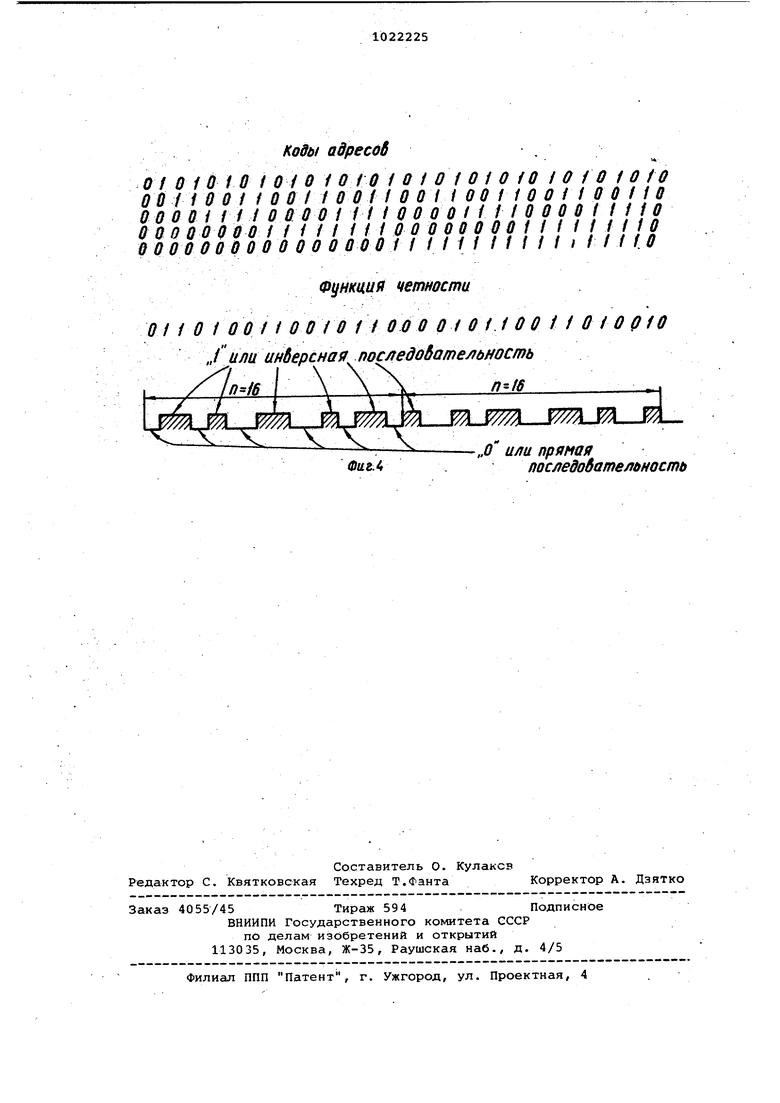

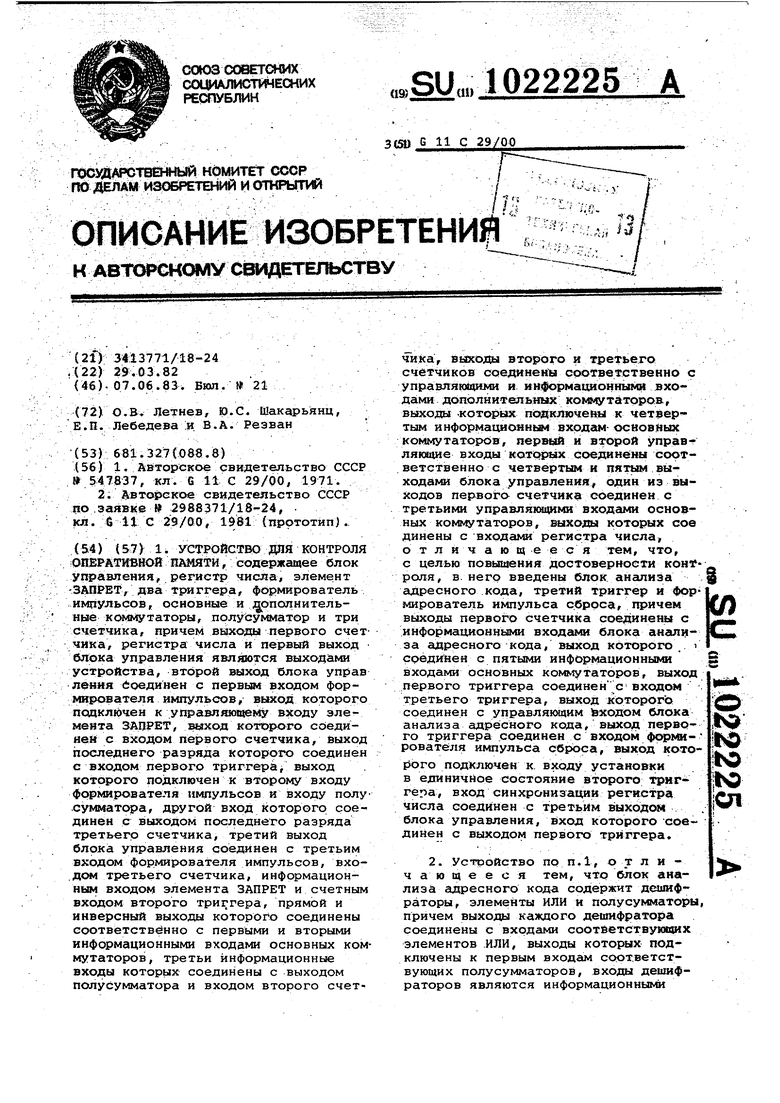

Блок анализа ещресного кода содержит дешифраторы, элементы ИЛИ и полусумматоры, причем выходы каждого дешифратора соединены с входами соответствующих элементов ИЛИ, выходы которых подключены к первым входам соответствующих полусумматоров, входы дешифраторов являются информационными входами блока анализа адресного кода, выход первого и второй вход пос леднего полусумматоров являются соот ветственно выходом и управляющим входом блока анализа адресного кода, второй вход каждого полусумматора соединен с выходом последующего полу.сумматора. На фиг. Г показана функциональная схема устройства для контроля оперативной памяти; на фиг. 2 - схема блока управления; на фиг. 3 - функциональная схема блока анализа адресного кода; на фиг. 4 - коды адресов счетчика и функция четности. Устройство содержит блок 1 управл ния с первым выходом 2, регистр 3 чк ла, второй выход 4 блока управления, первый счетчик 5, первый триггер 6, формирователь 7 импульсов, второй триггер 8, элемент ЗАПРЕТ 9, основные коммутаторы 10, полусумматор 11, дополнительные коммутаторы 12, второй 13 и третий 14 счетчики, формиро ватель 15 импульса сброса, ( + 1)-й выход 16 первого счетчика, соединенный с одними -из управляющих входов основных коммутаторов, третий выход 1 блока 1 управления, являющийся выходом тактовых импульсов, четвертый 18 и пятый 19 выходы блока 1 управления, блок 20 анализа адресного кода, i выход первого триггера, соединен ный с первым входом 21 Ьлока 1 управ ления, блок 22 оперативной памяти, триггер 23, задающий генератор 24. Триггеры 25 и 26, служащие для устра нения дребезга, дешифратор 27 кода - выбранного теста, информационный вход 28 и выход 29 блока анализа адресного кода, элементы И 30-31, элемент ИЛИ 32, элеме нт- И 33, дешифраторы 34, элементы Или 35, полусумматоры 36. Первый счетчик 5 имеет разрядност А., где А - количество адресов. Он обеспечивает формирование ко дов адресов. Формирователь 7 обеспечивает выделение по заднему фронту сигнала импульса длительностью в один период тактовых импульсов. Формирователь 15 импульса сброса обеспе чивает формирование по заднему фронт сигнал короткого (сбросового) импуль са. В качестве ёгб может быть исполь зован, например, элемент 134 ЖЛ1. Второй счетчик 13 предназначен для подсчета подцикла. Третий счетчик 14 обеспечивает формирование теста типа Адресный -код. Его разрядность равна (п+1).Блок 20 анализа адресного кода содержит по числу тетрад .кода первого счетчика 5 дешифраторы 34, элементы ИЛИ 35, полусут маторы 36. Если разрядность кода первого счетчика содержит не целое число тетрат, то количество каждых вышеперечисленных элементов увеличивается до ближайшего большего. Для 12-разрядных адресных шин запоминающих устройств емкостью 4096 бит (565РУ1) это число равно трем. Таким же оно будет и для емкости памяти 1024 бит (10 адресных шин) Входал дешифраторов являются информационными входами блока анализа адресного кода, второй, третий, пятый, восьмой, девятый, двенадцатый, четырнадцатый и пятнадцатый выходы каждого дешифратора соединены с входами соответствующих элементов ИЛИ выходы которых подключены k первым входам соответствукяцих полусумматоров, выход первого и второй вход последнего полусумматоров являются соответственно выходом и управляющим входом блока анализа адресного кода, второй вход каждого полусумматора соединен с выходом последующего полусумматора. Устройство работает следующим образом. Сигналы на управляющих выходах 18 и 19 блока 1 управления обусловливают выбор одного из четырех применяемых в устройстве контрольных тестов: Дождь, Адресный код, Шахматный код и Четность (нечетность). адреса (соответственно коды 00, 01, 10, 11). Перед запуском устройства происходит обнуление всех элементов с памятью (цепи обнуления условно не показаны). Рассмотрим работу устройства в режиме Дождь. При этом источником информации, записываемой в регистр 3, является полусумматор 11. Генератор 24 начинает вырабатывать тактовую последовательность импульсов. При этом на входах полус мматора 11 код . одинаковый, а на его выходе низкий уровень, соответствующий записи кода О по всем адресам.. По окончании первого подцикла формирователем 7 чмпульсов вьщеляется защний фронт сигнала с выхода триггера 6 и производится запрет (в элементе ЗАПРЕТ.9) продвижения одного импульса в счетчик 5. В -результате второй подцикл в счетчике 5 закончится на сздин такт (равный периоду обращений) позже, чем в счетчике 14, и полусумматор 11 зафиксирует неравнозначно.сгь в конце второго подцикла. Поэтому во втором подцикле во всех адресах памяти, кроме последнего, будут записаны коды О, а в последнем - код 1. Таким образом, блок 22 оперативной памяти, заполненный в первом .подцикле всеми нулями., заполняется в следующих подциклах единицами, Т4е. происходит процесс набегания единиц, характерный для теста Држд Когда пройдет А подциклой, коды на входах полусумматора будут инверсными, и- весь блок 22 оперативной памяти будет заполнен единицами. В следующие А прдциклов точно так же, начиная с последующего адреса, код единиц сменится кодом йулей. Через 2 А йрдциклов заканчивается полный период теста. Рассмотрим работу устройства при формировании теста типа Адресный код. В этом случае управляющие сигналы с блока 1 подключают к входам регистра 3 чиОла в ыхрды счетчика 14 {через ко1умутаторы 12 и 10). Работа коммутаторов 10 аналогична работе в режиме Дождь за .исклю чением тргр, что источником инфоргмации является не полусумматор, а счетчик 14, причем счетчики 13 и 14 имеют расхрждение ПР частрте, равное А/2. При этом код числа, записываемый в блок 22, будет меняться .с каждым адресом, и каждый следующий подцикл в адресном коде будет начинаться с разных кодовых коМби наций, чем обеспечивается динамическое смещение информации по подциклам.. Благодаря наличию коммутаторов 12, управляемых счетчиком 13, обеспечивается подключение к соотйетствующим разрядам регистра 3 чис ла различных разрядов счетчика 14-в различных подциклах. Этим достигав ется выравнивание .динамики различных разрядов. Рассмотрим-работу устройства в регкиме формирования теста Шахматный .код. ErtOK 1 управления вырабашвает управлякадие сигналы, которые подключ ют через коммутаторы 10 к входам регистра 3 числа выходы второго тригТера .8. В зависимости от сигнала иа .выходе 16 счетчика 5, являющегося .третьим управляющим сигналом для основных коммутаторов 10, будет подключен прямой или инверсный выход. Блок 1 управления вырабатывает такто вую последовательность импульсов, причем управляющий выход 4 блока 1 Запрещает работу формирователя 7. Этим обеспечивается непрерывное прохождение тактоврй последовательности на вход первого счетчика 5. Во время первого обращения первого подцикла происходит запись кода О в первый адрес блока 2. Затем на выходе триггера 8 появляются код 1, который записывается во второй адрес .формирователя 15. Далее в третий адрес блока 22 записывается код О. , ,« Так продолжается до 2 -го адреса. Таким образом, первая строка блока 22 будет заполнена перемещающимис единицами и нулями, После заполнения 2 адресов на выходе 16 счетчика 5 устанавливается уровень логической ,, разрешая тем самым прохождение в следующие 2 тактов обращения импульсов с инверсного выхода триггера 8 на входы регистра 3. Итак, в течение .первого подцикла каждый канал блока 22 будет заполнен Шахматным кодом, во время второго подцикла сигнал с выхода триггера 6 запрещает формирование блоком 1 управ- ления на выходе 2 импульсов записи, и происходит считывание. В конце второго подцикла короткий импульс с выхода формирователя 15 импульса сбро .са перебрасывает триггер 8 в единичное состояние и во время третьего подцикла в блок 22 памяти запишется инверсный шахматный код i Bip время четвертого прдцикла произойдет счиэгывание инверсного Шахматного кода . Вся проверка тестом Шахматный код занимает 4 подцикла. Рассмотрим работу устройства в режиме .Четность (нечетность) адреса В этом режиме работа происходит аналогично тесту Шахматный код . Запись прямрго и инверсного кода происходит в первом и третьем подциклах соответственно. Считывание информации происходит во время второгЬ и четвертого подцикла. Источником информации в этом режиме является блок анализа адресного кода, выкод которого подключается коммутаторами 10 по управляющим выходам 18 и 19 блока 1 управления к входам регастра числа. Функции блока анаЛйэа адресного кода заключаются э выдаче О на выходе, если адресный код на выходе счетчика 5 содержит четное число единиц, и 1, если нечетное число единиц. Из фиг. 4 видно, что функция четности является цикличной, причем каждый старший цикл включает в себя 16 младших циклов. Эти младише псщцикпы одинаковы, но могут быть как прямыми, так и инверсными, . причем последовательность их чередования такая же, как и последовательность .чередования единиц и нулей Б самом кщадшем вложенном цикле, т,е, О (или прямая последовательность) для первого, четвертого, шесто1Ч, седьмого, десятого, одиннадцатого, тринадцатргр и шестнадцатого кодов младшей тетрады (или люб;Ой ;рз последующих, старших IQT: рад)й) (или инверсная последовательность) для второго, третьего, пятого, восьмого, девятого, двенадцатого, четЕфнадцаторо и пятнадцатого кодов младшей тетрады (или любой из последукяцих старши:: тетрад) .

Блок 20 анализа адресного кода работает следующим образом.

Первоначально на всех информационных входах устанавливаются О, на управляющем входе тоже устанавливается О. При переборе счетчиком 5 кодов адресов в самом младшем цикле на выходе блока 20 анализа адресного кода будет вьарабатываться последовательность (фиг. 4). Во время 17-го адреса на втором выходе дешифратора 34 второй тетрады установится сигнал 1, который через второй эле.лент ИЛИ 35 пос1упит на первый вход второго полусумматора 36, на втором входе которого попрежнему присутствует сигнал О, в результате на его выходе появится сигнал 1, который,поступая на второй вход первого полусумматора 3 проинвертирует во втором мдадацем цикле последовательность с выхода первого элемента ИЛИ 35. В третьем цикле на выходе будет опять инверсная 1б-значная последовательность, в четвертом - прямая, в пятом инверсная, в шестом и седьмом прямая, в восьмом и девятом - инверсная и т-.д. в соответствии с фиг. 4. Последовательность с 257-iO по 512-й адрес будет представлять собой инверсную последовательность

с 1-го по 256-й адрес и т.д. После полного цикла записи и считывания сигнал на выходе третьего триггера изменится с О на 1 И устройство будет работать в режиме Нечетность адреса. Длительность эТрго кода такая же., как и кода Шахмат-; ный код. -,

Тест Четность (нечетность) адре са по сравнению с предыдущими

тестами позволяет более эффективно проверять такие неисправности дешифраторов адреса запоминаклих устройств, как отсутствие и йеоднозначность выборки.

Таким образом, введение в/устрбйство для контрюля оперативной naMHTti блока анализа адресного коуца, №еть его счетного триггера и схемы оаделения заднего фронта позволяет

существенно повысить достойерность контроля предлагаемого устройства за счет возможности проверки как В

АдресшА код

режиме тестов Дождь

и Шахматный код, так и л режиме теста Четность(нечетности)адреса .

25

Технико-экономическая Эффективность предлагаемого устройства эа- ; ключается в повыаенйи производитейьности труда за счет выявления :. правностей на ранних стадиях регули30ровочных работ.

Пуск ISj 24

1

.

Коды адресоб

..- .

Of О 10 i о 101 о 1 о to 1 и 1 о 1 о 1 о 10 I о 1 о 1 о 10 001 1 и 01 1 о о ft о о 11 о 011 0011001100110 00001 111 о 0001 11100001111000011110 00000000 11 111 111 00000000111111110 о 000000 000 о о 00001 1 1 1 1 1 1 1 I 1 1 ) 1 11 1.0

функция четности

01 10 100110010 11 000 Of 01100 11010010 J им инЬерсная последовательность

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке 2988371/18-24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-06-07—Публикация

1982-03-29—Подача