ю

00 со со

со

Iuj.r.uo;; 11л::ап- ке и может бьпЬ vicjiojihзг ::ано ;уи отработке оборудования i; ;;|,-огйамь1 ; чьпюликюи их контроль и

U.c;j ь i :;;i 6ut;-v2K)if; - лояьп11е; ие на

;г:VTffj ч - .(.: ппйс: -;м яй бло).

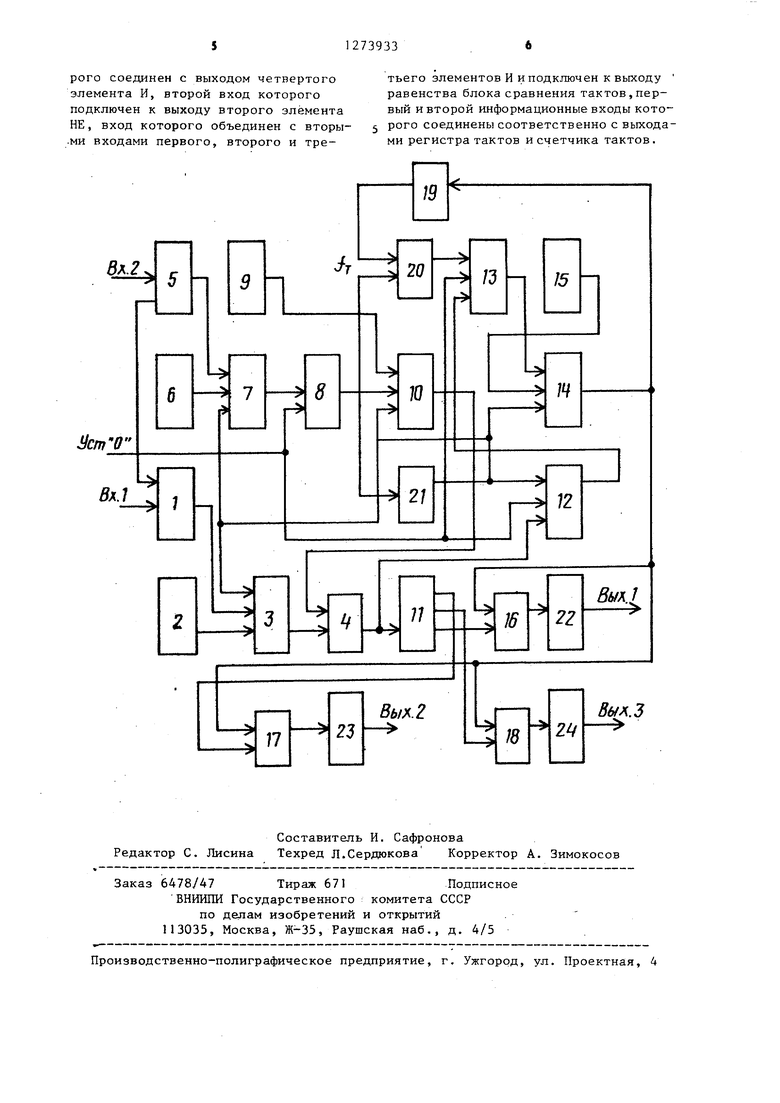

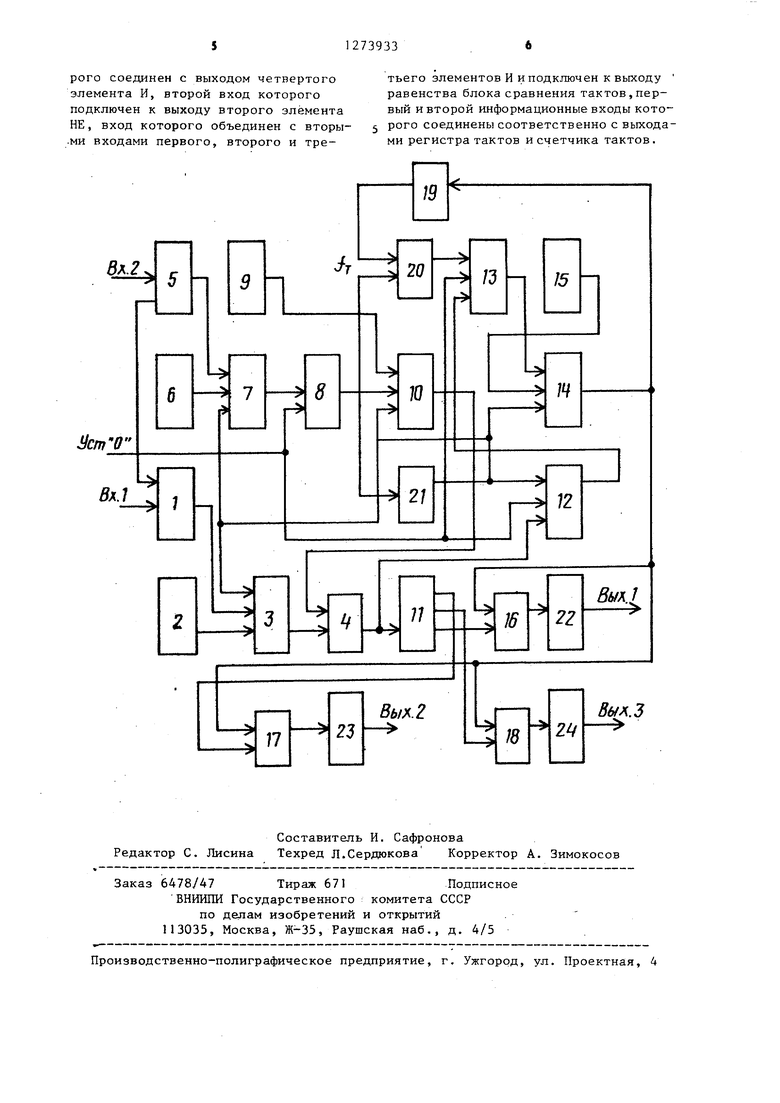

Устройство для имитации неисттрувностей содержит первый и второй регистры адреса 1 и 2, соединенные с бло) 3 сравнения адресов, который BbixcvioM соединен с входом элемента ИЛИ А, первый и второй регистръ кода 5 и 6, соединенные с блоком 7 сра}знения кодов, счетчик 8 циклогг:,, регистр 9 циклов, соединеннье е блоком 10 сравнения циклов, который выходом соединен с вторым входсг.-- ;эле.1ента ИЛИ 4, выход которого пслтключен к и ншрато1)у 1 1 неисправ- HOCieiJ и к входу разрешения триггера 2, иы;чод которого соед,инен е Бходом разрешения счетчика 13 тактов, выходом соединенного с входом блока 14- сравнения тактов, вторым 13ХОДОМ соединеннсго с регистром 15 тактоз. а вь ходо - - с входами выходных элементов И б-18 и элемента НЕ 19 5 Бьп;одом с:оедипенного с входом элемента И 20., выходом соединенного со счетным входом счетчика 3 тактов а вторым входом, который является тактоЕым входом устройства; с входом второго элемеьгга НЕ 2, выходом подключенното к вг:одак еиихронизации блока 14 сравнения тагстов, триггера i2. блока 10 сравнения циклов, блока 3 сравнения адресов и блока 7 срав1 ения кодов, выход которого подключен к входу счетчика циклов 8, вход обнуления которого подключен к обнуляющим входам первого регистра адреса 1, первого регистра кода 5, счетчика 13 тактов, триггера 12 и является входом начальной установки устройства, причем выходы шифратора 11 неисправностей подключены к вторым входам соответствующих выходных элементов И 16-18, выходы которых соединены соответственно с первым и вторы формирователями 22 и 23 сигналов ;Неисправностей и формирователем 24 импульсов, выходы которых являются

ir.::::i,j;-JM ; слгпалов неисправности устройства. .

УстрО1;Ство работает слецуюним образом ,

Цтп; ио.7отовке vcTiortvi ва к рабо - чс группл ад1тес1плх иходов ит&рого peiHCTpa 2 a,ripeca до/п-слтсчается к передачи адреса ко.1анд, руппа н;формационных входов второго регистра 6 кода, подключаетея к п.еплм передачи кодовых слов, тактовый вход устройства подключается к генератору тактовой частоты, а вход обнуления к устройству обнуления или к управляющему выходу ЦВМ. Выходы устройства подключаются к выбранной точке схемы ЦВМ или к внешним евязям ЦЕМ, в которых необходимо имргтировать неисгравность. В исходном состоянии регистры 1 и 5 счетчиков 8 и 13 и триггер 12 обнулены.

Для внесения определенной неисправности в необходимом такте по заданному адресу или коду в нужном цикле устанавливаются начальные ус лозгкя;- ПС втором регистре 2 адреса ;-;:t:jec команды во втором ретиегре 6 кода - код слова, в регистре 15 тактон - количество i/aKToa в шифраторе 1 1 неиспрагдо:-тей - неисправности. , условия задаются гумблерамг .-u y-;Hyio nepe,j, началом рабо ты„

п;)с.Паммъ1 в опре,-.:е;-;и 3 первый 1насывается адрес - -:еанному во второй регистр 2 адреса, Ка выходе блока 3 сравнения адреса появляется сигна.} сравнения, который через элемен 1ШИ 4 поступает на. шифратор ;;:i- исправности, подготавливая те;.; самым внесение опреде:1енного и.;,а неисправности и на триггер 12 - который по сигналу тактовой частоты во второй половине периода переключается в единичное состояние, после чего счетчик 13 тактов начинает считать сигналы тактовой чз..

В случае равенства количества тактов в счетчике 13 тактов и в регистре Ь тактов блок 14 сравнения такгов выдает сигнал, поступающий через элемент НЕ 19:на элемент И 20, за.прещая тем сам1з1м прохождение сигналов тактовой частоть на счетчик 13 тактов 5 и одновременно поступает на вглходные элементы И 16-18, разрешая тем оабсту олиого нз ({)Орьп1рователей 2/., 2Г) ujiii формирователя 24 импульсов. При поступлении сигнала с шифратора 1 1 яеггсправности на вы I . ( II 16 срабатывает пер г т J jif 22 неисправности э Il 1 I м (i I в цепи; при поступлении сигнала на выходной элемент 1117 срабатывает второй формирователь 23 нелсправности, имитирующий замыкание. Ilpi-i поступлении сигнала на выходной элемент И 18 срабатывае формирователь 24 импульсов, имитирующий одиночный импульс с уровнем логического нуля, что воспринимается как неисправность в данной точке (уровень логической единицы заменяется уровнем логического нуля) . Пос ле этого устройство приводится в ис ходное состояние и подготавливается к очередном, заданию неисправности. При поступлении с регистра 5 код кодового слова, совпадающего с кодо занесенным в регистр 9, блок сравнения кодов выдает сигнал, подсчиты ваемый счетчиком циклов. При равенстве количества совпадений состояний регистров 5 и 6, подсчитанных счетчиком циклов 8, и количества ЦИКЛОВ; занесенного в регистр циклов 9, блок 10 сравнения циклов выделяет сигнал сравнения, который через элемент Ш1И 4 поступает на шифратор 11 неисправности и триггер 12. В дальнейшем работа устройства происходит аналогично случаю совпадения адресов. После появления одного из сигналов совпадения на элементе ИЛИ 4 появление второго сигнала совпадения не изменяет работы устройства, так как триггер 12переключается от воздейстБия пер вого сигнала совпадения и остается в единичном состоянии до прихода обнуляющего сигнала. Формула изобретени Устройство для имитации неисправ ностей, содержащее первый и второй регистры кода, блок сравнения кодов первый и второй регистры адреса, блок сравнения адресов, регистр цик лов, счетчик циклов, блок сравнения циклов, счетчик тактов, регистр так тов, Tpvirrep, блок сравнения тактов три элемента И, два формирователя сигнала неисправности, формировател импульсов, элемент ИЛИ, шифратор неисправностей, причем информациоиньй вход первого регистра кода подключен к информапионному входу устройства, выходы первого и второго регистров кода соединены соответственно с первым и вторым информационными входами блока сравнения кодов, выход равенства которого подключен к счетному входу счетчика циклов, выход которого соединен с первым информационным входом блока сравнения циклов, второй информационный вход которого соединен с выходом регистра циклов, информационный вход первого регистра адреса подключен к адресному входу устройства, выход первого регистра адреса соединен с первым информационным входом блока сравнения адресов 5 второй информационный вход которого соединен с выходом второго регистра адреса, входы сброса счетчика циклов, триггера, счетчика тактов первого регистра кода, первого регистра адреса объединены и подключены к входу начальной установки устройства, выходы шифратора неисправностей подключены к первым входам соответственно первого, второго и третьего элементов И, выходы которых подключены к входам соответственно первого, второго формирователей сигнала неисправности и формирователя импульсов, выходы которых являются соответственно первым, вторым и третьим выходами сигналов неисправности устройства, отличающееся тем, что, с целью повышения надежности за счет блокировки совместного задания неисправностей по различным каналам, в него введены два элемента НЕ, четвертый элемент И, причем тактовьш вход устройства подключен к первому входу четвертого элемента И и входу первого элемента НЕ, выход которого соединен .с синхровходом триггера, с входами разрешения сравнения блоков сравнения кодов, тактов, адресов, ЦИКЛОВ, вход разрешения триггера объединен с входом шифратора неисправностей и подключен к выходу элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами блока сравнения циклов и блока сравнения адресов, выход триггера соединен со счетным входом счетчика тактов, тактовый вход кото-

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для имитации неисправностей | 1984 |

|

SU1164715A1 |

| Устройство для имитации неисправностей | 1985 |

|

SU1283775A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1536387A1 |

| Устройство для контроля цифровых блоков | 1983 |

|

SU1182540A1 |

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Устройство для контроля последовательности сигналов | 1987 |

|

SU1462493A1 |

| Устройство для сопряжения электронной вычислительной машины с каналами связи | 1983 |

|

SU1129599A1 |

| Устройство для отладки программ | 1980 |

|

SU922753A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1983 |

|

SU1115108A1 |

Изобретение относится к области вычислительной техники и может быть использовано при отработке оборудования и программ, выполняющих контроль и диагностирование неисправностей. Целью изобретения является повышение надежности за счет блокировки совместного задания неисправностей по различным каналам. Устройство содержит два регистра адреса, блок сравнения адресов, элемент ИЛИ, два регистра кода, блок сравнения кодов, счетчик циклов, регистр циклов, блок сравнения циклов, шифратор неисправностей, счетчик тактов, блок сравнения тактов , регистр тактов, четыре элемента И, два элемента НЕ, триггер, два формирователя сигнала неисправности, формирователь импульсов, 1 ил.

| Устройство для контроля цифровых блоков | 1981 |

|

SU1037259A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для имитации неисправностей | 1984 |

|

SU1164715A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-11-30—Публикация

1985-02-28—Подача