(Л С

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь последовательного кода в параллельный | 1985 |

|

SU1262732A1 |

| Устройство для магнитной записи цифровой информации | 1982 |

|

SU1037337A1 |

| Устройство для формирования тестовой последовательности | 1984 |

|

SU1218389A1 |

| Устройство для индикации | 1984 |

|

SU1243017A1 |

| Устройство магнитной записи сигналов цифровой информации | 1983 |

|

SU1157566A1 |

| Преобразователь последовательного кода в параллельный | 1988 |

|

SU1656685A2 |

| Устройство для воспроизведения информации с магнитного носителя | 1981 |

|

SU1014017A1 |

| Устройство для воспроизведения видеосигнала | 1982 |

|

SU1069189A1 |

| Преобразователь синусоидальных сигналов перемещения в код | 1984 |

|

SU1234968A1 |

| Устройство для сопряжения электронной вычислительной машины с каналами связи | 1983 |

|

SU1113790A1 |

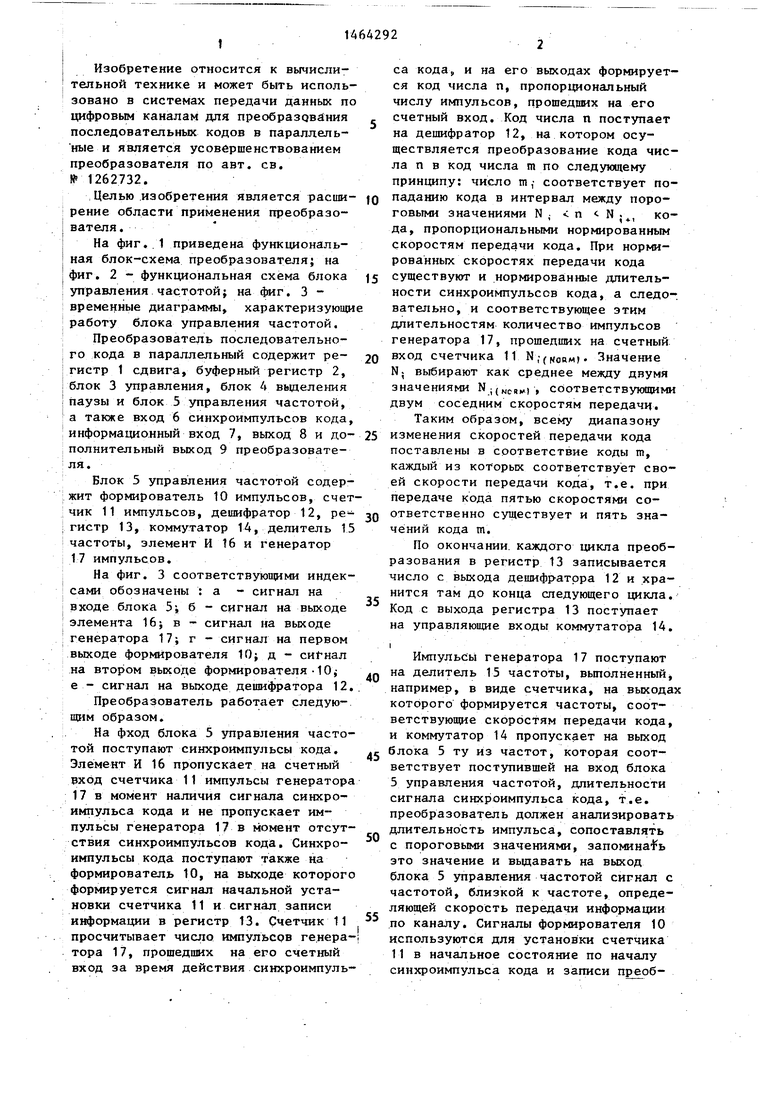

Изобретение относится к вычислительной технике и может быть использовано в системах передачи данных по цифровым каналам для преобразования последовательных кодов в параллельные. Изобретение позволяет путем введения многоскоростного приема информации расширить область применения преобразователя. Преобразователь последовательного кода в параллельный содержит регистр 1 сдвига, буферный регистр 2, блок 3 уп- . равления, блок 4 вьщеления паузы и блок 5 управления частотой, содержащий формирователь импульсов, счетчик импульсов, депифратор регистр, коммутатор, делитель частоты, элемент И и генератор импульсов. 2 з.п, ф-лы, 3 ил.

-5

9

ГО

Фиг./

Изобретение относится к вычислительной технике и может быть использовано в системах передачи данных по цифровым каналам для преобразования последовательных кодов в параллель- ные и является усовершенствованием преобразователя по авт. св. № 1262732.

Целью изобретения является расширение области применения преобразователя .

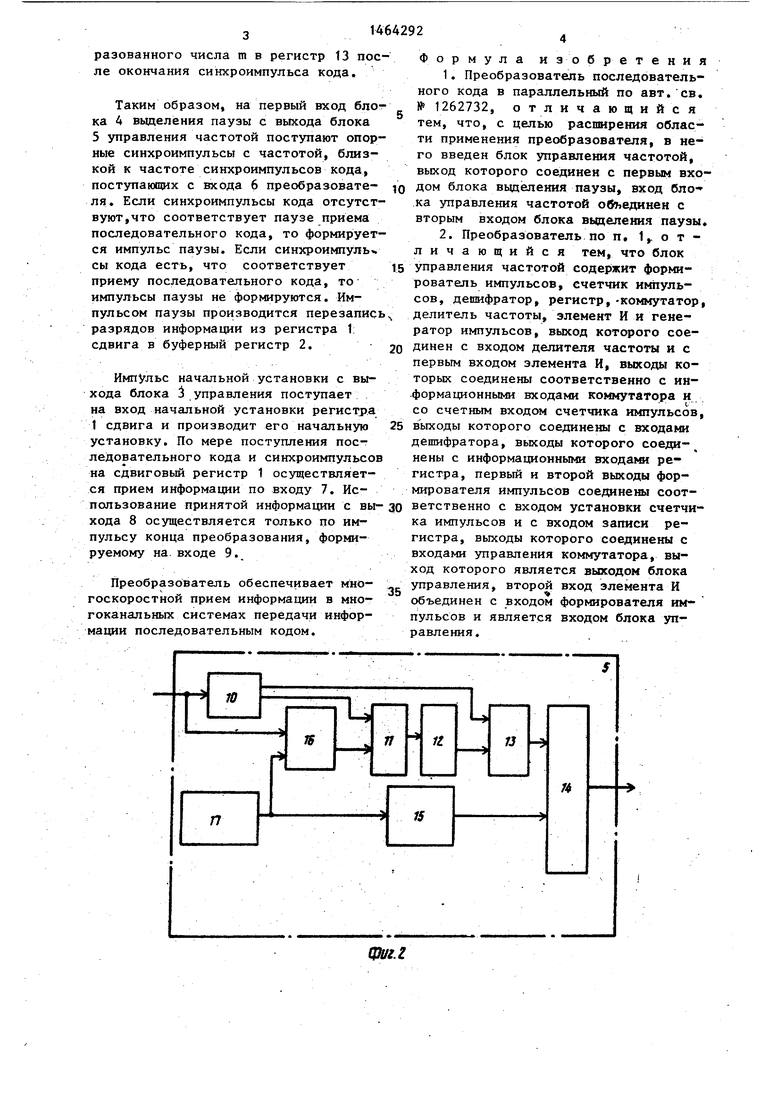

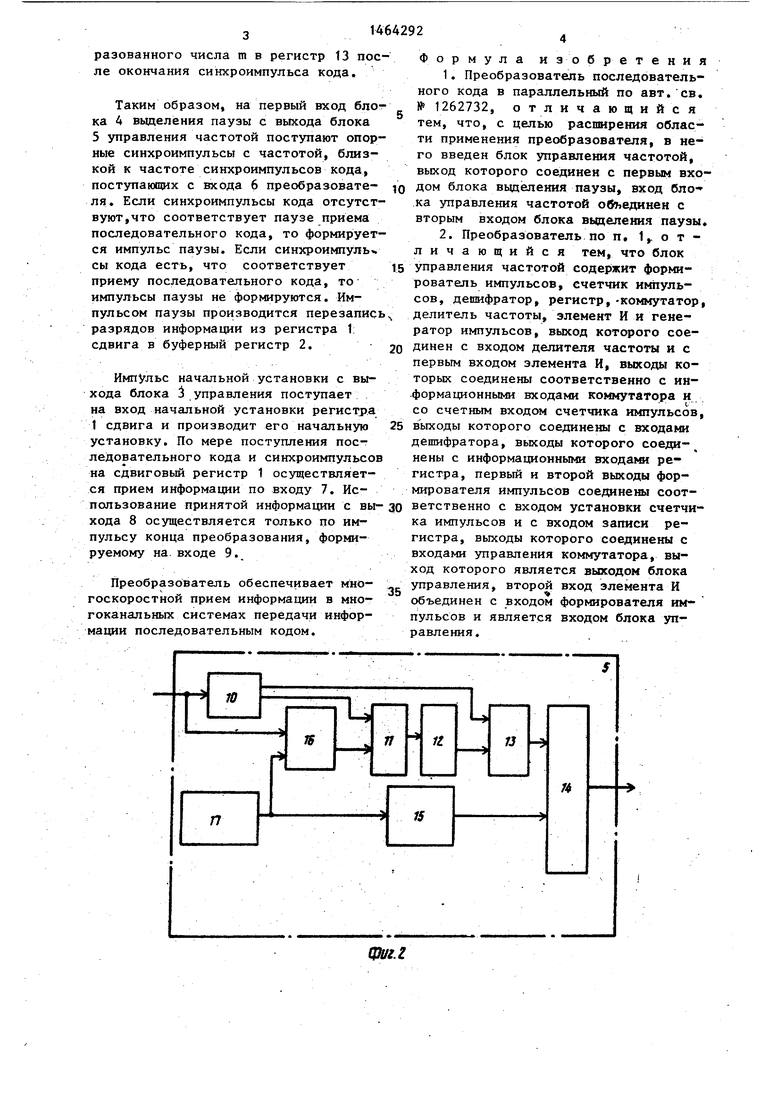

На фиг. 1 приведена функциональная блок-схема преобразователя; на фиг. 2 - функциональная схема блока I управления частотой; на фиг. 3 - временные диаграммы характеризующи работу блока управления частотой.

Преобразователь последовательно- I го кода в параллельный содержит ре- i гистр 1 сдвига, буферный регистр 2, {блок 3 управления, блок 4 выделения I паузы и блок 5 управления частотой,

а также вход 6 синхроимпульсов кода, : информационный вход 7, выход 8 и дополнительный вькод 9 преобразователя.

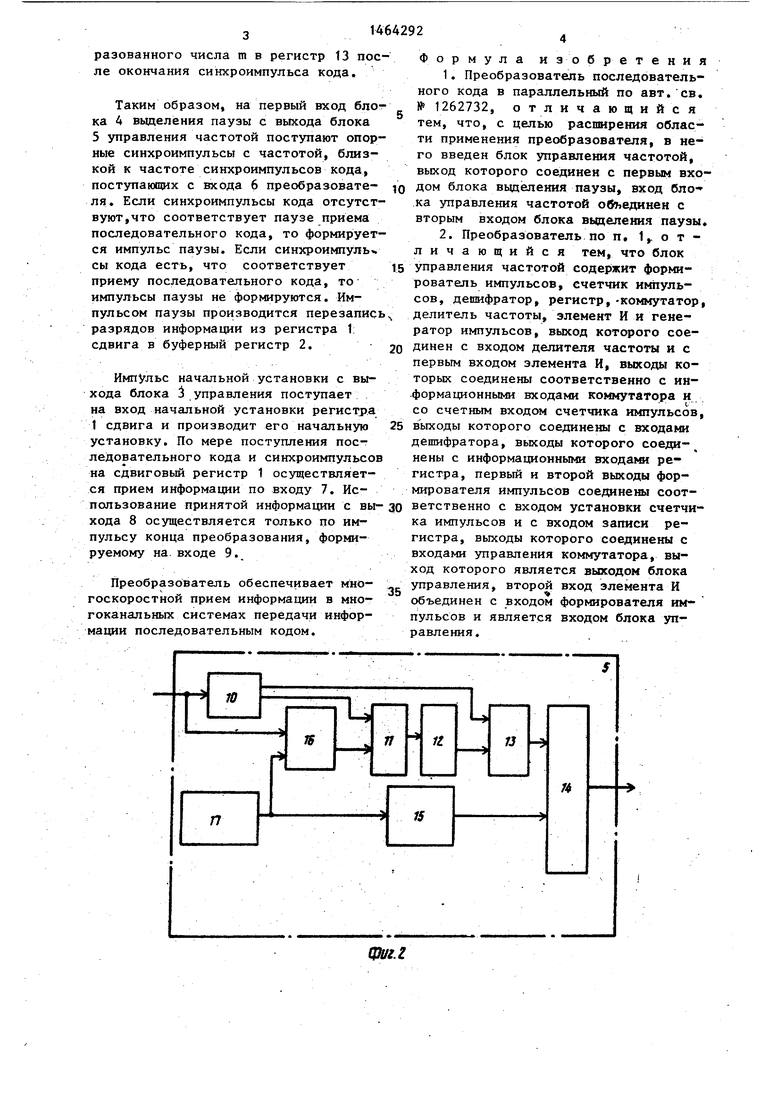

Блок 5 управления частотой содер- : жит формирователь 10 импульсов, счетчик 11 импульсов, дешифратор 12, ре- : гистр 13, коммутатор 14, делитель 15 I частоты, элемент И 16 и генератор 17 импульсов.

На фиг. 3 соответствуюп5ими индек- сами обозначены : а - сигнал на I входе блока 5; б сигнал на выходе i элемента 16j в - сигнал на выходе : генератора 17; г - сигнал на первом выходе формирователя 10; д - сигнал на втором выходе формирователя 10; е - сигнал на выходе дешифратора 12.

Преобразователь работает следующим образом.

На фход блока 5 управления частотой поступают синхроимпульсы кода. Элемент И 16 пропускает на счетный вход счетчика 11 импульсы генератора 17 в момент наличия сигнала синхроимпульса кода и не пропускает импульсы генератора 17 в момент отсутствия синхроимпульсов кода. Синхроимпульсы кода поступают также на формирователь 10, на выходе которого формируется сигнал начальной установки счетчика 11 и сигнал записи информации в регистр 13. Счетчик 11 просчитывает число импульсов генератора 17, прошедших на его счетный вход за время действия синхроимпуль-

0

5

0

5

0

5

0

5

0

5

са кода, и на его выходах формируется код числа п, пропорциональный числу импульсов, прошедших на его счетный вход. Код числа п поступает на дешифратор 12, на котором осуществляется преобразование кода числа п в код числа m по следующему принципу: число т,- соответствует попаданию кода в интервал между пороговыми значениями N , «: п N ., кода, пропорциональными нормированным скоростям передачи кода. При нормированных скоростях передачи кода существуют и нормированные длительности синхроимпульсов кода, а следо-. вательно, и соответствующее этим длительностям количество импульсов генератора 17, прошедших на счетный вход счетчика 11 N;ff,oBM). Значение N, выбирают как среднее мезвду двумя значениями N;( соответствующими двум соседним скоростям передачи.

Таким образом, всему диапазону изменения скоростей передачи кода поставлены в соответствие коды т, каждый из которых соответствует своей скорости передачи кода, т.е. при передаче кода пятью скоростями соответственно существует и пять значений кода т.

По окончании, каждого цикла преобразования в регистр 13 записывается число с выхода дешифратора 12 и хранится там до конца следующего цикла. Код с выхода регистра 13 поступает на управляющие входы коммутатора 14.

I

Импульсы генератора 17 поступают на делитель 15 частоты, выполненный например, в виде счетчика, на выходах которого формируется частоты, соответствующие скоростям передачи кода, и коммутатор 14 пропускает на выход блока 5 ту из частот, которая соответствует поступивщей на вход блока 5 управления частотой, длительности сигнала синхроимпульса кода, т.е. преобразователь должен анализировать длительность импульса, сопоставлять с пороговыми значениями, запоминать это значение и выдавать на выход блока 5 управления частотой сигнал с частотой, близкой к частоте, определяющей скорость передачи информации по каналу. Сигналы формирователя 10 используются для установки счетчика 11 в начальное состояние по началу синхроимпульса кода и записи преобразованного числа m в регистр 13 после окончания синхроимпульса кода.

Таким образом, на первый вход блока 4 вьщеления паузы с выхода блока 5 управления частотой поступают опорные синхроимпульсы с частотой, близкой к частоте синхроимпульсов кода, поступающих с исода 6 преобразователя. Если синхроимпульсы кода отсутствуют,что соответствует паузе приема последовательного кода, то формируется импульс паузы. Если синхроимпуль.. сы кода есть, что соответствует приему последовательного кода, то импульсы паузы не формируются. Импульсом паузы производится перезапись разрядов информации из регистра 1: сдвига в буферный регистр 2.

Импульс начальной установки с выхода блока 3 управления поступает на вход начальной установки регистра 1 сдвига и производит его начальную установку. По мере поступления последовательного кода и синхроимпульсов на сдвиговый регистр 1 осуществляется прием информации по входу 7. Использование принятой информации с вы- хода 8 осуществляется только по импульсу конца преобразования, формируемому на. входе 9.

Преобразователь обеспечивает м но- госкоростной прием информации в многоканальных системах передачи информации последовательным кодом.

77

20

25 О

Формула изобретения 1. Преобразователь последовательного кода в параллельный по авт. св. g № 1262732, отличающийся тем, что, с целью расширения области применения преобразователя, в него введен блок управления частотой, вькод которого соединен с первым вхо- 10 дом блока вьщеления паузы, вход бло ка управления частотой оОьединен с вторым входом блока вьщеления паузы. 2. Преобразователь по п, 1,. о т - личающийся тем, что блок 15 управления частотой содержит формирователь импульсов, счетчик импульсов, дешифратор, регистр,-коммутатор, делитель частоты, элемент И и генератор импульсов, выход которого соединен с входом делителя частоты и с первым входом элемента И, выходы которых соединены соответственно с информационными входами коммутатора и со счетным входом счетчика импульсов, в ыходы которого соединены с входами депшфратора, выходы которого соединены с информационными входаьш регистра, первый и второй выходы формирователя импульсов соединены соответственно с входом установки счетчика импульсов и с входом записи регистра, выходы которого соединены с входами управления коммутатора, выход которого является выходом блока управления, второй вход элемента И объединен с входом формирователя им- пульсов и является входом блока управления.

5

15

М1ШШШШШ

iiinmniiiiiiiiHiiiiiiiiiiiiniiiiiiiiiitniiiiiiiiiiiiiiiiiiiiiiiii

I .; / -1-II

Фиг.З

| Преобразователь последовательного кода в параллельный | 1985 |

|

SU1262732A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-03-07—Публикация

1986-12-02—Подача