Изобретение относится к вычислительной технике и может быть использовано в системах передачи данных по цифровым каналам.

Целью изобретения является повышение достоверности преобразуемой информации и расширение области прим:енения путем преобразования кода различной разрядности.

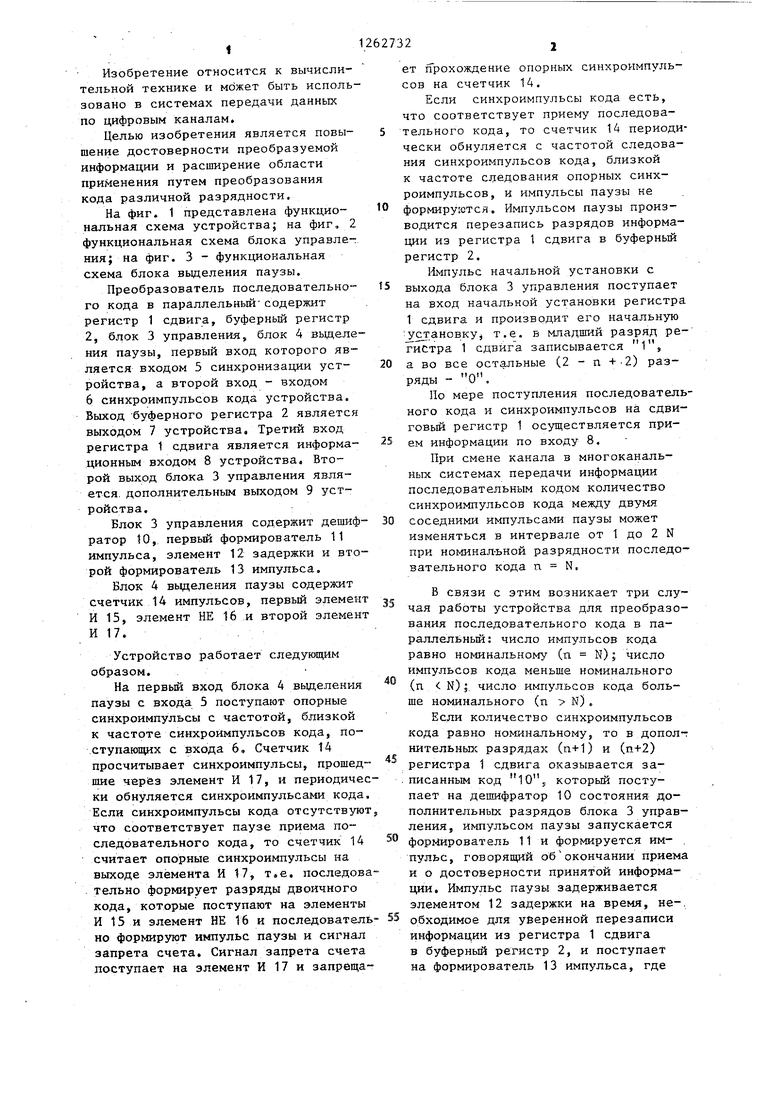

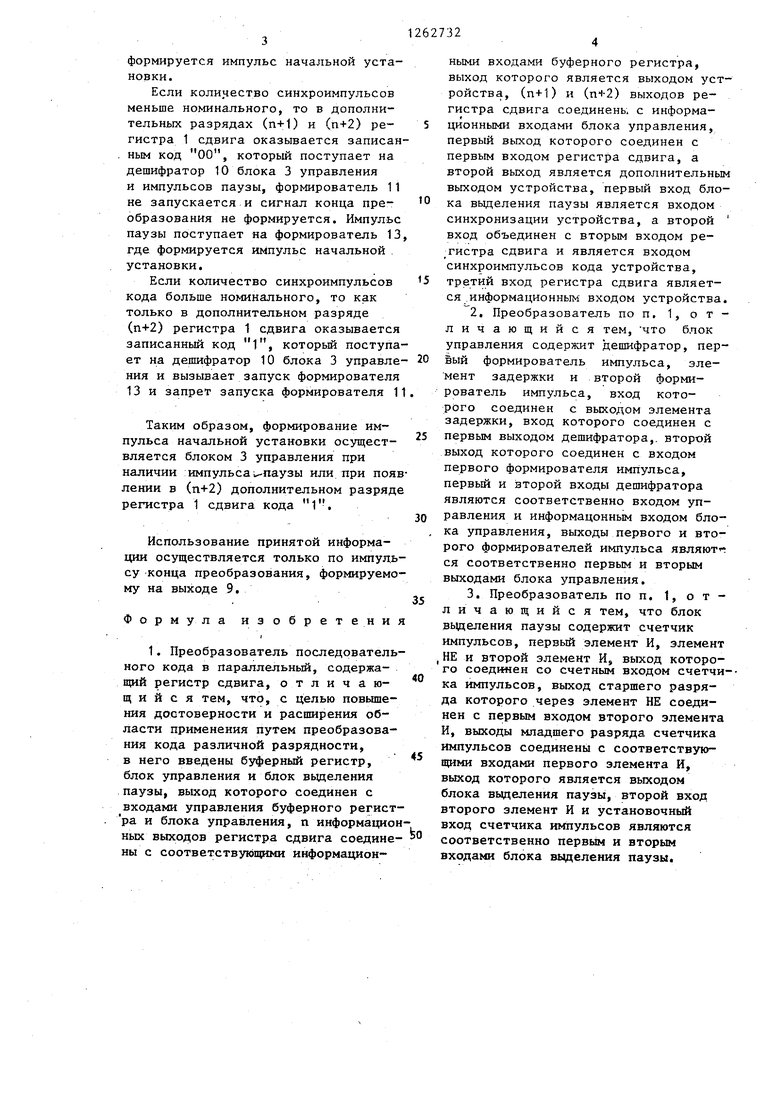

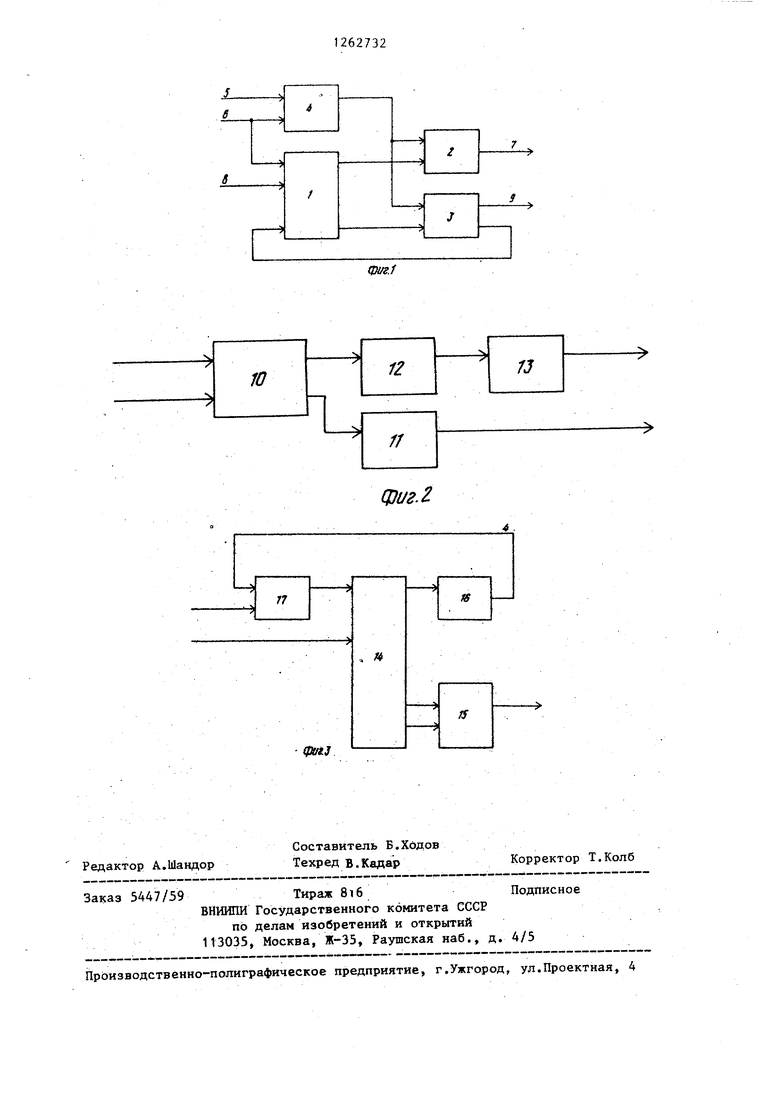

На фиг. 1 представлена функциональная схема устройства; на фиг 2 функциональная схема блока управления; на фиг. 3 - функциональная схема блока вьщеления паузы.

Преобразователь последовательного кода в параллельныйсодержит регистр 1 сдвига, буферньгй регистр 2, блок 3 управления, блок 4 выделения паузы, первый вход которого является входом 5 синхронизации устройства, а второй вход - входом 6 синхроимпульсов кода устройства. Выход буферного регистра 2 является выходом 7 устройства. Третий вход регистра 1 сдвига является информационным входом 8 устройства. Второй выход блока 3 управления является, дополнительным выходом 9 устройства.

Блок 3 управления содержит дешифратор to, первый формирователь 11 импульса, элемент 12 задержки и второй формирователь 13 импульса.

Блок 4 выделения паузы содержит счетчик 14 импульсов, первый элемент И 15, элемент НЕ 16 и второй элемент И 17.

Устройство работает следующим образом.

На первьй вход блока 4 выделения паузы с входа 5 поступают опорные синхроимпульсы с частотой, близкой к частоте синхроимпульсов кода, поступающих с входа 6, Счетчик 14 просчитывает синхроимпульсы, прошедшие черкез элемент И 17, и периодически обнуляется синхроимпульсами кода. Если синхроимпульсы кода отсутствуют что соответствует паузе приема последовательного кода, то счетчик 14 считает опорные синхроимпульсы на выходе элемента И 17, т.е. последовательно формирует разряды двоичного кода, которые поступают на элементы И 15 и элемент НЕ 16 и последователь но формируют импульс паузы и сигнал запрета счета. Сигнал запрета счета поступает на элемент И 17 и запрещает прохождение опорных синхроимпульсов на счетчик 14.

Если синхроимпульсы кода есть, что соответствует приему последовательного кода, то счетчик 14 периодически обнуляется с частотой следования синхроимпульсов кода, близкой к частоте следования опорных синхроимпульсов, и импульсы паузы не формируются. Импульсом паузы производится перезапись разрядов информации из регистра 1 сдвига в буферный регистр 2.

мпульс начальной установки с выхода блока 3 управления поступает на вход начальной установки регистра 1 сдвига и производит его начальную : У тановку т.е. в младший разряд региСтра 1 сдвига записывается 1, а во все остальные (2 - п +-2) разряды - О.

По мере поступления последовательного кода и синхроимпульсов на сдвиговьй регистр 1 осуществляется прием информации по входу 8.

При смене канала в многоканальных системах передачи информации последовательным кодом количество синхроимпульсов кода между двумя соседними импульсами паузы может изменяться в интервале от 1 до 2 N при номинал-ьной разрядности последовательного кода п N.

В связи с этим возникает три случая работы устройства для преобразования последовательного кода в параллельный: число импульсов кода равно номинальному (п N); число импульсов кода меньше номинального (п N);. число импульсов кода больше номинального (п N),

Если количество синхроимпульсов кода равно номинальному, то в дополт нительных разрядах (п+1) и (п+2) регистра 1 сдвига оказывается записанным код 10% который поступает на дешифратор 10 состояния дополнительных разрядов блока 3 управления, импульсом паузы запускается формирователь 11 и формируется импульс, говорящий об окончании приема и о достоверности принятой информации. Импульс паузы задерживается элементом 12 задержки на время, не-. обходимое для уверенной перезаписи информации из регистра 1 сдвига в буферньй регистр 2, и поступает на формирователь 13 импульса, где формируется импульс начальной установки. Если количество синхроимпульсов меньше номинального, то в дополнительных разрядах (п+1) и (п+2) регистра 1 сдвига оказывается записан ным код 00, который поступает на дешифратор 10 блока 3 управления и импульсов паузы, формирователь 11 не запускается и сигнал конца преобразования не формируется. Импульс паузы поступает на формирователь 13 где формируется импульс начальной . установки. Если количество синхроимпульсов кода больше номинального, то как только в дополнительном разряде (п+2) регистра 1 сдвига оказывается записанный код 1, которьй поступа ет на дешифратор 10 блока 3 управле ния и вызывает запуск формирователя 13 и запрет запуска формирователя 1 Таким образом, формирование импульса начальной установки осуществляется блоком 3 управления при наличии импульса и-паузы или при появ лении в (п+2) дополнительном разряде регистра 1 сдвига кода 1. Использование принятой информации осуществляется только по импудь су -конца преобразования, формируемо му на выходе 9, Формула изобретени 1. Преобразователь последователь ного кода в параллельный, содержащий регистр сдвига, отличающийся тем, что, с целью повышения достоверности и расширения области применения путем преобразования кода различной разрядности, в него введены буферный регистр, блок управления и блок вьщеления паузы, выход которого соединен с входами управления буферного регист ра и блока управления, п информацио ных выходов регистра сдвига соедине ны с соответствуюпрми информационными входами буферного регистра, выход которого является выходом устройства, (п+1) и (п+2) выходов регистра сдвига соединены с информационными входами блока управления, первый выход которого соединен с первым входом регистра сдвига, а второй выход является дополнительным выходом устройства, первый вход блока выделения паузы является входом синхронизации устройства, а второй вход объединен с вторым входом регистра сдвига и является входом синхроимпульсов кода устройства, третий вход регистра сдвига является информационным входом устройства. 2,Преобразователь по п, 1, отличающийся тем, ЧТО блок управления содержит дешифратор, первый формирователь импульса, элемент задержки и второй формирователь импульса, вход которого соединен с выходом элемента задержки, вход которого соединен с первым выходом дешифратора,, второй выход которого соединен с входом первого формирователя импульса, первый и второй входы дешифратора являются соответственно входом управления и информацонным входом блока управления, выходы первого и второго формирователей импульса являются соответственно первым и вторым выходами блока управления. 3.Преобразователь по п. 1, отличающийся тем, что блок вьщеления паузы содержит счетчик импульсов, первый элемент И, элемент НЕ и второй элемент И выход которого соединен со счетным входом счетчи-ка импульсов, выход старшего разряда которого через элемент НЕ соединен с первым входом второго элемента И, выходы младшего разряда счетчика импульсов соединены с соответствующими входами первого элемента И, выход которого является выходом блока ввделения паузы, второй вход второго элемент И и установочный вход счетчика импульсов являются соответственно первым и вторым входами блока выделения паузы.

фиг. г

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь последовательного кода в параллельный | 1986 |

|

SU1464292A2 |

| Преобразователь последовательного кода в параллельный | 1988 |

|

SU1656685A2 |

| Устройство для магнитной записи цифровой информации | 1982 |

|

SU1037337A1 |

| Преобразователь последовательного кода в параллельный | 1987 |

|

SU1418911A1 |

| Устройство магнитной записи сигналов цифровой информации | 1983 |

|

SU1157566A1 |

| Устройство для сбора,кодирования,передачи и приема информации с исправлением ошибок | 1980 |

|

SU960898A1 |

| Устройство для формирования тестовой последовательности | 1984 |

|

SU1218389A1 |

| Устройство для сопряжения электронной вычислительной машины с каналами связи | 1983 |

|

SU1113790A1 |

| Устройство для обмена данными между цифровой вычислительной машиной и устройством магнитной записи | 1981 |

|

SU1022139A1 |

| Устройство для преобразования телеграфного кода в видеокод | 1985 |

|

SU1314461A1 |

Изобретение относится к вычислительной технике, а именно к устройствам преобразования информации, и может быть использовано в системах передачи данных по цифровым каналам. Устройство позволяет не только определять сбои в приеме информации по каналу и вьшвлять слово, при. приеме которого произошел сбой, но и при переходе с канала на канал при асинхронной передаче информации выявлять недостоверные слова и исключать их из дальнейшего использования. Кроме того, устройство обеспечивает работу с различной разрядностью последовательного и параллельного кодов. Все перечисленное расширяет функциональные возможности устройства и повышает достоверность обрабатываемой информации. Преобразователь последовательного кода в параллельный содержит регистр сдвига, буферный регистр, блок управления и блок вьщеления паузы. Первый и второй входы блока вьщеления паузы являются соответственно входом синхронизации и входом синхроимпульсов кода устройства. Третий вход регистра сдвига является информациi онным входом устройства. Выход бу(Л ферного регистра и второй выход блока управления являются соответственно выходом устройства и допол.нительным выходом. Блок управления состоит из дешифратора, элемента задержки л двух формирователей импульса. Блок выделения паузы состоts5 ит из счетчика импульсов, двух элеО5 ментов И и элемента НЕ. 2 з.п. ф-лы, Ю 3 ил. СО ю

| Преобразователь последовательногоКОдА B пАРАллЕльНый | 1979 |

|

SU851396A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для преобразования последовательного кода в параллельный | 1982 |

|

SU1081639A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-07—Публикация

1985-04-09—Подача