Фиг.1

Изобретение относится к измерительной технике.

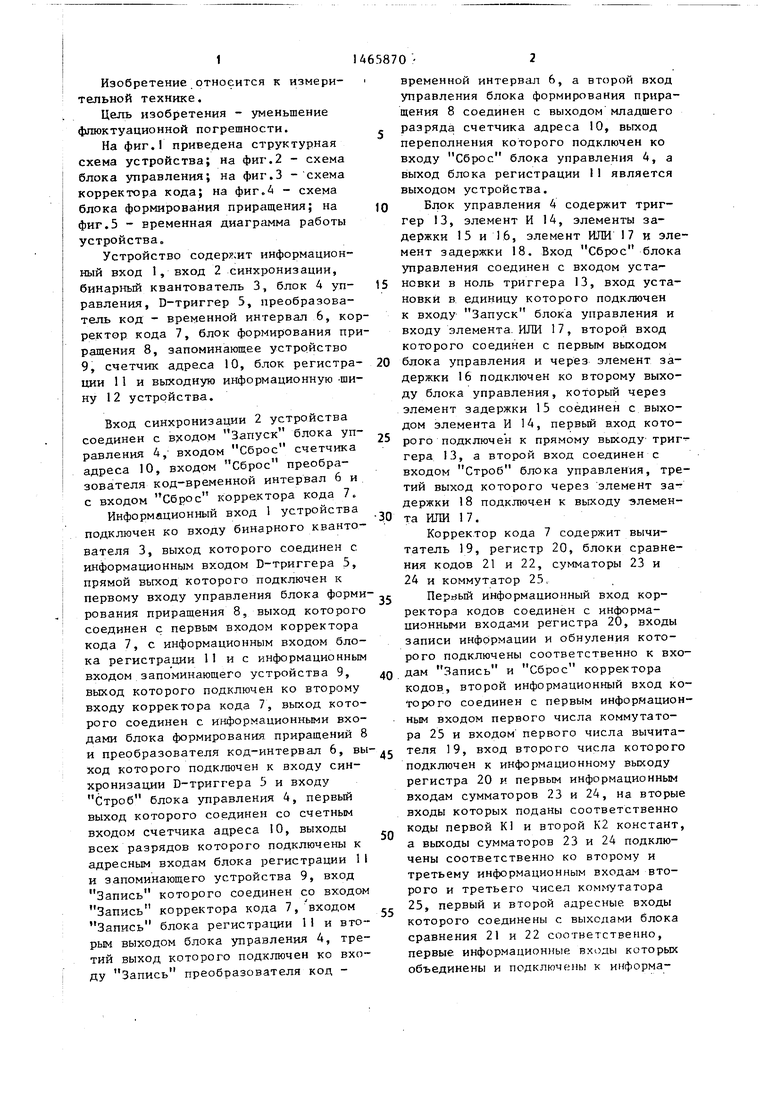

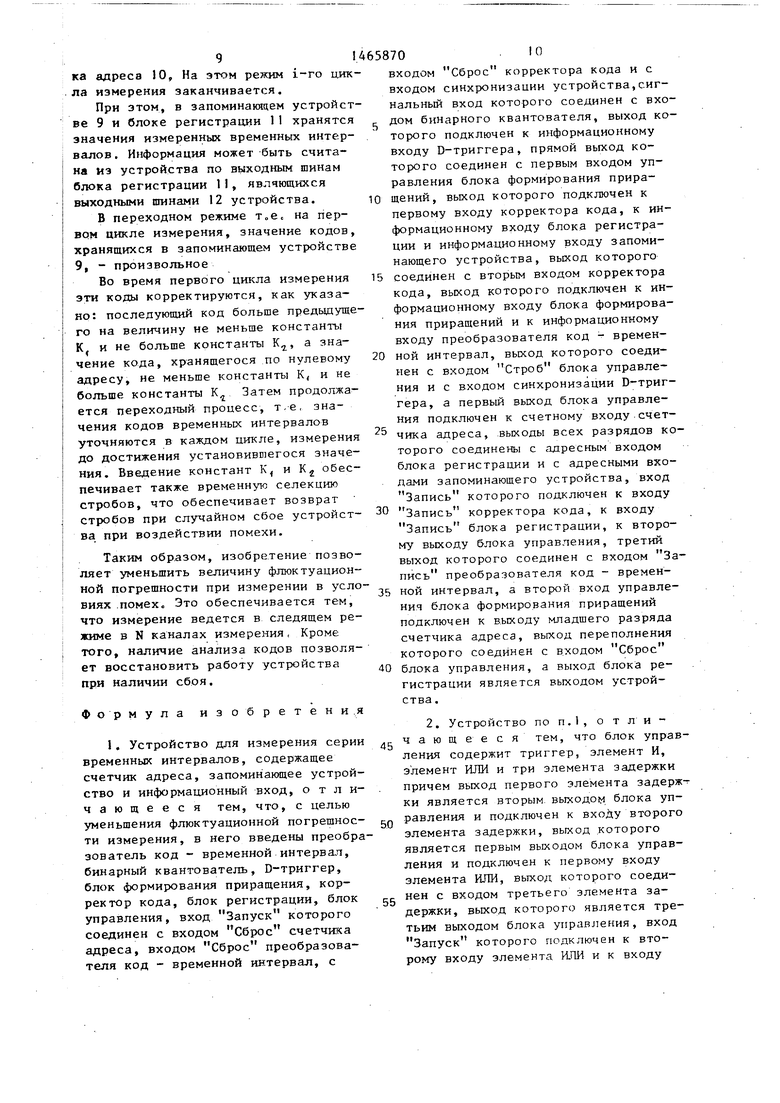

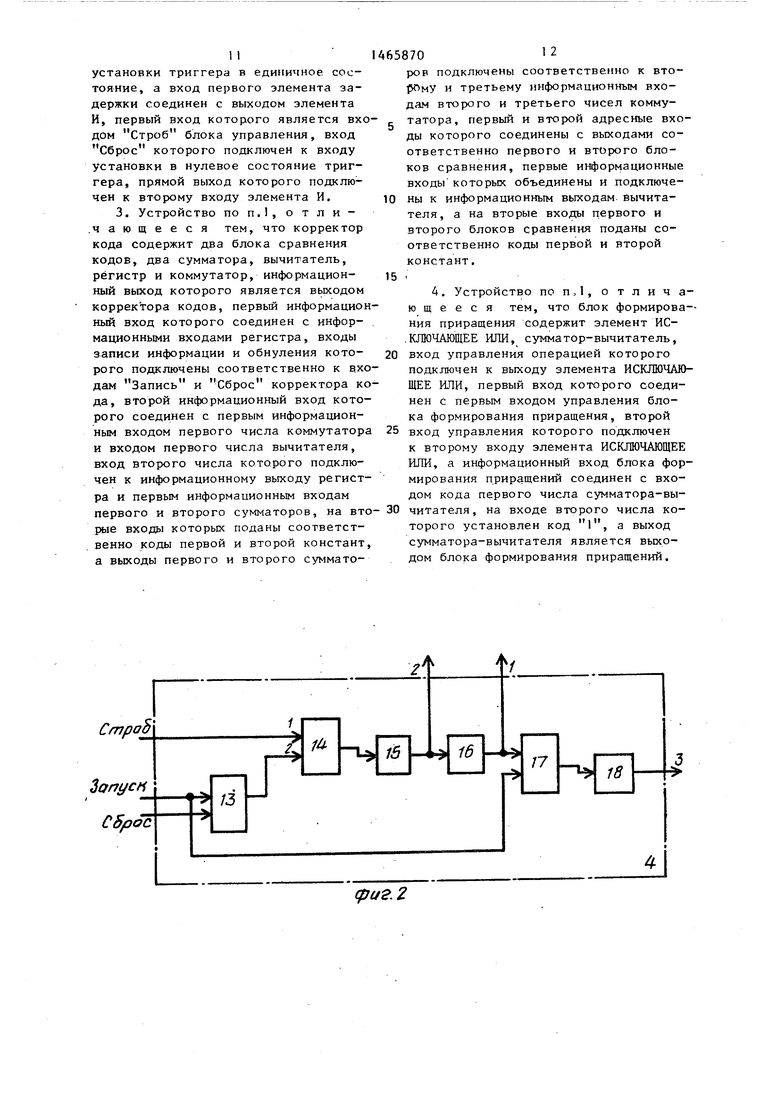

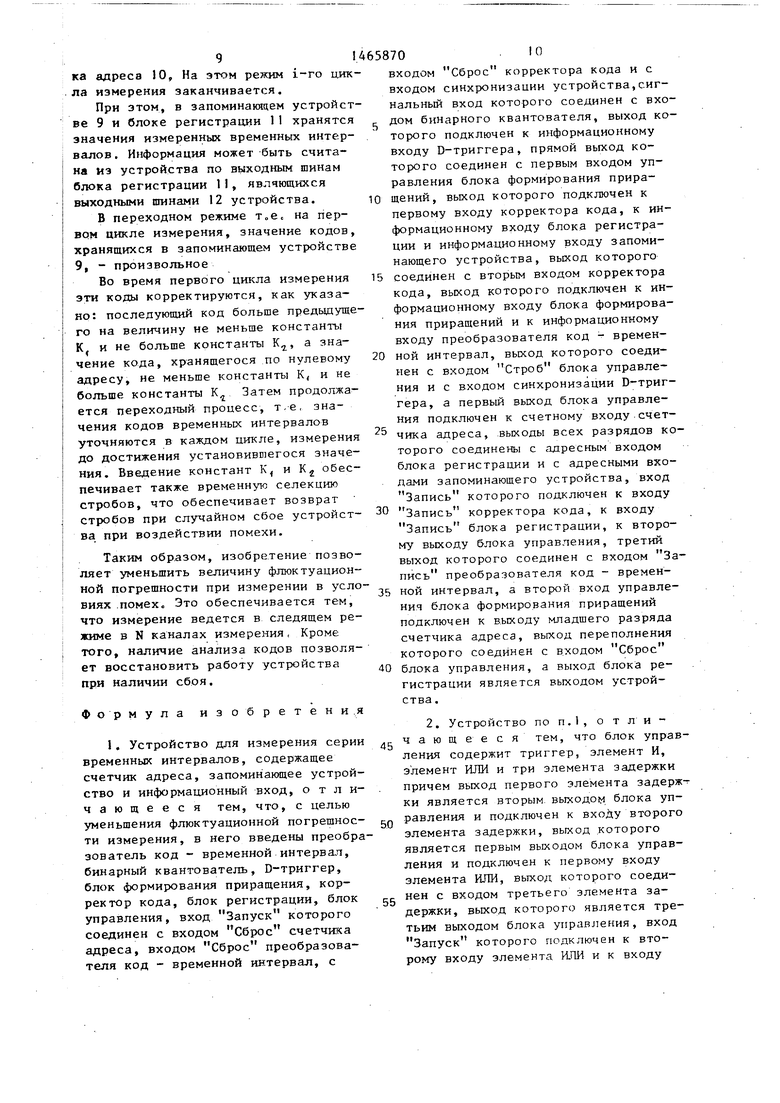

Цель изобретения - уменьшение флюктуационной погрешности.На фиг.Г приведена структурная схема устройства; на фиг.2 - схема блока управления; на фиг.З - схема корректора кода; на фиг.А - схема блока формирования приращения; на ю фиг.З - временная диагргшма работы устройства.

Устройство содер: ;ит информационный вход 1, вход 2 синхронизации, бинарньш квантователь 3, блок А уп- 15 равления, D-триггер 5, преобразователь код - временной интервал 6, корректор кода 7, блок формирования приращения 8, запоминающее устройство 9, счетчик адреса 10, блок регистра- 20 ции 11 и выходную информационную -шину 12 устройства.

Вход синхронизации 2 устройства соединен с входом Запуск блока уп- 35 равления А, входом Сброс счетчика адреса Ю, входом Сброс преобразователя код-временной интервал 6 и с входом Сброс корректора кода /.

Информационный вход 1 устройства д подключен ко входу бинарного кванто- вателя 3, выход которого соединен с информационным входом D-триггера 5, прямой выход которого подключен к первому входу управления блока формн- рования приращения 8, выход которого соединен с первым входом корректора кода 7, с информационным входом блока регистрации 11 и с информационным входом запоминающего устройства 9, 40 вькод которого подключен ко второму входу корректора кода 7, выход которого соединен с информационными входами блока формирования, приращений 8

временной интервал 6, а второй вход управления блока формирования приращения 8 соединен с выходом младщего разряда счетчика адреса 10, выход переполнения которого подключен ко входу Сброс блока управления 4, а выход блока регистрации 11 является выходом устройства.

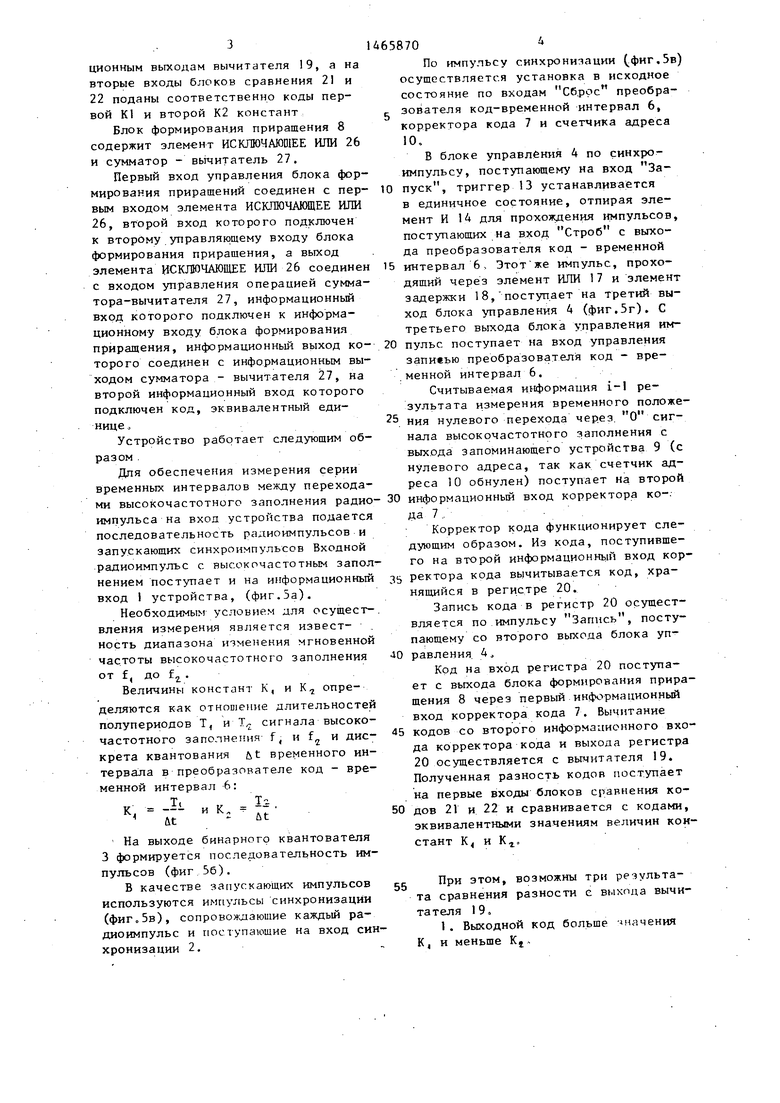

Блок управления 4 содержит триггер 13, элемент И IA, элементы задержки 15 и 16, элемент ИЛИ 17 и элемент задержки 18. Вход Сброс блока управления соединен с входом установки в ноль триггера 13, вход установки в единицу которого подключен к входу Запуск блока управления и входу элемента. ИЛИ 17, второй вход которого соединен с первым выходом блока управления и через элемент задержки 16 подключен ко второму выходу блока управления, который через элемент задержки 15 соединен с выходом элемента И 1А, первый вход которого подключен к прямому выходу триггера 13, а второй вход соединен с входом Строб блока управления, третий выход которого через злемент задержки 18 подключен к выходу элемента ИЛИ 17.

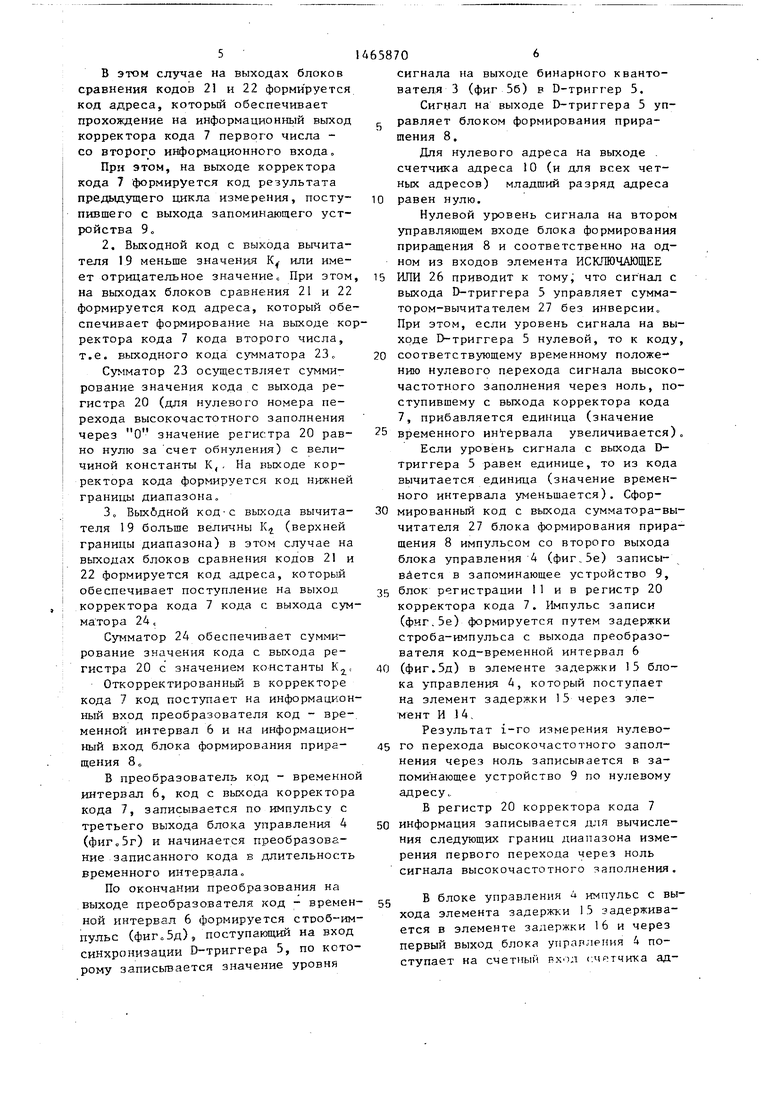

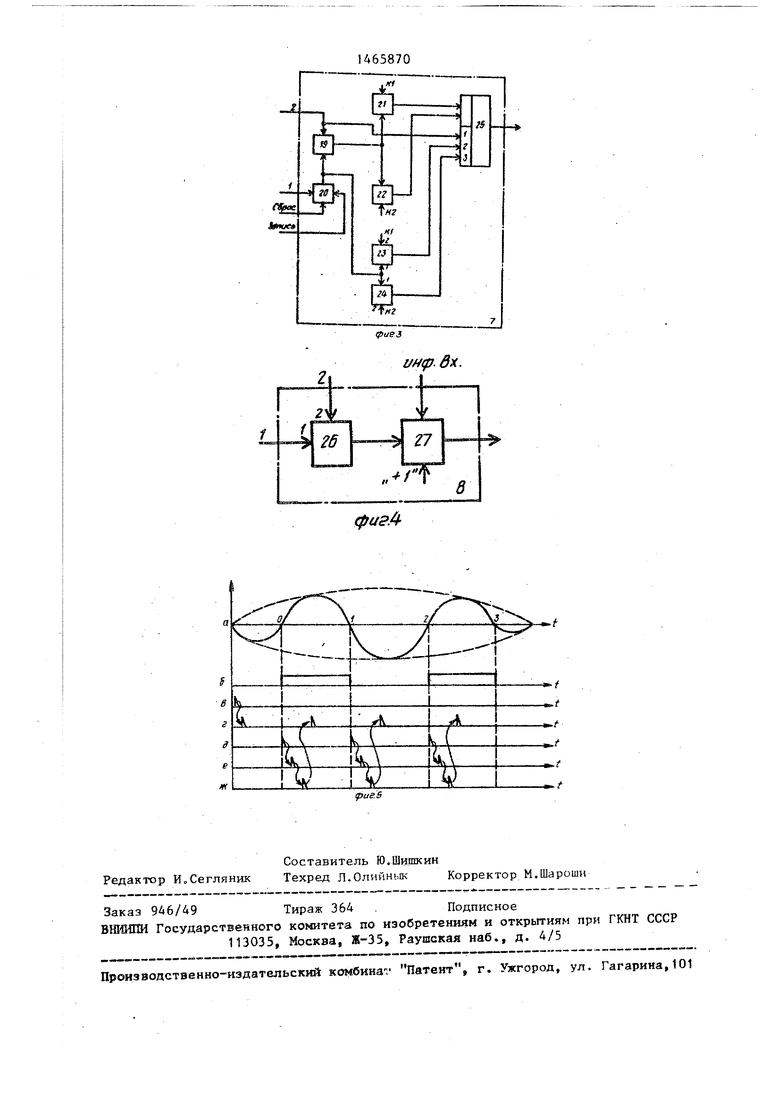

Корректор кода 7 содержит вычи- татель 19, регистр 20, блоки сравнения кодов 21 и 22, сумматоры 23 и 24 и коммутатор 25, .

Перйый информационный вход корректора кодов соединен с информационными входами регистра 20, входы записи информации и обнуления которого подключены соответственно к входам Запись и Сброс корректора кодов, второй информационный вход которого соединен с первым информацион ным входом первого числа коммутатора 25 и входом первого числа вычитаи преобразователя код-интервал 6, вы-д5 теля 19, вход второго числа которого

ход которого подключен к входу синхронизации D-триггера 5 и входу Строб блока управления 4, первый выход которого соединен со счетным входом счетчика адреса 10, выходы всех разрядов которого подключены к адресным входам блока регистрации 1I и запоминающего устройства 9, вход Запись которого соединен со входом Запись корректора кода 7, входом Запись блока регистрации 11 и вторым выходом блока управления 4, третий выход которого подключен ко входу Запись преобразователя код 50

55

подключен к информационному выходу регистра 20 и первым информационным входам сумматоров 23 и 24, на вторые входы которых поданы соответственно коды первой К и второй К2 констант, а выходы сумматоров 23 и 24 подключены соответственно ко второму и третьему информационным входам второго и третьего чисел ком г/татора 25, первый и второй адресные входы которого соединены с выходами блока сравнения 21 и 22 соответственно, первые информационные входы которых обьединены и подключены к информавременной интервал 6, а второй вход управления блока формирования приращения 8 соединен с выходом младщего разряда счетчика адреса 10, выход переполнения которого подключен ко входу Сброс блока управления 4, а выход блока регистрации 11 является выходом устройства.

Блок управления 4 содержит триггер 13, элемент И IA, элементы задержки 15 и 16, элемент ИЛИ 17 и элемент задержки 18. Вход Сброс блока управления соединен с входом установки в ноль триггера 13, вход установки в единицу которого подключен к входу Запуск блока управления и входу элемента. ИЛИ 17, второй вход которого соединен с первым выходом блока управления и через элемент задержки 16 подключен ко второму выходу блока управления, который через элемент задержки 15 соединен с выходом элемента И 1А, первый вход которого подключен к прямому выходу триггера 13, а второй вход соединен с входом Строб блока управления, третий выход которого через злемент задержки 18 подключен к выходу элемента ИЛИ 17.

Корректор кода 7 содержит вычи- татель 19, регистр 20, блоки сравнения кодов 21 и 22, сумматоры 23 и 24 и коммутатор 25, .

Перйый информационный вход корректора кодов соединен с информационными входами регистра 20, входы записи информации и обнуления которого подключены соответственно к входам Запись и Сброс корректора кодов, второй информационный вход которого соединен с первым информационным входом первого числа коммутатора 25 и входом первого числа вычитателя 19, вход второго числа которого

подключен к информационному выходу регистра 20 и первым информационным входам сумматоров 23 и 24, на вторые входы которых поданы соответственно коды первой К и второй К2 констант, а выходы сумматоров 23 и 24 подключены соответственно ко второму и третьему информационным входам второго и третьего чисел ком г/татора 25, первый и второй адресные входы которого соединены с выходами блока сравнения 21 и 22 соответственно, первые информационные входы которых обьединены и подключены к информа3I

ционным выходам вычитателя 19, а на вторые входы блоков сравнения 21 и 22 поданы соответственно коды первой К1 и второй К2 констант

Блок формирования приращения 8 содержит элемент ИСКЛЮЧАЮОШЕ ИЛИ 26 и сумматор - вычитатель 27.

Первый вход управления блока формирования приращений соединен с первым входом элемента ИСКЛОЧАЩЕЕ ИЛИ 26, второй вход которого подключен к второму управляющему входу блока формирования приращения, а выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 26 соединен с входом управления операцией сумма- тора-вычитателя 27, информационный вход которого подключен к информационному входу блока формирования приращения, информационньш выход которого соединен с информационным выходом сумматора - вычитателя 27, на второй информационный вход которого подключен код, эквивалентный единице.

Устройство работает следующим образом ,

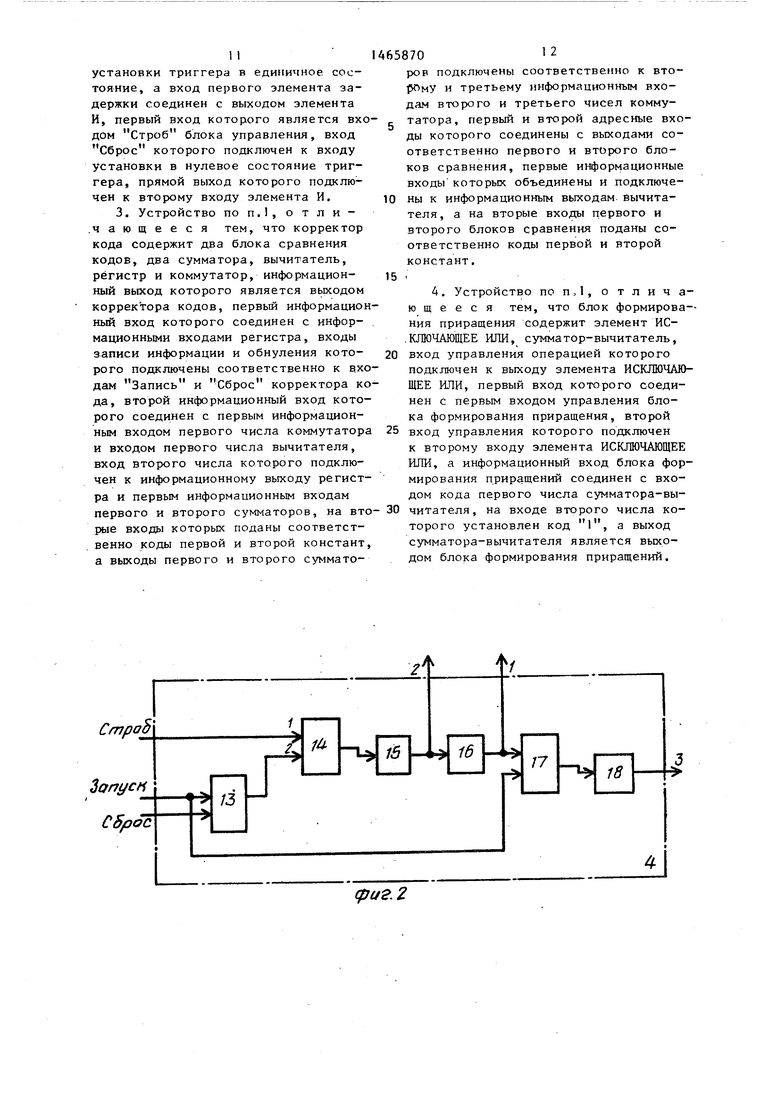

Для обеспечения измерения серии временных интервалов между переходами высокочастотного заполнения радиоимпульса на вход устройства подается последовательность радиоимпульсов и запускающих синхроимпульсов Входной радиоимпульс с высокочастотным заполнением поступает и на информационньш вход 1 устройства, (фиг.За),

Необходимым условием для осуществления измерения является известность диапазона изменения мгновенной частоты высокочастотного заполнения от f, до fj.

Величины констант К, и К, определяются как отношение длительностей полупериодов Т, и Т сигнала высокочастотного заполнения f, и f и дискрета квантования &t временного ин- тервала в преобразователе код - временной интервал 6:

к,--

На выходе бинарного квантователя 3 формируется последовательность импульсов (фиг 5б).

В качестве запускающих импульсов используются импульсы синхронизации (фиг„5в), сопровождаюшие каждый радиоимпульс и поступающие на вход синхронизации 2.

65870

По импульсу синхронизации (фиг.Зв) осуществляется установка в исходное состояние по входам Сброс преобразователя код-временной интервал 6, корректора кода 7 и счетчика адреса

10.

В блоке управления 4 по синхроимпульсу, поступающему на вход За- 10 пуск, триггер 13 устанавливается в единичное состояние, отпирая элемент И 14 для прохождения импульсов, поступающих на вход Строб с выхода преобразователя код - временной 15 интервал 6, Этот же импульс, проходящий через элемент ИЛИ 17 и элемент задержки 18,поступает на третий выход блока управления 4 (фиг.Зг). С третьего выхода блока управления им- 20 пульс поступает на вход управления запиеью преобразователя код - вре- менной интервал 6.

Считываемая информация i-l результата измерения временного положе- 25 ния нулевого перехода через. О сигнала высокочастотного заполнения с выхода запоминающего устройства 9 (с нулевого адреса, так как счетчик адреса 10 обнулен) поступает на второй 30 информационный вход корректора ко-.

да 7 .

Корректор кода функционирует следующим образом. Из кода, поступившего на второй информационный вход кор- 35 ректора кода вычитывается код, хранящийся в регистре 20.

Запись кода в регистр 20 осуществляется по импульсу Запись, поступающему со второго выхода блока упйО равления. 4

Код на вход регистра 20 поступает с выхода блока формирования приращения 8 через первый информационный вход корректора кода 7. Вычитание

45 кодов со второго информационного входа корректора кода и выхода регистра 20 осуществляется с вычитателя 19. Полученная разность кодов поступает на первые входы блоков сравнения ко50 дов 21 и 22 и сравнивается с кодами, эквивалентными значениям величин констант К4 н K

При этом, возможны три результа- та сравнения разности с выхода вычитателя 19,

1 . Выходной код больше -дначення

К, и меньше К(В этом случае на выходах блоков сравнения кодов 21 н 22 формируется код адреса, который обеспечивает прохождение на информационный выход корректора кода 7 первого числа - со второго информационного входа„

При этом, на выходе корректора кода 7 формируется код результата предыдущего цикла измерения, поступившего с выхода запоминающего устройства 9о

2. Выходной код с выхода вычита- теля 19 меньше значения или имеет отрицательное значение с При этом на выходах блоков сравнения 21 и 22 формируется код адреса, который обеспечивает формирование на выходе корректора кода 7 кода второго числа, т.е. выходного кода сумматора 23,.

Сумматор 23 осуществляет суммирование значения кода с выхода регистра 20 (для нулевого номера перехода высокочастотного заполнения через О значение регистра 20 равно нулю за счет обнуления) с величиной константы К,, На выходе корректора кода формируется код нижней границы диалазонао

3„ Вькйдной код С выхода вычита- теля 19 больше величны К (верхней границы диапазона) в этом случае на выходах блоков сравнения кодов 21 и 22 формируется код адреса, который обеспечивает поступление на выход корректора кода 7 кода с выхода сумматора 24 е

Сумматор 24 обеспечивает суммирование значения кода с выхода регистра 20 с значением константы К,

Откорректированный в корректоре кода 7 код поступает на информационный вход преобразователя код - временной интервал 6 и на информационный вход блока формирования приращения 8 „

В преобразователь код - временно интер}зал 6, код с выхода корректора кода 7, залисы.вается по импульсу с третьего выхода блок.а управления 4 (фиг,5г) и начинается преобразование записанного кода в длительность временного интервала

По окончании преобразования на выходе преобразователя код - временной интервал 6 формируется строб-импульс (фиг.5д), поступающий на вход синхронизации D-триггера 5, по которому записывается значение уровня

сигнала на выходе бинарного квантователя 3 (фиг 5б) в D-триггер 5.

Сигнал на выходе D-триггера 5 управляет блоком формирования прира- шения 8.

Для нулевого адреса на выходе . счетчика адреса 10 (и для всех четных адресов) младший разряд адреса равен нулю.

Нулевой уровень сигнала на втором управляющем входе блока формирования приращения В и соответственно на одном из входов элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ 26 приводит к тому, что сигнал с выхода D-триггера 5 управляет сумма- тором-вычитателем 27 без инверсии При этом, если уровень сигнала на выходе D-триггера 5 нулевой, то к коду,

соответствующему временному положению нулевого перехода сигнала высокочастотного заполнения через ноль, поступившему с выхода корректора кода 7, прибавляется единица (значение

временного интервала увеличивается)

Если уровень сигнала с выхода D- триггера 5 равен единице, то из кода вычитается единица (значение временного интервала уменьшается). Сформированный код с выхода сумматора-вы- читателя 27 блока формирования приращения 8 импульсом со второго выхода блока управления 4 (фиг,5е) записы- вйется в запоминающее устройство 9,

блок регистрации 11 и в регистр 20 корректора кода 7. Импульс записи (фиг.5е) формируется путем задержки строба-импульса с выхода преобразователя код-временной интервал 6

(фиг.Зд) в элементе задержки 15 блока управления 4, который поступает на элемент задержки 15 через элемент И 1 4.

Результат i-ro измерения нулевого перехода высокочастотного заполнения через ноль записывается в запоминающее устройство 9 по нулевому адресу.

В регистр 20 корректора кода 7

информация записывается для вычисления следующих границ диапазона измерения первого перехода через ноль сигнала высокочастотного заполнения.

В блоке управления 4 импульс с выхода элемента задержки 15 задерживается в элементе задержки 16 и через первый выход блока управления 4 поступает на счетный вхол счртчиха ад

p eca 10, устанавливая на его выходе код первого адреса.

Емкость счетчика адреса 10 определяется числом измеряемых времен- ных интервалов,. Это же число определяет и количество адресов запоминающего устройства 9 и блока регистрации 1 1 о

Далее устройство осуществляет i-oe измерение первого перехода сигнала высокочастотного заполнения через ноль.

Измерение i-ro интервала отличается тем, что в регистре 20 коррек- тора кода 7 записан код временного интервала нулевого перехода сигнала высокочастотного заполнения через ноль.

Результат (i-1 ) измерения пер- вого перехода сигнала высокочастотного заполнения нерез ноль с выхода запоминающего устройства 9 поступает на второй информационный вход корректора кода 7.,

В корректоре кода 7 этот код сравнивается с границами диапазона временного положения нулевого перехода через ноль сигнала высокочастотного заполнения плюс величина константы К ( временного положения нулевого перехода через ноль сигнала высокочастотного заполнения плюс константа K2.(tc,+K2).

I

На вычитателе 19, на входе кода

второго числа, устанавливается код, записанный в регистр 20 в результате i-ro измерения нулевого перехода через ноль сигнала высокочастотного заполнения, Это обеспечивает проверку новых границ диапазона измерения.

Скорректированный код с выхода корректора кода 7 поступает на вход преобразователя код - временной ин- тервал 6 и записывается сигналом с выхода блока управления 4 (фиг.Зг),

На третьем выходе блока управления 4 формируется импульс, задер- жанный в элементе задержки 18 и поступивший через элемент ИЛИ 17 с выхода элемента задержки 16.

Временной интервал, формируемый для измерения первого перехода отсчи тывается от импульса Сброс преобразователя код - временной интервал 6 до момента появления первого строба (фиг.5д), так как после формировани

5

0

5

О

5

0

5

нулевого временного интервала преобразователь код - временной интервал 6 не обнуляется.

После окончания первого вре.меино- го интервала повторяется формирование импульсов записи корректора кода 7, запоминающего устройства 9 и блока регистрации М,

Формирование приращения в блоке

формирования приращения 8 в первой точке измерения (как и во всех нечетных) отличается от формирювания приращения в нулевой точке измерения (как и во всех четных).

Поступающий младший разряд счетчика адреса 10 в нечетных интервалах измерения имеет единичное состояние. Это единичное состояние на входе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 26 обеспечивает инвертирование выходного сигнала D-триггера 5, т.е. сигнал управления на входе сумматора - вычитателя 27 инвертируется

Таким образом, если сигнал на выходе D-триггера 5 имеет единичное состояние - значение записываемого в запоминающее устройство 9 и корректор код 7 временного интервала увеличивается Если Же уровень сигнала на выходе D-триггера 5 имеет нулевое значение, то величина кода временного интервала уменьщается,

Использование элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 26 в блоке формирования приращения 8 позволяет организовать слежение как за положительными, так и за отрицательными переходами через ноль сигнала высокочастотного заполнения радиоимпульса.

По окончании измерения всех N переходов сигнала высокочастотного заполнения через ноль на выходе счетчика адреса 10 формируется сигнал переполнения, который поступает на вход Сброс блока управления 4 и устанавливает триггер 11 в нулевое сос- тояние

При этом, запрещается поступление строб-импульса (фиг.Зд) с выхода преобразователя код - временной интервал в блок управления 4, т.е„ прекращается формирование импульсов, управляющих записью запоминающего устройства 9, блока регистрации 1I, корректора кода 7, преобразоиателя код - временной интервал 6 и счетчи9I

ка адреса 10, На этом режим i-ro цикла измерения заканчивается.

При этом, в запоминающем устройстве 9 и блоке регистрации 11 хранятся значения измеренных временных интервалов . Информация может быть считана из устройства по выходным шинам блока регистрации 11, являющихся выходными шинами 12 устройства.

В переходном режиме т„е. на первом цикле измерения, значение кодов, хранящихся в запоминающем устройстве 9, - произвольное

Во время первого цикла измерения эти коды корректируются, как указано: последующий код больше предыдущего на величину не меньше константы К и не больше константы К, а значение кода, хранящегося по нулевому адресу, не меньше константы К и не больше константы К Затем продолжается переходный процесс, т.е. значения кодов временных интервалов уточняются в каждом цикле, измерения до достижения установившегося значения. Введение констант К, и К обеспечивает также временную селекцию стробов, что обеспечивает возврат стробов при случайном сбое устройства при воздействии помехи.

Таким образом, изобретение позволяет уменьшить величину флюктуацион- ной погрешности при измерении в уело ВИЯХ .помех. Это обеспечивается тем, что измерение ведется в следящем режиме в N каналах измерения, Кроме того, наличие анализа кодов позволяет восстановить работу устройства при наличии сбоя.

Формула изобретени ,я

. Устройство для измерения серии временных интервалов, содержащее счетчик адреса, запоминающее устройство и информационный вход, отличающееся тем, что, с целью уменьшения флюктуационной погрешности измерения, в него введены преобразователь код - временной интервал, бинарный квантователь, D-триггер, блок формирования приращения, корректор кода, блок регистрации, блок управления, вход Запуск которого соединен с входом Сброс счетчигка адреса, входом Сброс преобразователя код - временной интервал, с

65870.10

входом Сброс корректора кода и с входом синхронизации устройства,сигнальный вход которого соединен с входом бинарного квантователя, выход ко- торого подключен к информационному входу D-триггера, прямой выход которого соединен с первым входом управления блока формирования прира- 10 щений, выход которого подключен к первому входу корректора кода, к информационному входу блока регистрации и информационному входу запоминающего устройства, выход которого 15 соединен с вторьм входом корректора кода, выход которого подключен к информационному входу блока формирова- ния приращений и к информационному

входу преобразователя код - времен- 20 ной интервал, выход которого соединен с входом Строб блока управления и с входом синхронизации В-триг- гера, а первый выход блока управления подключен к счетному входу счетчика адреса, выходы всех разрядов которого соединены с адресным входом блока регистрации и с адресными входами запоминающего устройства, вход Запись которого подключен к входу 30 Запись корректора кода, к входу Запись блока регистрации, к второму выходу блока управления, третий выход которого соединен с входом Запись преобразователя код - времен- 35 ной интервал, а второй вход управления блока формирования приращений подключен к в.ыходу младшего разряда счетчика адреса, выход переполнения которого соединен с входом Сброс 40 блока управления, а выход блока регистрации является выходом устройства .

25

5

2. Устройство по П.1, о т л и - чающееся тем, что блок управления содержит триггер, элемент И, элемент ИЛИ и три элемента задержки причем выход первого элемента задерж- ки является вторым выходом, блока управления и подключен к вхоДу второго элемента задержки, выход которого является первым выходом блока управления и подключен к первому входу элемента ИЛИ, выход которого соединен с входом третьего элемента задержки, вькод которого является третьим выходом блока управления, вход Запуск которого подключен к второму входу элемента ИЛИ и к входу

11I

установки триггера в единичное состояние, а вход первого элемента задержки соединен с выходом элемента И, первый вход которого является входом Строб блока управления, вход Сброс которого подключен к входу установки в нулевое состояние триггера, прямой выход которого подключен к второму входу элемента И.

3. Устройство по п.1, о т л и - .чающееся тем, что корректор кода содержит два блока сравнения кодов, два сумматора, вычитатель, регистр и коммутатор, информационный выход которого является вькодом корректора кодов, первый информационный вход которого соединен с инфор- . мационными входами регистра, входы записи информации и обнуления которого подключены соответственно к входам Запись и Сброс корректора кода, второй информационный вход которого соединен с первым информационным входом первого числа коммутатора и входом первого числа вычитателя, вход второго числа которого подключен к информационному выходу регистра и первым информационным входам первого и второго сумматоров, на вто рые входы которых поданы соответственно коды первой и второй констант, а выходы первого и второго суммато658701 2

ров подключены соответственно к вто- рОмУ и третьему информационным входам второго и третьего чисел коммутатора, первый и второй адресные входы которого соединены с выходами соответственно первого и второго блоков сравнения, первые информационные входы которых объединены и подключе0 ны к информационным выходам вычитателя, а на вторые входы цервого и второго блоков сравнения поданы соответственно коды первой и второй констант.

15 .

4, Устройство поп,1,отлича- ю щ е е с я тем, что блок формирования приращения содержит элемент ИС- .КЛЮЧАЮЩЕЕ ИЛИ, сумматор-вычитатель,

20 вход управления операцией которого подключен к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с первым входом управления блока формирования приращения, второй

25 вход управления которого подключен к второму входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а информационный вход блока формирования приращений соединен с входом кода первого числа сумматора-вы30 читателя, на входе второго числа которого установлен код I, а выход сумматора-вычитателя является выходом блока формирования приращений.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выделения изображений подвижных объектов | 1987 |

|

SU1462373A1 |

| Устройство для поиска координат точки экстремума функции двух переменных | 1981 |

|

SU966703A1 |

| Функциональный преобразователь | 1985 |

|

SU1251103A1 |

| Программируемый генератор циклов | 1988 |

|

SU1644119A1 |

| Цифровой генератор | 1986 |

|

SU1347164A1 |

| Спектроанализатор кардиосигналов | 1984 |

|

SU1170371A1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2459241C1 |

| Устройство коррекции | 1987 |

|

SU1499507A1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2455682C1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2477887C1 |

Изобретение относится к измери тельной технике и позволяет уменьИНф. Синхро шить фпюктуационную погрешность.Устройство содержит запоминающее устройство 9 и счетчик 10 адреса. Введение бинарного квантователя 3, блока 4 управления, D-триггера 5, преобразователя 6 код-временной интервал, корректора 7 кода, блока 8 формирования приращения и блока 11 регистрации позволяет измерение проводить в следящем режиме в N каналах измерения. Кроме того, наличие анализа кодов позволяет восстановить работу устройства при наличии сбоя/В описании приведены примеры реализации блока 4 управления, корректора 7 кода и блока 8 формирования приращения. 3 з.п. ф-лы, 5 ил. с б (Л 4 О5 СП 00

(ри2.2

--

«М--Г

.

26

.ifi

индз. вх.

Z7

,.

8

фиг4

| Измеритель временных интервалов | 1974 |

|

SU546845A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для измерения серии временных интервалов | 1977 |

|

SU699485A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-03-15—Публикация

1986-11-26—Подача