о.

4ъ

4ъ

| название | год | авторы | номер документа |

|---|---|---|---|

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Генератор циклов | 1981 |

|

SU964616A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ | 1997 |

|

RU2119717C1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2459241C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2004 |

|

RU2260195C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| АДАПТИВНОЕ ЦИФРОВОЕ ДИФФЕРЕНЦИРУЮЩЕЕ И ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2535467C1 |

Изобретение относится к автоматике, вычислительной технике, предназначено для генерирования импульсных сигналов с заданными периодами следования и может быть использовано в контрольно-измерительном оборудовании параметрического контроля БИС и СБИС. Цель изобретения - расширение класса-решаемых задач за счет расширения области рабочих частот и дискрета задания их точности. Устройство содержит регистр 2, блок 4 синхронизации, блок 3 перестройки, счетчик 5, вычитатель 6, адресные регистры 7,8, триггеры 9,10, генератор 1 эталонной частоты, шинные мультиплексные распределители 11,12, линию 13 задержки, элемент 14 задержки, формирователь 15 выходного сигнала. Поставленная цель достигается за счет введения регистра 2, счетчика 5, адресных регистров 7,8, шинных мультиплексных распределителей 11,12, формирователя 15 выходных сигналов. 1 з.п. ф-лы, 8 ил., 1 табл. о 8 (Л

СО

Изобретение относится к автоматике и вычислительной технике и предназначено для генерирования импульсных сигналов с заданными периодами следования и, кроме того, может быть использовано в контрольно-измерительном оборудовании параметрического контроля БИС и СБИС в качестве перестраиваемого генератора, тайме- ра, формирователей синхронизирующих, стробирующих и управляющих сигналов объекта контроля, где точное высокочастотное генерирование импульсных сигналов с заданными параметрами рас- ширяет саму методику параметрического контроля и способствует классу создания более прогрессивной цифровой вычислительной техники.

Цель изобретения - расширение

класса решаемых задач за счет расширения области рабочих частот и дискрета задания их точности.

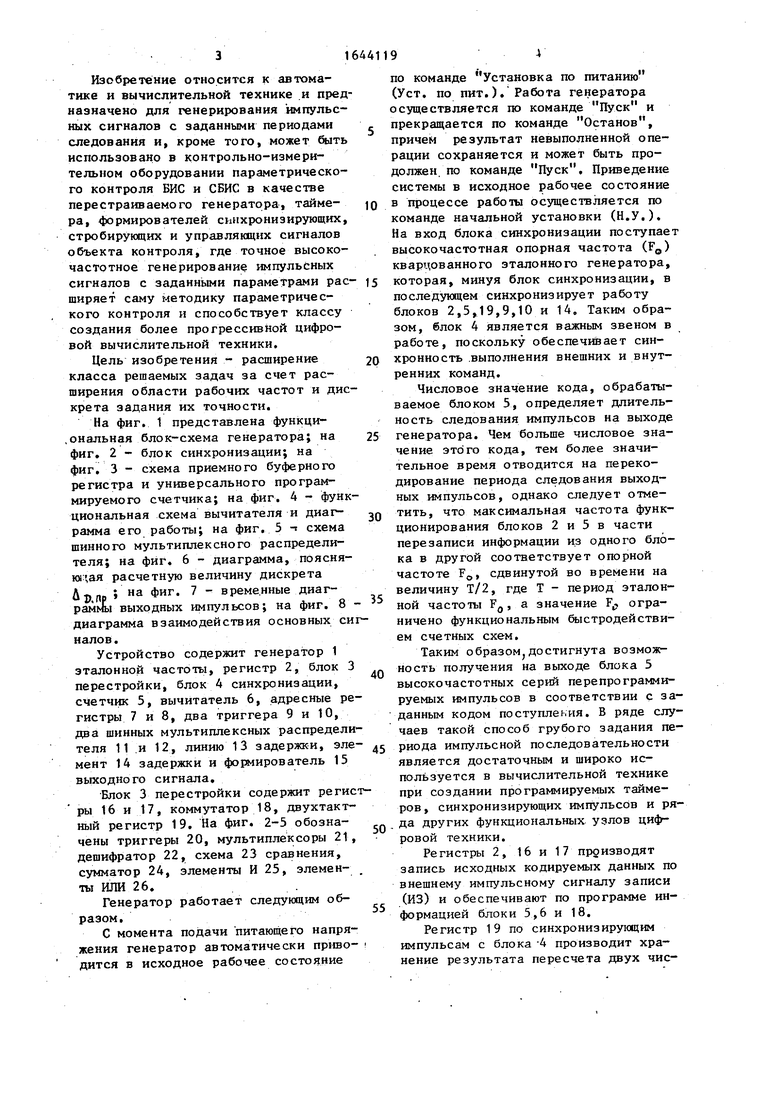

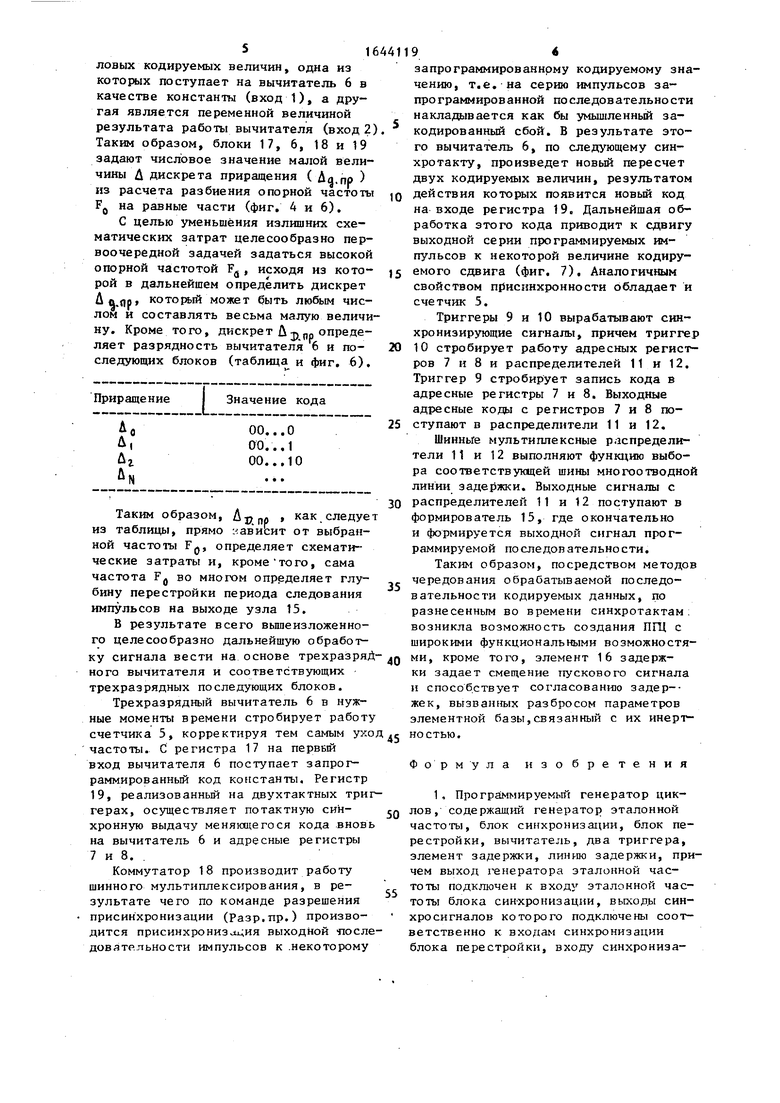

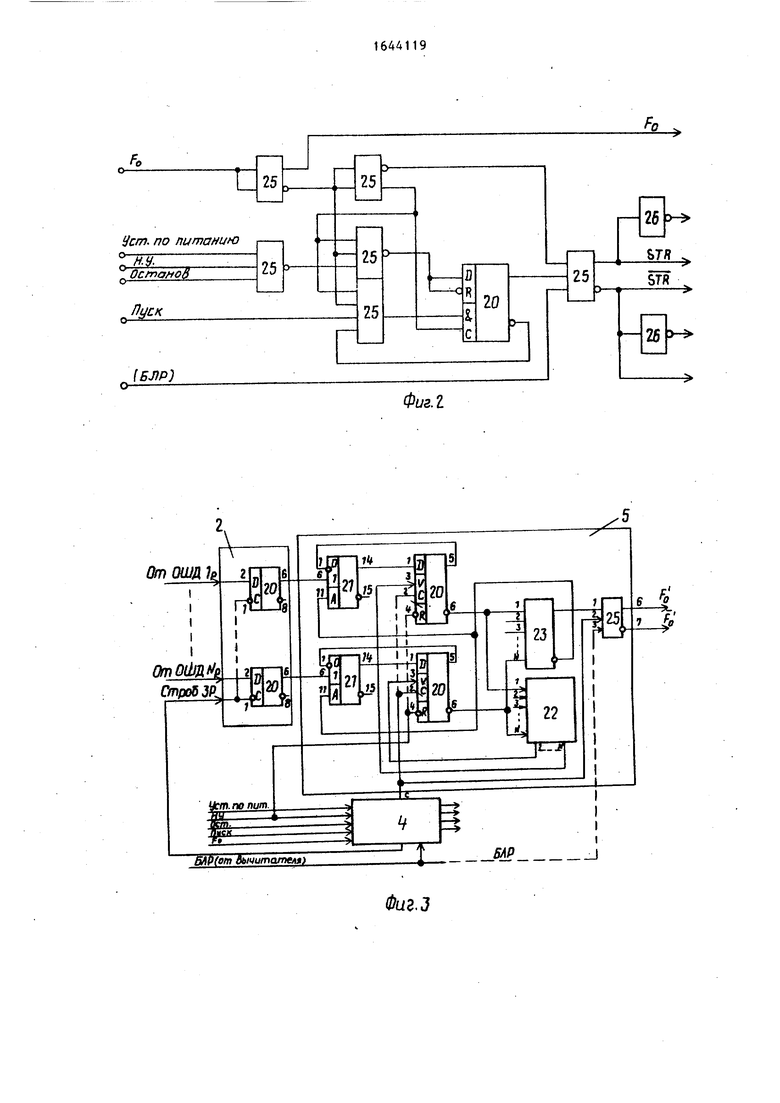

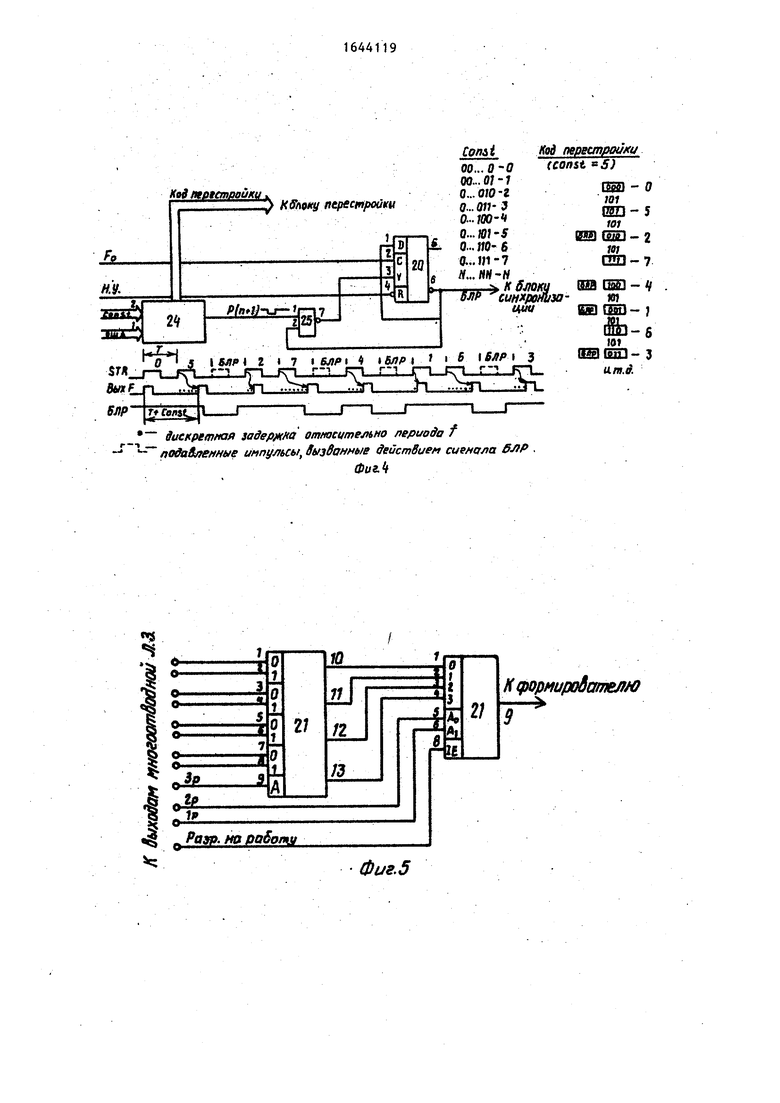

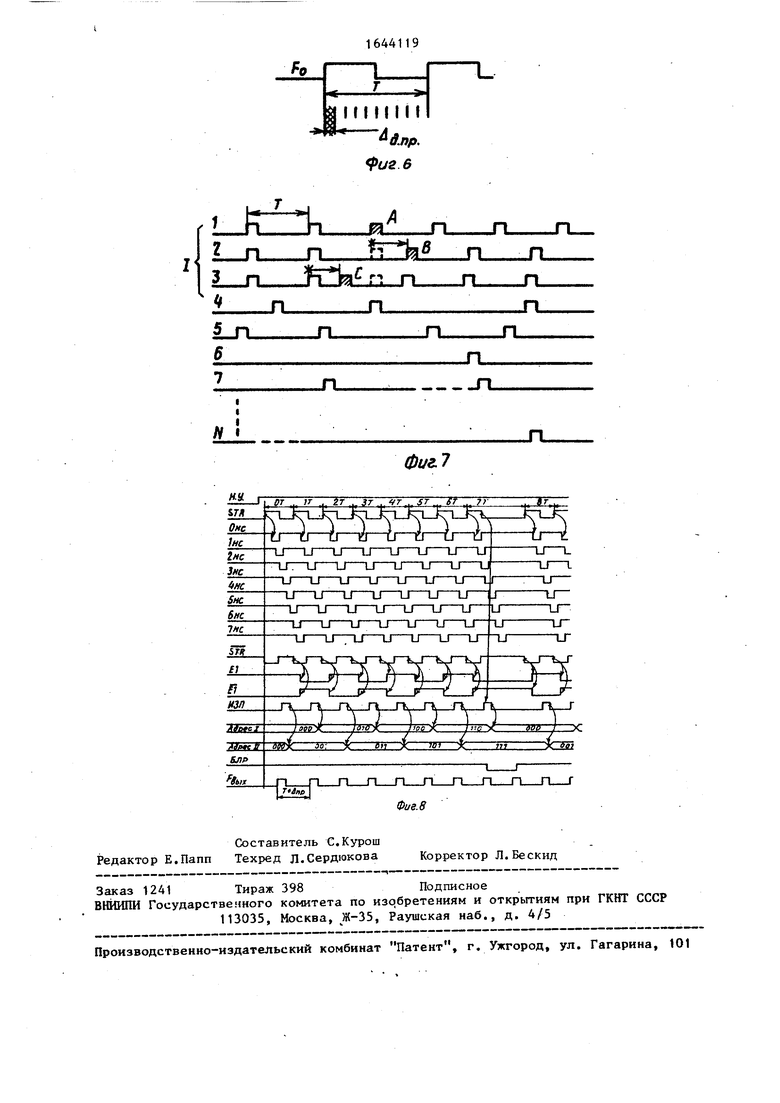

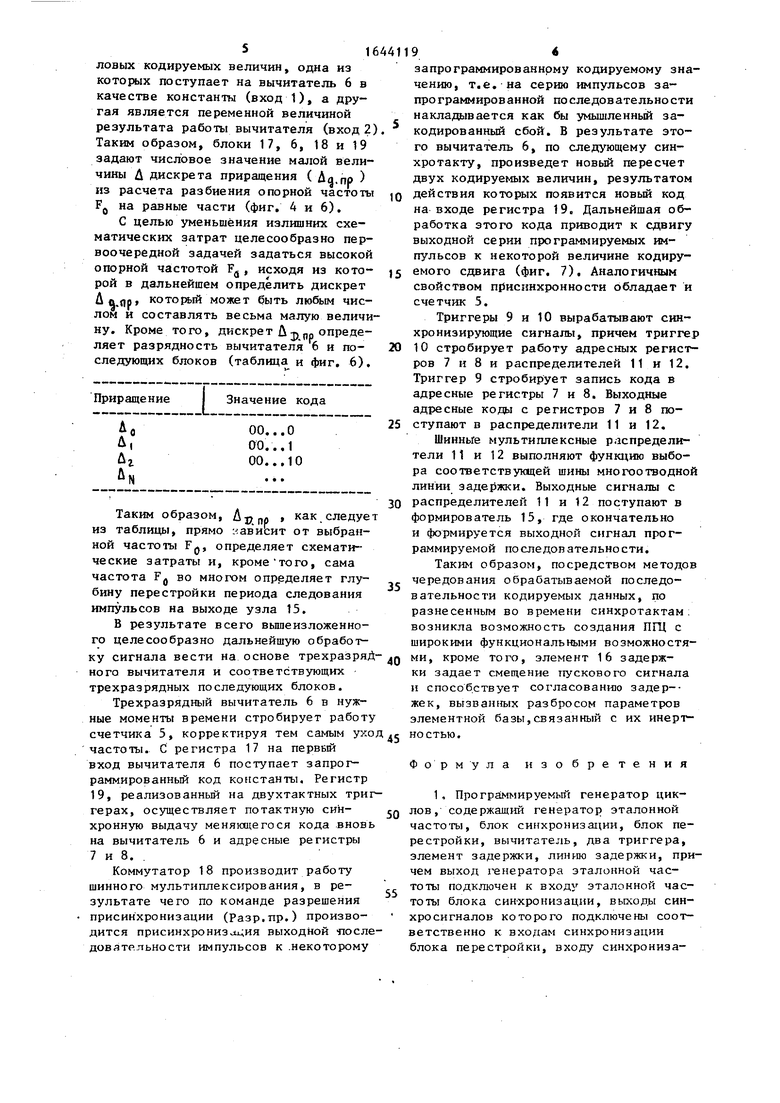

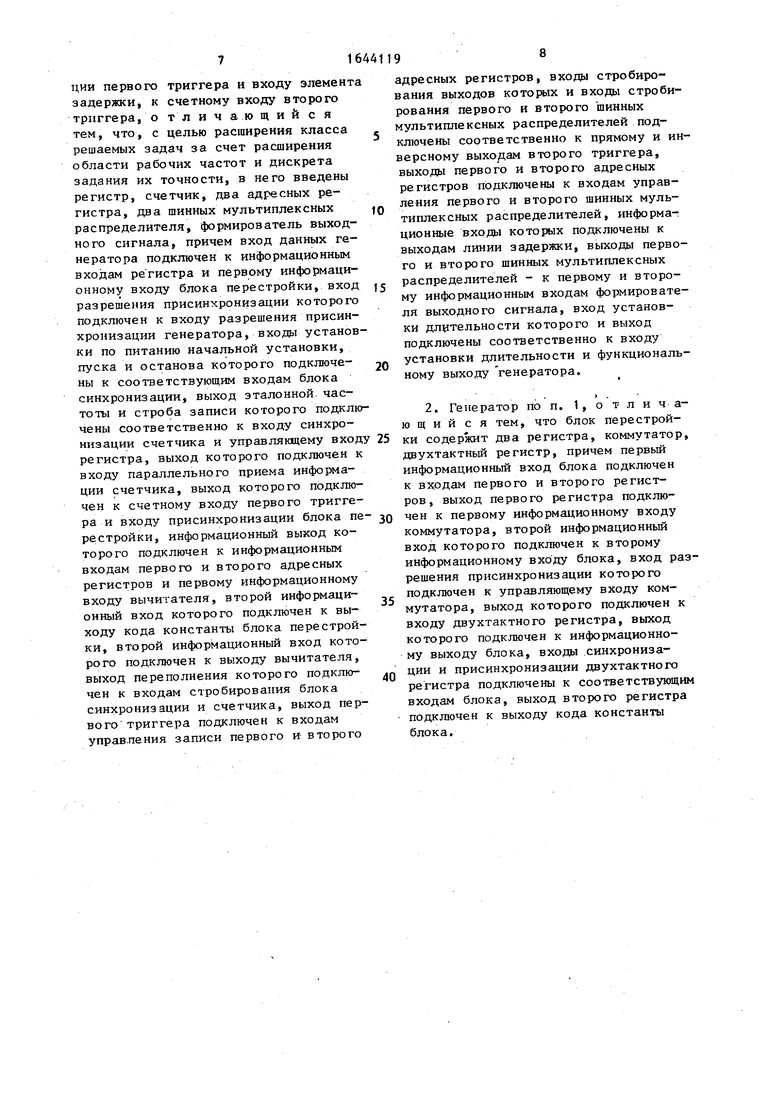

На фиг. 1 представлена функциональная блок-схема генератора; на фиг. 2 - блок синхронизации; на фиг. 3 - схема приемного буферного регистра и универсального программируемого счетчика; на фиг. 4 - функциональная схема вычитателя и диаг- рамма его работы; на фиг. 5 - схема шинного мультиплексного распределителя; на фиг. 6 - диаграмма, поясняющая расчетную величину дискрета Д j. ; на фиг. 7 - временные диаграммы выходных импульсов; на фиг. 8 - диаграмма взаимодействия основных сигналов .

Устройство содержит генератор 1 эталонной частоты, регистр 2, блок 3 перестройки, блок 4 синхронизации, счетчик 5, вычитатель 6, адресные регистры 7 и 8, два триггера 9 и 10, два шинных мультиплексных распределителя 11 и 12, линию 13 задержки, эле- мент 14 задержки и формирователь 15 выходного сигнала.

Блок 3 перестройки содержит регистры 16 и 17, коммутатор 18, двухтактный регистр 19. На фиг. 2-5 обозна- чены триггеры 20, мультиплексоры 21, дешифратор 22, схема 23 сравнения, сумматор 24, элементы И 25, элементы ИЛИ 26.

Генератор работает следующим образом.

С момента подачи питающего напряжения генератор автоматически приво- дится в исходное рабочее состояние

по команде Установка по питанию (Уст, по пит.). Работа генератора осуществляется по команде Пуск и прекращается по команде Останов, причем результат невыполненной операции сохраняется и может быть продолжен по команде Пуск. Приведение системы в исходное рабочее состояние в процессе работы осуществляется по команде начальной установки (Н.У.). На вход блока синхронизации поступае высокочастотная опорная частота (F0) кварцованного эталонного генератора, которая, минуя блок синхронизации, в последующем синхронизирует работу блоков 2,5,19,9,10 и 14. Таким образом, блок 4 является важным звеном в работе, поскольку обеспечивает синхронность выполнения внешних и внутренних команд.

Числовое значение кода, обрабатываемое блоком 5, определяет длительность следования импульсов на выходе генератора. Чем больше числовое значение этого кода, тем более значительное время отводится на перекодирование периода следования выходных импульсов, однако следует отметить, что максимальная частота функционирования блоков 2 и 5 в части перезаписи информации из одного блока в другой соответствует опорной частоте F0, сдвинутой во времени на величину Т/2, где Т - период эталонной частоты FO , а значение F,, ограничено функциональным быстродействием счетных схем.

Таким образом,достигнута возможность получения на выходе блока 5 высокочастотных серий перепрограммируемых импульсов в соответствии с заданным кодом поступления. В ряде случаев такой способ грубого задания периода импульсной последовательности является достаточным и широко используется в вычислительной технике при создании программируемых таймеров , синхронизирующих импульсов и ряда других функциональных узлов цифровой техники.

Регистры 2, 16 и 17 производят запись исходных кодируемых данных по внешнему импульсному сигналу записи (ИЗ) и обеспечивают по программе информацией блоки 5,6 и 18.

Регистр 19 по синхронизирующим импульсам с блока -4 производит хранение результата пересчета двух чис516

ловых кодируемых величин, одна из которых поступает на вычитатель 6 в качестве константы (вход 1), а другая является переменной величиной результата работы вычитателя (вход 2) Таким образом, блоки 17, 6, 18 и 19 задают числовое значение малой величины Д дискрета приращения ( Дл.пр ) из расчета разбиения опорной частоты FO на равные части (фиг. 4 и 6).

С целью уменьшения излишних схематических затрат целесообразно первоочередной задачей задаться высокой опорной частотой Fa , исходя из кото- рой в дальнейшем определить дискрет Aft.flp который может быть любым числом и составлять весьма малую величину. Кроме того, дискрет Д-р,, определяет разрядность вычитателя 6 и по- следующих блоков (таблица и фиг. 6).

Таким образом, &$ пр как.следует из таблицы, прямо зависит от выбранной частоты Гф, определяет схематические затраты и, кроме того, сама частота FO во многом определяет глубину перестройки периода следования импульсов на выходе узла 15.

В результате всего вышеизложенного целесообразно дальнейшую обработку сигнала вести на основе трехразряд- нога вычитателя и соответствующих трехразрядных последующих блоков.

Трехразрядный вычитатель 6 в нужные моменты времени стробирует работу счетчика 5, корректируя тем самым уход частоты. С регистра 17 на первый вход вычитателя 6 поступает запрограммированный код константы. Регистр 19, реализованный на двухтактных триггерах, осуществляет потактную син- хронную выдачу меняющегося кода вновь на вычитатель 6 и адресные регистры 7 и 8.

Коммутатор 18 производит работу шинного мультиплексирования, в ре- зультате чего по команде разрешения присинхронизации (Разр.пр.) производится присинхронизомия выходной тосле- ДОВЯТРТЬНОСТИ импульсов к некоторому

.Q

5 0

5

0

д

о

9

запрограммированнрму кодируемому значению, т.е. на серию импульсов запрограммированной последовательности накладывается как бы умышленный закодированный сбой. В результате этого вычитатель 6, по следующему син- хротакту, произведет новый пересчет двух кодируемых величин, результатом действия которых появится новый код на входе регистра 19. Дальнейшая обработка этого кода приводит к сдвигу выходной серии программируемых импульсов к некоторой величине кодируемого сдвига (фиг. 7). Аналогичным свойством присинхронности обладает и сче тчик 5.

Триггеры 9 и 10 вырабатывают синхронизирующие сигналы, причем триггер

10стробирует работу адресных регистров 7 и 8 и распределителей 11 и 12. Триггер 9 стробирует запись кода в адресные регистры 7 и 8. Выходные адресные коды с регистров 7 и 8 поступают в распределители 11 и 12.

Шинные мультиплексные распределители 11 и 12 выполняют функцию выбора соответствующей шины многоотводной линии задержки. Выходные сигналы с распределителей 11 и 12 поступают в формирователь 15, где окончательно и формируется выходной сигнал программируемой последовательности.

Таким образом, посредством методов чередования обрабатываемой последовательности кодируемых данных, по разнесенным во времени сннхротактам возникла возможность создания ПГЦ с широкими функциональными возможностями, кроме того, элемент 16 задержки задает смещение пускового сигнала и способствует согласованию задер-- жек, вызванных разбросом параметров элементной базы,связанный с их инертностью.

Формула изобретения

1, Программируемый генератор циклов, содержащий генератор эталонной частоты, блок синхронизации, блок перестройки, вычитатель, два триггера, элемент задержки, линию задержки, причем выход генератора эталонной частоты подключен к входу эталонной частоты блока синхронизации, выходы синхросигналов которого подключены соответственно к входам синхронизации блока перестройки, входу синхрониэадни первого триггера и входу элемент задержки, к счетному входу второго триггера, о тличающийся тем, что, с целью расширения класса решаемых задач за счет расширения области рабочих частот и дискрета задания их точности, в него введены регистр, счетчик, два адресных регистра, два шинных мультиплексных распределителя, формирователь выходного сигнала, причем вход данных генератора подключен к информационным входам регистра и первому информационному входу блока перестройки, вход разрешения присинхронизации которого подключен к входу разрешения присинхронизации генератора, входы установки по питанию начальной установки, пуска и останова которого подключе- ны к соответствующим входам блока синхронизации, выход эталонной частоты и строба записи которого подключены соответственно к входу синхронизации счетчика и управляющему вход регистра, выход которого подключен к входу параллельного приема информации счетчика, выход которого подключен к счетному входу первого триггера и входу присинхронизации блока пе рестройки, информационный выход которого подключен к информационным входам первого и второго адресных регистров и первому информационному входу вычитателя, второй информаци- онный вход которого подключен к выходу кода константы блока перестройки, второй информационный вход которого подключен к выходу вычитателя, выход переполнения которого подклю- чен к входам стробирования блока синхронизации и счетчика, выход первого триггера подключен к входам управпения записи первого и второго

адресных регистров, входы стробиро- вания выходов которых и входы строби- рования первого и второго шинных мультиплексных распределителей подключены соответственно к прямому и инверсному выходам второго триггера, выходы первого и второго адресных регистров подключены к входам управления первого и второго шинных мультиплексных распределителей, информационные входы которых подключены к выходам линии задержки, выходы первого и второго шинных мультиплексных распределителей - к первому и второму информационным входам формирователя выходного сигнала, вход установки длительности которого и выход подключены соответственно к входу установки длительности и функциональному выходу генератора.

щщюшо

ЪШШО

От еч г o II I I I I I I

§§§§§

ti

ISM E

W понродшоогони иодохпд j/

LJtZTK

n

N

на

. Г ц. 1Г И. 7 .1. 37 j. ЧТ ST ST 71вТ

Фиг б

П.

п

фигЛ

Фие.8

| Генератор циклов | 1979 |

|

SU877511A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для калибровки счетчика молний | 1975 |

|

SU564616A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-04-23—Публикация

1988-06-07—Подача