Nt

со

со

СП

О

31499

Изобретение относится к электросвязи и предназначено для улучшения качества воспроизведения сигналов в системах связи с линейной и адаптив- ной низкоскоростной дельта-модуляцией.

Целью изобретения является повышение точности коррекции.

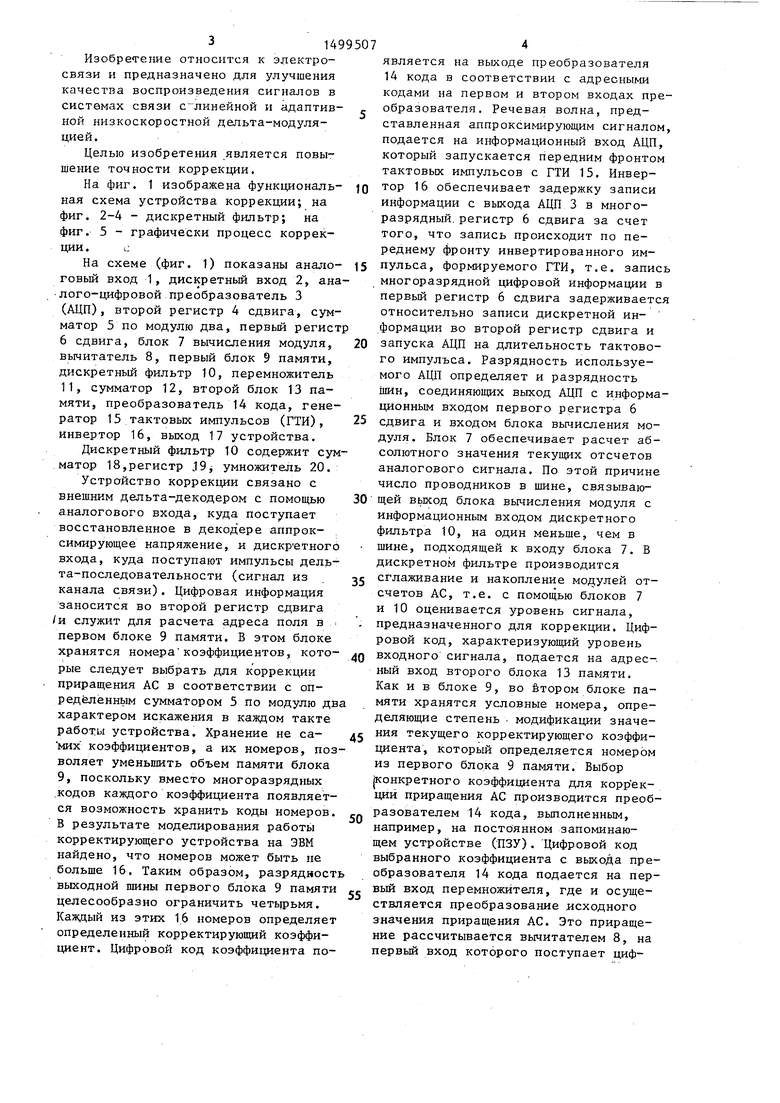

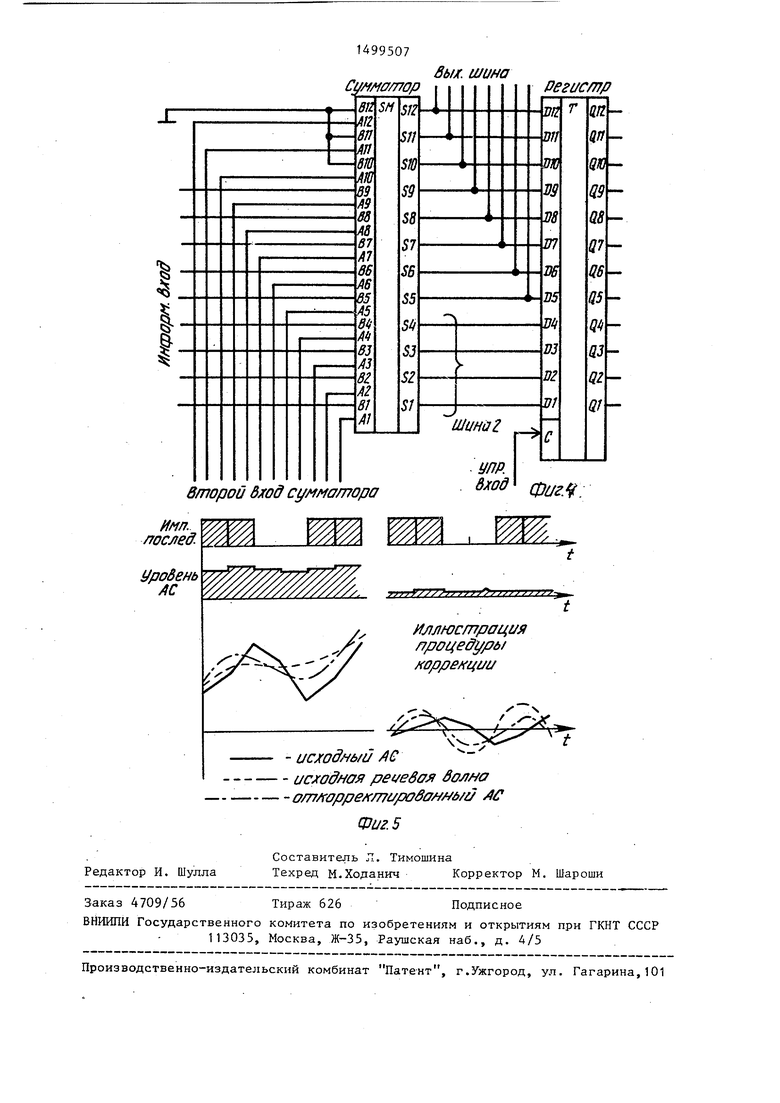

На фиг. 1 изображена функциональ- ная схема устройства коррекции; на фиг. 2-4 - дискретный фильтр; на фиг. 5 - графически процесс коррекции, с

На схеме (фиг. 1) показаны анало- говый вход 1, дискретньш вход 2, ана- лого-цифровой преобразователь 3 (АЦП), второй регистр 4 сдвига, сумматор 5 по модулю два, первьй регистр 6 сдвига, блок 7 вычисления модуля, вьиитатель 8, первый блок 9 памяти, дискретньш фильтр 10, перемножитель 11, сумматор 12, второй блок 13 памяти, преобразователь 14 кода, генератор 15 тактовых импульсов (ГТИ), инвертор 16, выход 17 устройства.

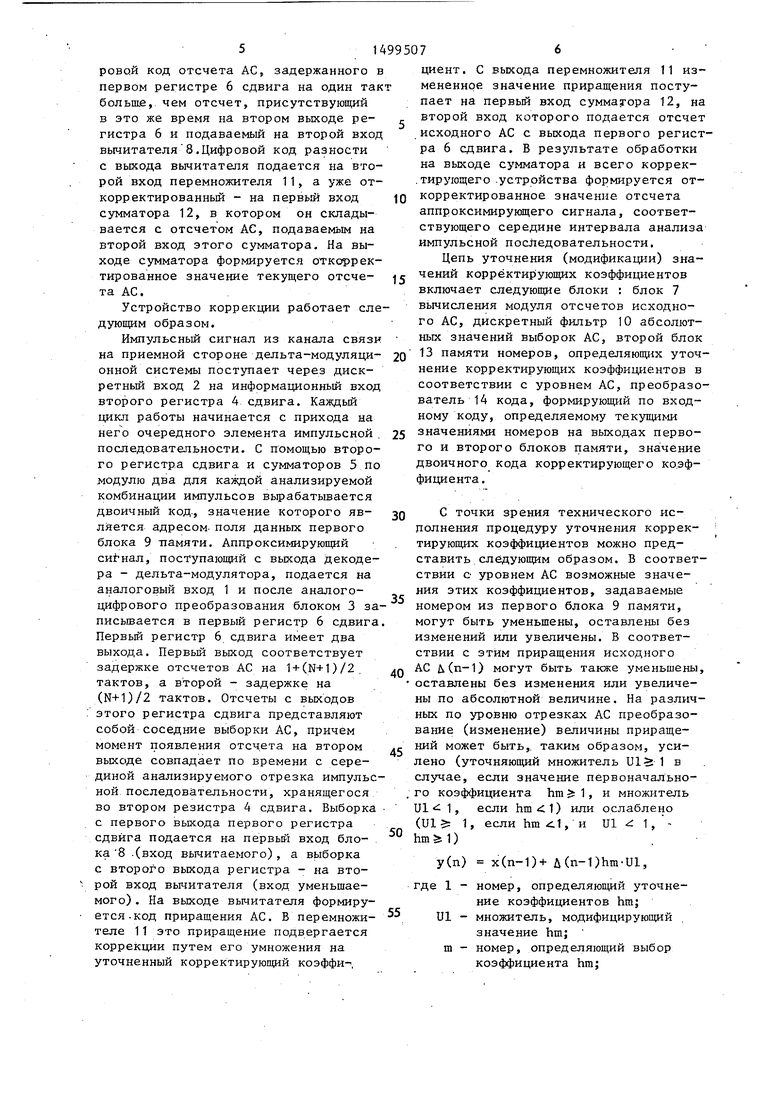

Дискретный фильтр 10 содержит сумматор 18,регистр ,19j умножитель 20.

Устройство коррекции связано с внешним дельта-декодером с помощью аналогового входа, куда поступает восстановленное в декодере аппроксимирующее напряжение, и дискр етного входа, куда поступают импульсы дельта-последовательности (сигнал из канала связи). Цифровая информация заносится во второй регистр сдвига /и служит для расчета адреса поля в первом блоке 9 памяти. В этом блоке хранятся номера коэффициентов, кото-

рые следует выбрать для коррекции приращения АС в соответствии с определенным сумматором 5 по модулю дв характером искажения в каждом такте работы устройства. Хранение не са- мих коэффициентов, а их номеров, позволяет уменьшить объем памяти блока 9, поскольку вместо многоразрядных .кодов каждого коэффициента появляется возможность хранить коды номеров, В результате моделирования работы корректирующего устройства на ЭВМ найдено, что номеров может быть не больше 16. Таким образом, разрядност выходной шины первого блока 9 памяти целесообразно ограничить четырьмя. Каждый из этих 16 номеров определяет определенный корректирующий коэффициент. Цифровой код коэффИ15иента появляется на выходе преобразователя 14 кода в соответствии с адресными кодами на первом и втором входах преобразователя. Речевая волна, представленная аппроксимирующим сигналом подается на информационный вход АЦП, который запускается передним фронтом тактовых импульсов с ГТИ 15. Инвертор 16 обеспечивает задержку записи информации с выхода АЦП 3 в многоразрядный, регистр 6 сдвига за счет того, что запись происходит по переднему фронту инвертированного импульса, формируемого ГТИ, т.е. запис многоразрядной цифровой информации в первьй регистр 6 сдвига задерживаетс относительно записи дискретной ин- формации во второй регистр сдвига и запуска АЦП на длительность тактового импульса. Разрядность используемого АЦП определяет и разрядность шин, соединяющих выход АЦП с информационным входом первого регистра 6 сдвига и входом блока вычисления модуля. Блок 7 обеспечивает расчет абсолютного значения текущих отсчетов аналогового сигнала. По этой причине число проводников в шине, связывающей вькод блока вычисления модуля с информационным входом дискретного фильтра 10, на один меньше, чем в шине, подходящей к входу блока 7. В дискретном фильтре производится сглаживание и накопление модулей отсчетов АС, т.е. с помощью блоков 7 и 10 оценивается уровень сигнала, предназначенного для коррекции. Цифровой код, характеризующий уровень входного сигнала, подается на адрес-- ный вход второго блока 13 памяти. Как и в блоке 9, во втором блоке памяти хранятся условные номера, определяющие степень модификации значения текущего корректирующего коэффициента, который определяется номером из первого блока 9 памяти. Выбор jKOHKpeTHoro коэффициента для коррекций приращения АС производится преобразователем 14 кода, выполненным, например, на постоянном запоминающем устройстве (ПЗУ). Цифровой код выбранного коэффициента с выхода преобразователя 14 кода подается на первый вход перемножителя, где и осуществляется преобразование исходного значения приращения АС. Это приращение рассчитывается вычитателем 8, на первьй вход которого поступает цифровой код отсчета АС, задержанного в первом регистре 6 сдвига на один так больше, чем отсчет, присутствующий в это же время на втором выходе регистра 6 и подаваемый на второй вход вычитателя 8.Цифровой код разности с выхода вычитателя подается на второй вход перемножителя 11, а уже от- корректированньш - на первый вход сумматора 12, в котором он складывается с отсчетом АС, подаваемым на второй вход этого сумматора. На выходе сумматора формируется откорректированное значение текущего отсчета АС.

Устройство коррекции работает следующим образом.

Импульсный сигнал из канала связи на приемной стороне дельта-модуляционной системы поступает через дискретный вход 2 на информационный вход второго регистра 4 сдвига. Каждьш цикл работы начинается с прихода на него очередного элемента импульсной последовательности. С помощью второго регистра сдвига и сумматоров 5 по модулю два для каждой анализируемой комбинации импульсов вырабатывается двоичный код, значение которого является адресом- поля данных первого блока 9 ттамяти. Аппроксимирующий , поступающий с выхода декодера - дельта-модулятора, подается на аналоговый вход 1 и после аналого- цифрового преобразования блоком 3 за письюается в первый регистр 6 сдвига Первьй регистр 6 сдвига имеет два выхода. Первый выход соответствует задержке отсчетов АС на 1+(N+1)/2. тактов, а второй - задержке на (N+1)/2 тактов. Отсчеты с выходов этого регистра сдвига представляют собой соседние выборки АС, причем момент появления отсчета на втором выходе совпадает по времени с серединой анализируемого отрезка импульсной последовательности, хранящегося во втором резистра 4 сдвига. Выборка с первого выхода первого регистра сдвига подается на первый вход блока 8 .(вход вычитаемого), а выборка с второго выхода регистра - на второй вход вычитателя (вход уменьшаемого) . На выходе вычитателя формируется, код приращения АС. В перемножителе 11 это приращение подвергается коррекции путем его умножения на уточненный корректирующий коэффи-,

5

циент. С выхода перемножителя 11 измененное значение приращения поступает на первьй вход сумматора 12, на второй вход которого подается отсчет исходного АС с выхода первого регистра 6 сдвига. В результате обработки на выходе сумматора и всего коррек- , тирующего .устройства формируется отQ корректированное значение отсчета аппроксимирующего сигнала, соответствующего середине интервала анализа импульсной последовательности.

Цепь уточнения (модификации) значений корректирующих коэффициентов включает следующие блоки : блок 7 вычисления модуля отсчетов исходного АС, дискретный фильтр 10 абсолют- ньк значений выборок АС, второй блок

0 13 памяти номеров, определяюЩ11х уточнение корректирующих коэффициентов в соответствии с уровнем АС, преобразователь 14 кода, формирующий по входному коду, определяемому текущими

5 значениями номеров на выходах первого и второго блоков памяти, зна чение двоичного кода корректирующего коэффициента.

С точки зрения технического исполнения процедуру уточнения коррек- тирующих коэффициентов можно представить следующим образом. Б соответствии с уровнем АС возможные значения этих коэффициентов, задаваемые номером из первого блока 9 памяти, могут быть уменьщены, оставлены без изменений или увеличены. В соответствии с этим приращения исходного АС Л(п-1) могут быть также уменьшены, оставлены без изменения или увеличены по абсолютной величине. На различных по уровню отрезках АС преобразование (изменение) величины приращений может быть,, таким образом, усилено (уточняющий множитель Ul 1 в случае, если значение первоначально- . го коэффициента hra 1, и множитель U1 « 1, если ) или ослаблено ( 1, если , и U1 1, 0 )

0

5

0

5

у(п) х(п-1)+ u(n-1)hm-Ul,

где 1 - номер, определяющий уточнение коэффициентов hm; U1 - множитель, модифицирующий

значение hm;

m - номер, определяющий выбор коэффициента hm;

7149

Д(п-1Т-исходное приращение отсчета х(п-1) аппроксимирующего сигнала.

Однако перемножение величин hm и U1 целесообразно заменить на непос- редственный отбор тех результирующих значений, которые получаются после перемножения. С этой целью первый .и второй блоки памяти хранят условные номера m и 1 а. преобразователь кода, получая их на своем входе, формирует общий корректирующий коэффициент, т.е. условные номера преобразуются блоком 14 в цифровые коды корректирующего коэффициента и участвуют в преобразовании отсчетов АС по формуле

у(п) х(п-1)+ A(n-.1)hra,l.

Для реализации первого регистра сдвига (многоразрядный регистр сдвига, блок 6) можно использовать сдвиговый регистр с последовательным входом; для реализации вычитателя (блок 8) - сумматор-вычитатель чисел. Для реализации блока вычисления модуля используется сумматор-вычитатель, в котором управление режимом (суммированием или вычитанием) производится знаковым разрядом цифрового кода об- рабатьшаемого отсчета. В случае отрицательного числа, поступакщего на блок вычисления модуля, старпшй знаковый разряд содержит логическую еди ницу. Поэтому блок переводится в режим вычитания. В случае положительного числа знаковьй разряд содержит логический нуль И схема осуществляет суммирование. Вторым операндом в это операции алгебраического сложения является число нуль, представленное соответствующим цифровым кодом 000.. .. .0. Поэтому при вычитании из -нуля отрицательного входного числа получается положительное число, а при сложении нуля с положительным входным числом это число не изменяется и является результатом обработки, т.е. блок 7 осуществляет опера- цию вычисления модуля.

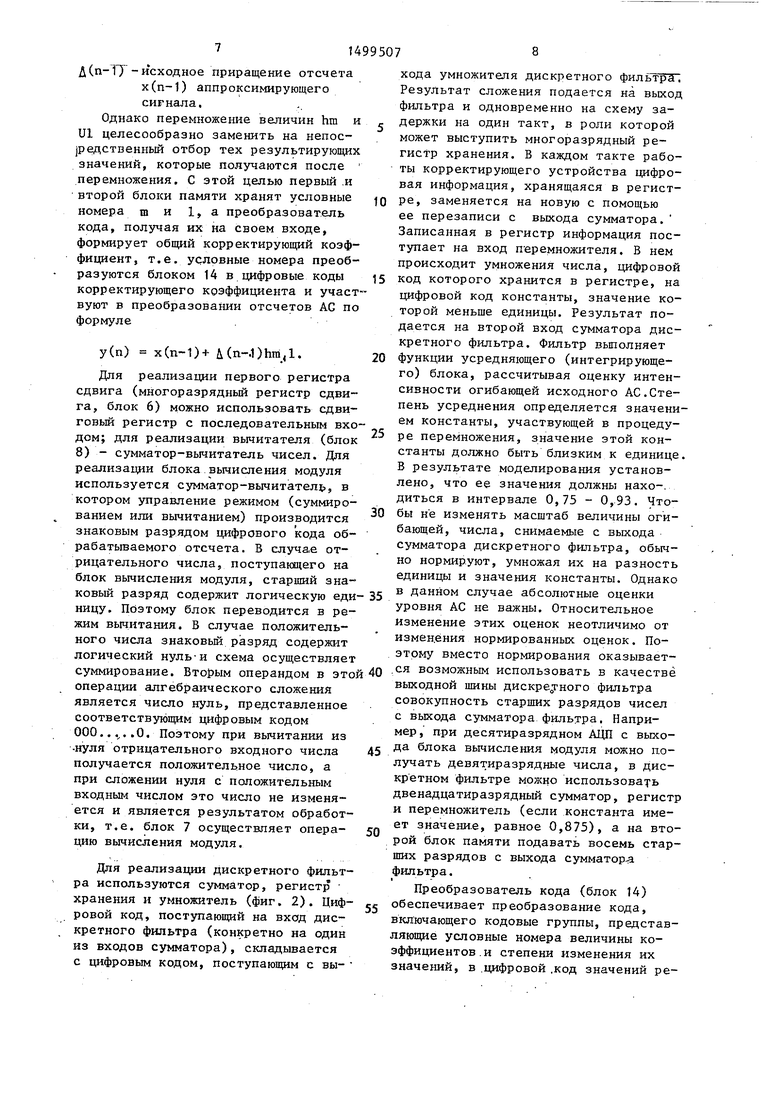

Для реализации дискретного фильтра используются сумматор, регистр хранения и умножитель (фиг. 2). Циф- ровой код, поступающий на вход дискретного фильтра (конкретно на один из входов сумматора), складывается с цифровым кодом, поступающим с вы-

Q 5

0

5

5 0 5 0

5

8

хода умножителя дискретного фильтра, Результат сложения подается на выход фильтра и одновременно на схему задержки на один такт, в роли которой может выступить многоразрядный регистр хранения. В каждом такте работы корректирующего устройства цифровая информация, хранящаяся в регистре, заменяется на новую с помощью ее перезаписи с выхода сумматора. Записанная в регистр информация поступает на вход перемножителя. В нем происходит умножения числа, цифровой код которого хранится в регистре, на цифровой код константы, значение которой меньше единицы. Результат подается на второй вход сумматора дискретного фильтра. Фильтр выполняет функции усредняющего (интегрирующего) блока, рассчитывая оценку интенсивности огибающей исходного АС.Степень усреднения определяется значением константы, участвующей в процедуре перемножения, значение этой константы должно быть близким к единице. В результате моделирования установлено, что ее значения должны нахо-. диться в интервале 0,75 - 0,93. Чтобы не изменять масштаб величины огибающей, числа, снимаемые с выхода сумматора дискретного фильтра, обьм- но нормируют, умножая их на разность единицы и значения константы. Однако в данном случае абсолютные оценки уровня АС не важны. Относительное изменение этих оценок неотличимо от измен.ёния нормированных оценок. Поэтому вместо нормирования оказывает- .ся возможным использовать в качестве выходной шины дискретного фильтра совокупность старших разрядов чисел с выхода сумматора фильтра, Например , при десятиразрядном АЦП с выхода блока вьиисления модуля можно получать девятиразрядные числа, в дискретном фильтре можно использовать двенадцатиразрядный сумматор, регистр и перемножитель (если константа имеет значени.е, равное 0,875), а на второй блок памяти подавать восемь старших разрядов с выхода сумматор-а фильтра.

I

Преобразователь кода (блок 14) обеспечивает преобразование кода, включающего кодовые группы, представляющие условные номера величины коэффициентов . и степени изменения их значений, в .цифровой .код значений результируюпщх корректирующих коэффициентов. Преобразователь кода может быть выполнен на постоянном запоминающем устройстве (блоке памяти), в котором адрес формируется из двух частей: условного номера коэффициента и условного номера степени изменения, и определяет то значение коэффициента, которое следует использовать при изменении приращения АС и которое должно храниться в этом блоке по этому адресу.

Процедура настройки предлагаемого устройства аналогична процедуре настройки известного и отличается лишь тем, что она более проста, так как N значений коэффициентов известного устройства, соответствующих конкретному адресу, взаимозависимы, что усложняет процесс их оптимизации, тогда как в предлагаемом устройстве каждому адресу m соответствует только один коэффициент. Процерующего сигнала, обеспечивает большую точность коррекции по сравнению с известным (отношение сигнал - шум повышается примерно на 1,5 дБ) в сочетании с меньшим объемом памяти постоянного запоминающего устройства, а также с менее сложной процедурой настройки весовых коэффициентов (корректирующих коэффициентов).

Формула изобретения

Устройство коррекции, содержащее последовательно соединенные генератор тактовых импульсов, аналого-цифровой преобразователь, информационный вход которого является аналоговым входом устройства коррекции, и первый регистр сдвига, последовательно соединенные перемножитель и сумматор, второй регистр сдвига, к управляющему входу которого подключен выход генератора тактовых и шульсов .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения взаимной корреляционной функции | 1990 |

|

SU1751779A1 |

| Цифровой измеритель коэффициента корреляции случайного сигнала | 2020 |

|

RU2747725C1 |

| Устройство для автоподстройки частоты | 1988 |

|

SU1653159A1 |

| Цифровой когерентный демодулятор сигналов с двоичной относительной фазовой манипуляцией | 2020 |

|

RU2748858C1 |

| Устройство коррекции | 1984 |

|

SU1252949A1 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ АДАПТИВНОЙ КОРРЕКЦИИ КВАДРАТУРНЫХ ДЕМОДУЛЯТОРОВ | 2000 |

|

RU2187140C2 |

| Адаптивный цифровой корректор | 1979 |

|

SU794734A1 |

| Передающее устройство адаптивной телеизмерительной системы | 1986 |

|

SU1501117A1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1990 |

|

SU1795475A1 |

| НЕКОГЕРЕНТНЫЙ ЦИФРОВОЙ ДЕМОДУЛЯТОР "В ЦЕЛОМ" КОДИРОВАННЫХ СИГНАЛОВ С ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2014 |

|

RU2556429C1 |

Изобретение относится к электросвязи. Цель изобретения -повышение точности коррекции. Устройство коррекции содержит АЦП 3, регистры 4 и 6 сдвига, сумматор 5 по модулю два, блок 7 вычисления модуля, вычитатель 8, блоки 9 и 13 памяти, дискретный фильтр 10, перемножитель 11, сум матор 12, преобразователь 14 кода, г-р 15 тактовых импульсов и инвертор 16. Цель достигается за счет обеспечения формирования откорректированного значения отсчета аппроксимирующего сигнала, соответствующего середине интервала анализа импульсной последовательности. 3 ил.

дура оптимизации параметров корректи- 25 информационный вход второго регистра

рующего устройства включает поиск значений коэффициентов при условии, что цепь уточнения по уровню аппрок- симизации сигнала не работает, оптимизацию значений этих коэффициентов с учетом уровня АС. Критерием качества работы устройства коррекции могут быть такие интегральные оценки, как величина отношения сигнал - шум, величина сегментного отношения сигнал - шум, величина относительной среднеквадратической ошибки восстановления или другие известные показатели. Оптимальные значения коэффициентов обеспечивают экстремум этих показателей. Кроме того, отношение сигнал - шум в любом дельта-кодекс ожет быть дополнительно увеличено утем оптимизации его параметров в случае, если кодекс работает с настоенным устройством коррекции.

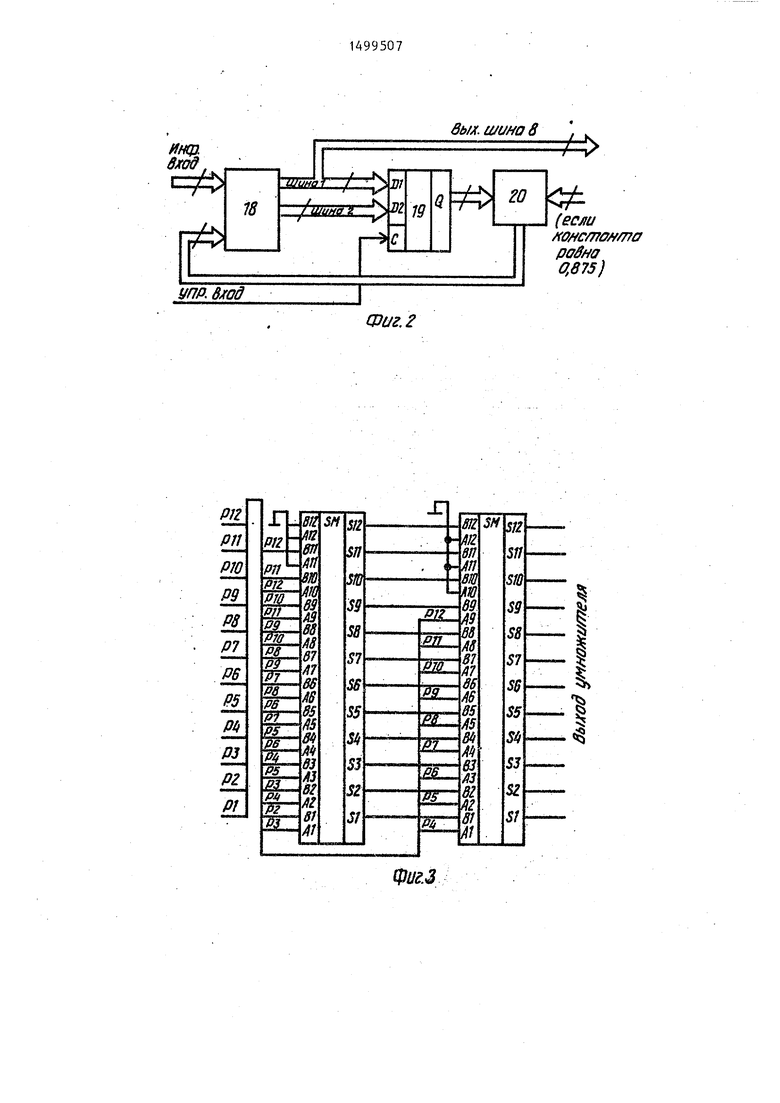

Процесс коррекции (фиг. 3) пока- зан на траекториях аппроксимирующего сигнала до коррекции и после коррекции с учетом комбинации дельта- импульсов и уровня сигнала.

Таким образом, предлагаемое устройства, использующее .принцип изменения значений отсчетов аппроксимисдвига является дискретным входом устройства коррекции, N-1 выходов второго регистра сдвига через N-1 сумматоров по модулю два, к вторым 0 входам которых подключен N-й выход второго регистра сдвига, подключены к N-1 входам первого блока памяти, а также второй блок памяти, о т.1 Л. и-;- чающееся тем, что, с повышения точности коррекции, введены преобразователь кода, вычита- тель, к входу вычитаемого которого и к второму входу сумматора подключен первый выход первого регистра сдвига, второй выход которого через вычита- тель подключен к -второму входу перемножителя, последов ательно соединенные блок вычисления модуля, к входу которого подключен выход аналого-цифрового преобр азователя, дискретный фильтр, выход которого подключен к первому гходу перемножителя чербз последовательно соединенные второй блок памяти и преобразователь кода, к второму входу которого подключен выход первого блока памяти, а также инвертор, к входу которого подключен генератор тактовых импульсов, а выход - к вторым входам первого регистра сдвига и дискретного фильтра.

5

0

5

0

5

шимаГ

5ЬЙ

:

18

/ шимаг

УПР, влод

PJL //

РЮ

EL EL

1 EL EL EL L

EL PI

вь/х.шимав

i

19

го

(если

/(O/fC/77O f77a

paffna 0.875)

Фиг, 2

иг.З

И/in. лослед.

. .

Уровень АС

Редактор И. Шулла

- uc;( С

ucjfodffOff болна

--om/foppe/f/77i/poeo 6/i/

Фиг. 5

Составитель Л. Тимошина

Техред М.Ходанич Корректор М. Шароши

вых. шина

Иллюстрация

лроцедурй/

/(оррещии

| Устройство коррекции | 1984 |

|

SU1252949A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-08-07—Публикация

1987-12-03—Подача