1

Изобретение относится к вычислительной технике и может быть использовано .при построении быстродействующих специализированных устройств и систем управления технологическими процессами.

Целью изобретения является повьппе- ние быстродействия.

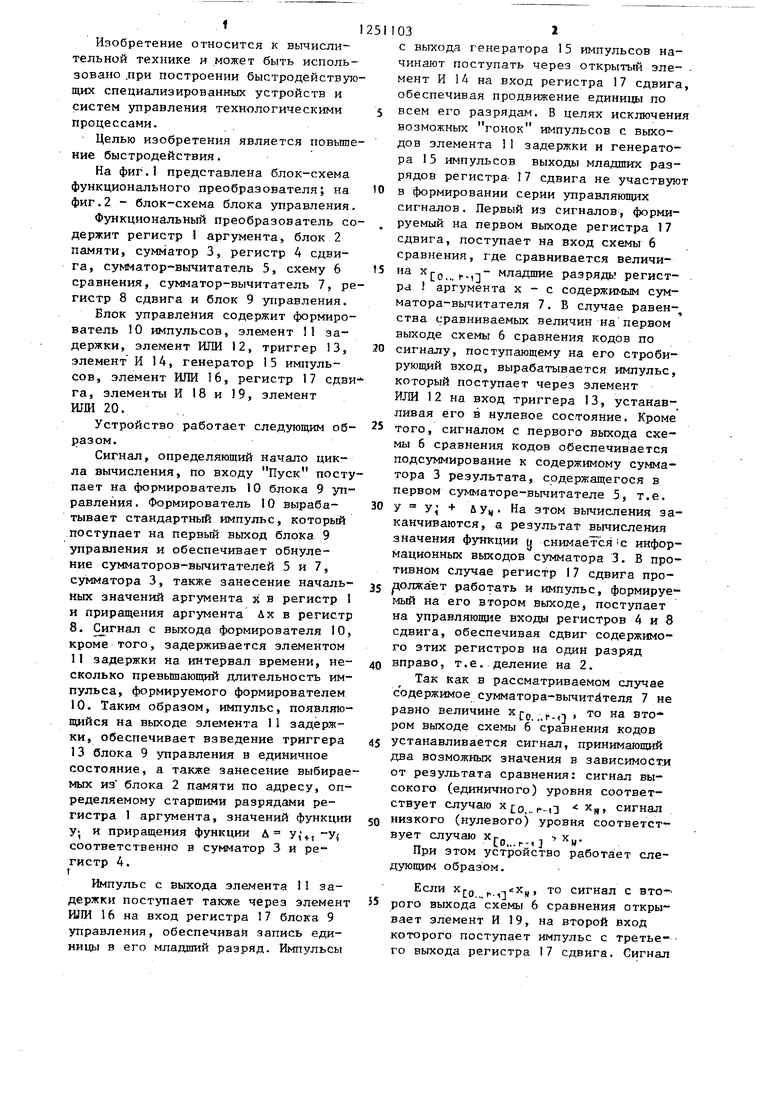

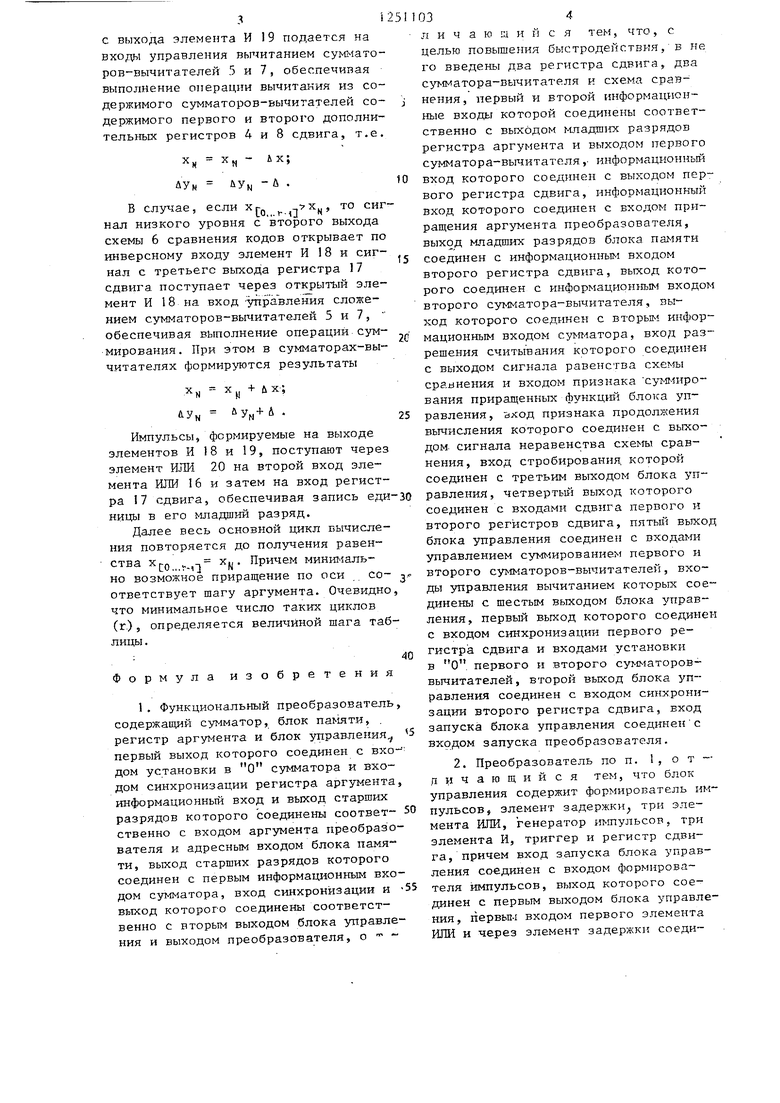

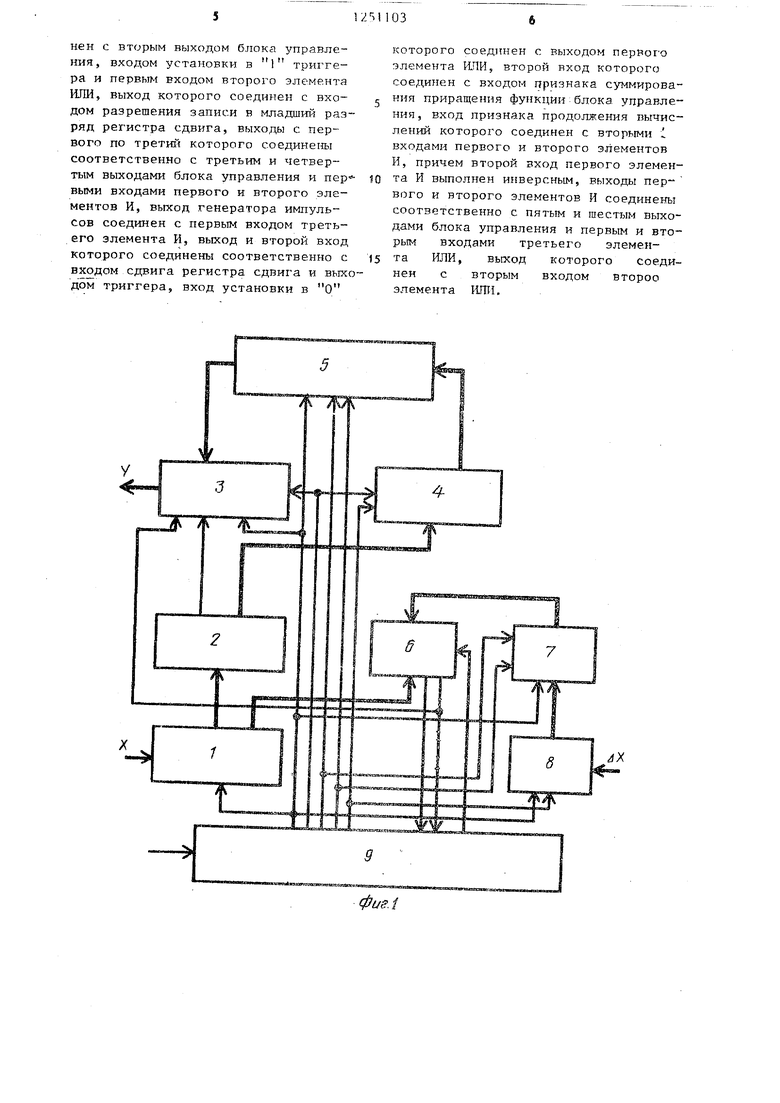

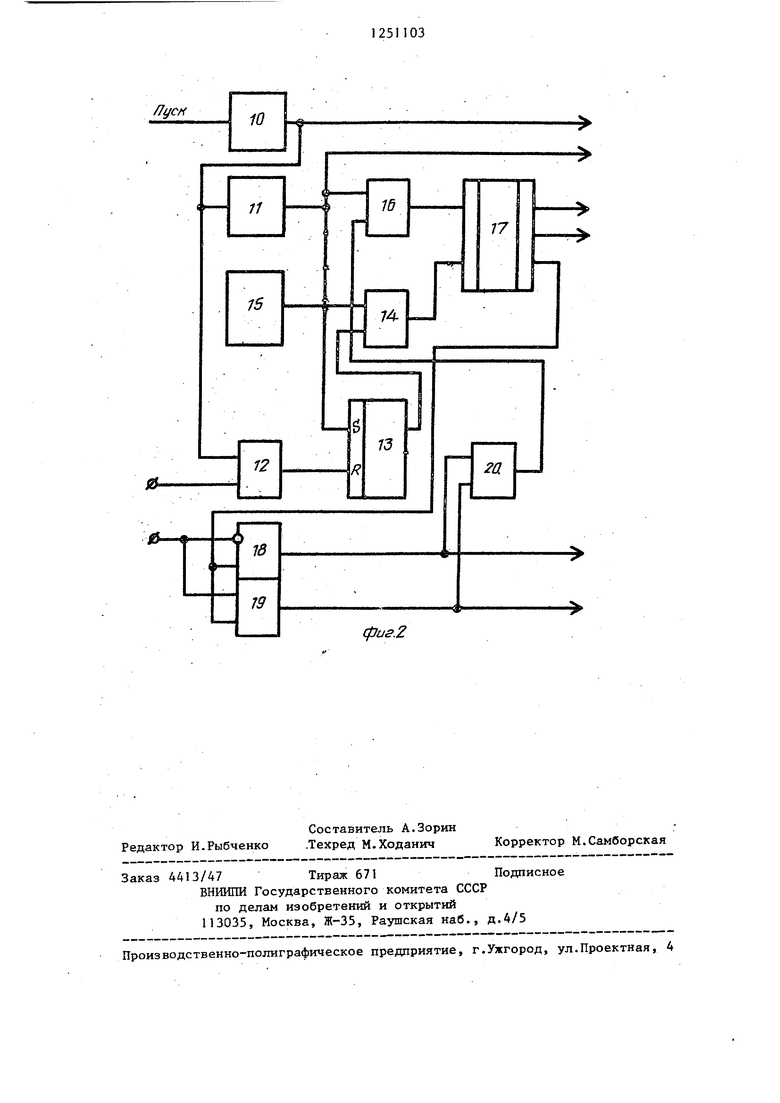

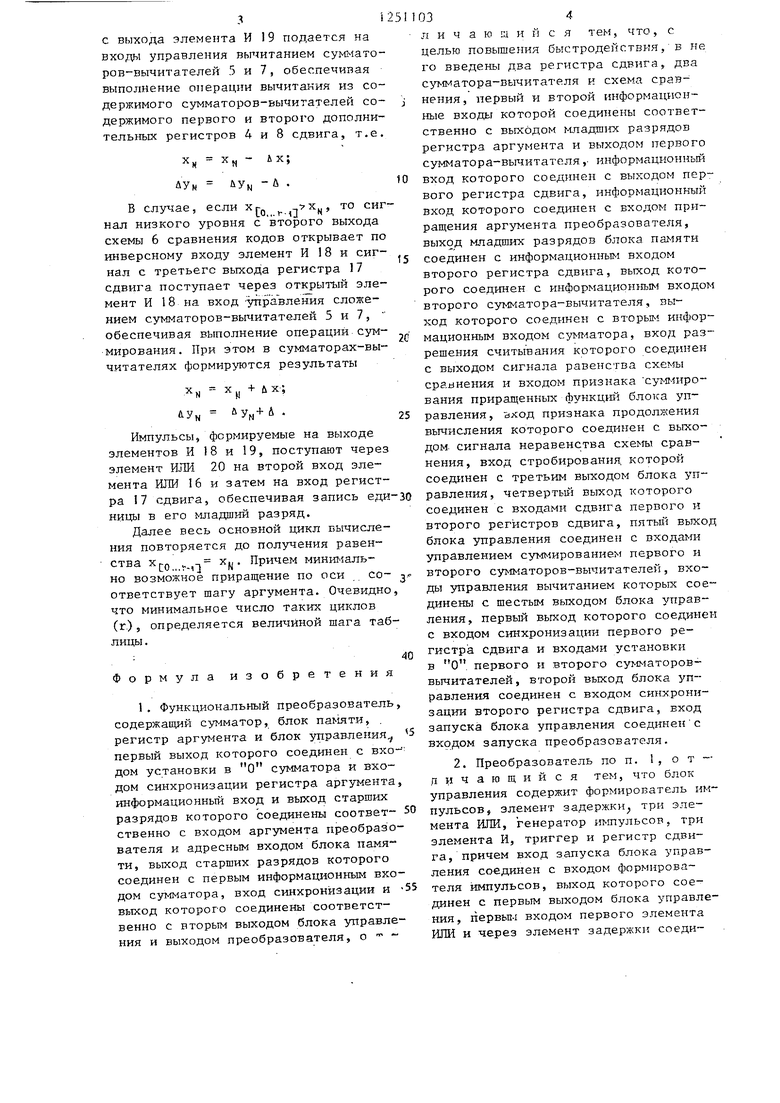

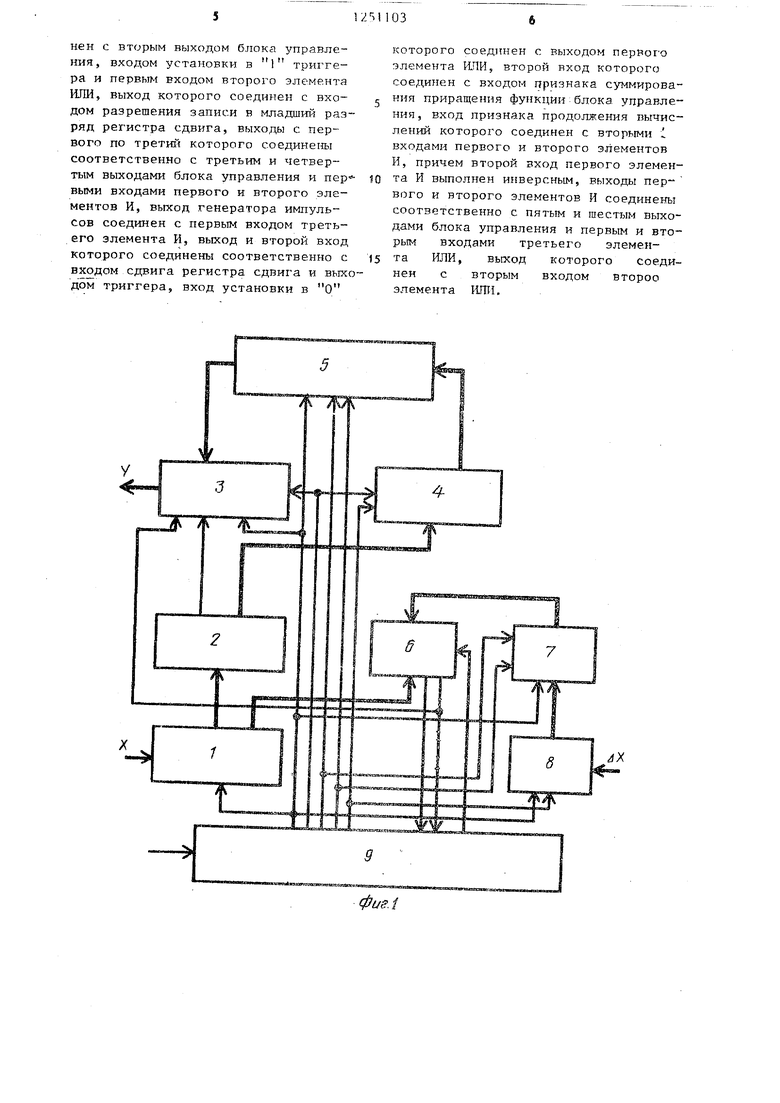

На фиг.1 представлена блок-схема функционального преобразователя; на фиг.2 - блок-схема блока управления.

Функциональный преобразователь содержит регистр 1 аргумента, блок 2 памяти, сумматор 3, регистр 4 сдвига, сумматор-вычитатель 5, схему 6 сравнения, сз мматор-вычитатель 7, регистр 8 сдвига и блок 9 управления.

Блок управления содержит формирователь 10 импульсов, элемент 11 задержки, элемент ИЛИ 12, триггер 13, элемент И 14, генератор I5 импульсов, элемент ИЛИ 16, регистр 17 сдвига, элементы И 18 и 19, элемент ИЛИ 20.

Устройство работает следующим образом.

Сигнал, определяющий начало цикла вычисления, по входу Пуск поступает на формирователь 10 блока 9 управления . Формирователь IО вырабатывает- стандартный импульс, который поступает на первый выход блока 9 управления и обеспечивает обнуле- кие сумматоров-вычитателей 5 и 7, сумматора 3, также занесение начальных значений аргумента х в регистр 1 и приращения аргумента Лх в регистр 8. Сигнал с выхода формирователя 10, кроме того, задерживается элементом 11 задержки на интервал времени, несколько превышающий длительность импульса, формируемого формирователем 10. Таким образом, импульс, появляющийся на выходе элемента 11 задержки, обеспечивает взведение триггера 13 блока 9 управления в единичное состояние, а также занесение выбираемых из блока 2 памяти по адресу, определяемому старшими разрядами регистра 1 аргумента, значений функции у. и приращения функции Д у,-, -У| соответственно в сумматор 3 И ре-

гистр 4. t

Импульс с выхода элемента 11 задержки поступает также через элемент ИЛИ 16 на вход регистра 17 блока 9 управления, обеспечивай запись единицы в его младший разряд. Импульсы

511032

с выхода генератора 15 импульсов начинают поступать через открытый эле- . мент И 14 на вход регистра 17 сдвига, обеспечивая продвижение единицы по

5 всем его разрядам. В целях исключения возможных гонок импульсов с выходов элемента 11 задержки и генератора 15 импульсов выходы младших разрядов регистра- 17 сдвига не y4acTBiTOT

О в формировании серии управляющих

сигналов. Первый из сигналов, форми руемый на первом выходе регистра 17 сдвига, поступает на вход схемы 6 сравнения, где сравнивается величиtS на .,. fM3 младщие разрядь регист- . ра 1 аргумента х - с содержимым сум- матора-вычитателя 7. В случае равенства сравниваемых величин на первом выходе схемы 6 сравнения кодов по

30 сигналу, поступающему на его строби- рующий вход, вырабатывается импульс, который поступает через элемент ИЛИ 12 на вход триггера 13, устанавливая его в нулевое состояние. Кроме

25 того, сигналом с первого выхода схемы 6 сравнения кодов обеспечивается подсуммироваиие к содержимому сумматора 3 результата, содержащегося в первом сумматоре-вычитателе 5, т.е.

30 у у, + йУч Ча этом вычисления заканчиваются, а результат вычисления значения функции у снимается с информационных выходов сумматора 3. В противном случае регистр 17 сдвига про35 должает работать и импульс, формируемый на его втором выходе, поступает на управляющие входы регистров 4 и 8 сдвига, обеспечивая сдвиг содержимого этих регистров на один разряд

40 вправо, т.е. деление на 2.

Так как в рассматриваемом случае содержимое сумматора-вычитйтеля 7 не равно величине Xj-, ,,-, , то на втором выходе схемы 6 сравнения кодов

45 устанавливается сигнал, принимающий два возможных значения в зависимости от результата сравнения: сигнал высокого (единичного) уровня соответствует случаю io,.. сигнал

5Q низкого (нулевого) уровня соответствует случаю Х|-. т Хц.

L Wii f J

При этом устройство работает следующим образом.

Если Xj-g р,«х, то сигнал с вто- 55 рого выхода схемы 6 сравнения открывает элемент И 19, на второй вход которого поступает импульс с третье-- го выхода регистра 17 сдвига. Сигнал

31251

с выхода элемента И 19 подается на входы управления вьп нтанием су№1ато- ров-вычитателей 5 и 7, обеспечивая выполнение операции вычитания из содержимого сумматоров-вычигателей со- j держимого первого и второго дополнительных регистров 4 и 8 сдвига, т.е.

ЛУм В случае, если Хг 7X.., то сигLQ.,. N

нал низкого уровня с второго выхода схемы 6 сравнения кодов открывает по инверсному входу элемент И 18 и сигнал с третьего выхода регистра 17 сдвига поступает через открытый элемент И 18 на вход -управления сложением сумматоров-вычитателей 5 и 7, обеспечивая выполнение операций суммирования. При этом в сумматорах-вы- читателях формируются результаты

X 11

ЛУ„ .

Импульсы, формируемые на выходе элементов И 18 и 19, поступают через элемент ИЛИ 20 на второй вход элемента ИЛИ 16 и затем на вход регистра 17 сдвига, обеспечивая запись единицы в его младший разряд.

Далее весь основной цикл вычисления повторяется до получения равенства XPQ «-,-) fj Причем минимально возможное приращение по оси со- ответствует шагу аргумента. Очевидно, что минимальное число таких циклов (г.) 5 определяется величиной шага таблицы .

Формула изобретения

1. Функциональный преобразователь, содержащий сумматор, блок , . регистр аргумента и блок управления первый выход которого соединен с входом установки в О сумматора и входом синхронизации регистра аргумента, информационный вход и выход старших разрядов которого соединены соответ- ственно с входом аргумента преобразователя и адресным входом блока памя ти, выход старших разрядов которого соединен с первым информационным входом сумматора, вход синхронизации и выход которого соединены соответственно с вторым выходом блока управления и выходом преобразователя, о

j

fO

5

С

5

о

0

5 0 5

1034

л и ч а ю а и и с я тем, что, с целью повышения быстродействия, в не го введены два регистра сдвига, два сумматора-вычитателя и схема сравнения, первый и второй информационные входы которой соединены соответственно с вьпсодом младших разрядов регистра аргумента и выходом первого сумматора-вычитателя , информационный вход которого соединен с выходом первого регистра сдвига, информационный вход которого соединен с входом приращения аргумента преобразователя, выход младших разрядов блока памяти соединен с информационным входом второго регистра сдвига, выход которого соединен с информационным входом второго сумматора-вычитателя, выход которого соединен с вторым информационным входом сумматора, вход разрешения считывания которого соединен с выходом сигнала равенства схемы сравнения и входом признака сумг-птро- вания приращенных функцш блока управления, вход признака продолжения вычисления которого соединен с выходом, сигнала неравенства схемы сравнения, вход стробирования. которой соединен с третьим выходом блока управления, четвертьш выход которого соединен с входами сдвига первого и второго регистров сдвига, пятьш вьтход блока управления соедине: с входами управлением суммированием первого и второго cy шaтopoв-вычитaтeлeй, входы управления вычитанием которых соединены с шестым выходом блока управления, первый выход которого соединен с входом С1Шхронизацни первого регистра сдвига и входами установки в о первого и второго сумматоров- вычитателей, второй выход блока управления соединен с входом синхронизации второго регистра сдвига, вход запуска блока управления соединен с входом запуска преобразователя.

2. Преобразователь по п. 1, о т - ,ti и ч а ю щ и и с я тем, что блок управления содержит формирователь импульсов, элемент задержки три элемента ИЛИ, генератор импульсов, три элемента И, триггер и регистр сдвига, причем вход запуска блока управления соединен с входом формирователя импульсов, выход которого соединен с первым выходом блока управления , первьш входом первого элемента ИЛИ и через элемент задержки соединен с вторым выходом блока управления, входом установки в l триггера и первым входом второго элемента ИЛИ, выход которого соединен с входом разрешения записи в младший разряд регистра сдвига, выходы с первого по третий которого соединены соответственно с третьим и четвертым выходами блока управления и пер выми входами первого и второго элементов И, выход генератора импульсов соединен с первым входом третьего элемента И, выход и второй вход которого соединены соответственно с входом сдвига регистра сдвига и выхдом триггера, вход установки в О

У

5

которого соединен с выходом первог о элемента ИЛИ, второй вход которого соединен с входом признака суммирования приращения функцииблока управления , вход признака продолжения вычислений которого соединен с вторыми i входами первого и второго элементов И, причем второй вход первого элемента И выполнен инверсным, выходы пер- вого и второго элементов И соединены соответственно с пятым и шестым выходами блока управления и первым и вторым входами третьего элемента ИЛИ, выход которого соединен с вторым входом второо элемента ИПИ,

4

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь | 1986 |

|

SU1339554A1 |

| Функциональный преобразователь | 1991 |

|

SU1807498A1 |

| Функциональный преобразователь | 1988 |

|

SU1541629A1 |

| Устройство для извлечения квадратного корня | 1988 |

|

SU1569827A1 |

| Устройство для извлечения квадратного корня | 1989 |

|

SU1658150A2 |

| Интерполятор | 1988 |

|

SU1541557A1 |

| Устройство для вычисления математического ожидания | 1986 |

|

SU1322315A1 |

| Интерполятор | 1987 |

|

SU1413602A1 |

| Цифровой функциональный преобразователь Анишина | 1983 |

|

SU1157543A1 |

| Цифровой функциональный преобразователь | 1984 |

|

SU1188750A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении быстродей г- ствующих специализированных устройств и систем управления технологическими процессами. Целью изобретения .является повышение быстродействия. Уст-- ройство содержит регистр аргумента, блок памяти, сумматор, два суммато- ра-вычитателя, два регистра сдвига, схему сравнения и блок управления. . Достижение поставленной цели обеспечивается исключением операции умножения . 1 3.п.ф-лы. 2 ил. ь ю bi

А/

8

х

фиг. /

/JycH

10

75

12

0-.

Редактор И.Рыбченко

Составитель А.Зорин .Техред М.Ходанич

Заказ 4413/47 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.А/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

2a

cpus.Z

Корректор М.Самборская

| Петров В.П | |||

| Проектирование цифровых систем | |||

| М.: Машиностроение, 1967, с | |||

| Приспособление для нагрузки тендеров дровами | 1920 |

|

SU228A1 |

| Оранский A.M | |||

| Аппаратные методы в цифровой вычислительной технике | |||

| Минск, изд-во ВГУ им | |||

| Б.И.Ленина, .1977, с | |||

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1986-08-15—Публикация

1985-02-18—Подача