11

ш

ел

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел | 1985 |

|

SU1287149A1 |

| Устройство для деления двоичных чисел | 1985 |

|

SU1325466A1 |

| Устройство для деления чисел с фиксированной запятой | 1986 |

|

SU1417009A1 |

| Устройство для деления чисел | 1980 |

|

SU857977A1 |

| Устройство для деления | 1985 |

|

SU1357946A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Устройство для определения аргумента вектора | 1986 |

|

SU1319024A1 |

| Устройство для деления | 1985 |

|

SU1282117A1 |

| Устройство для деления двоичных чисел | 1988 |

|

SU1617437A1 |

| Устройство для деления | 1984 |

|

SU1249551A1 |

Изобретение .относится к вычислительной технике и может быть использовано при построении универсальных и специализированных цифровых вычислительных машин. Целью изобретения является сокращение аппаратурных затрат. Эта цель достигается тем, что в устройство для деления чисел, содержащее три регистра 2, П, 17, сутчматор 6, коммутатор 5, блок 12 памяти, элемент ИЛИ 13, введены элементы ИЛИ 14, 15, триггер 8, сумматор 16 г соответствующими связями. 2 ил., 1 табл.

О5

ел

00 00

со

1465883

Изобретение .относится к вычислительной технике и может быть использовано при разработке параллельных цифровьсх вычислительных машин. ,

Цель изобретения - сокращение аппаратурных затрат.

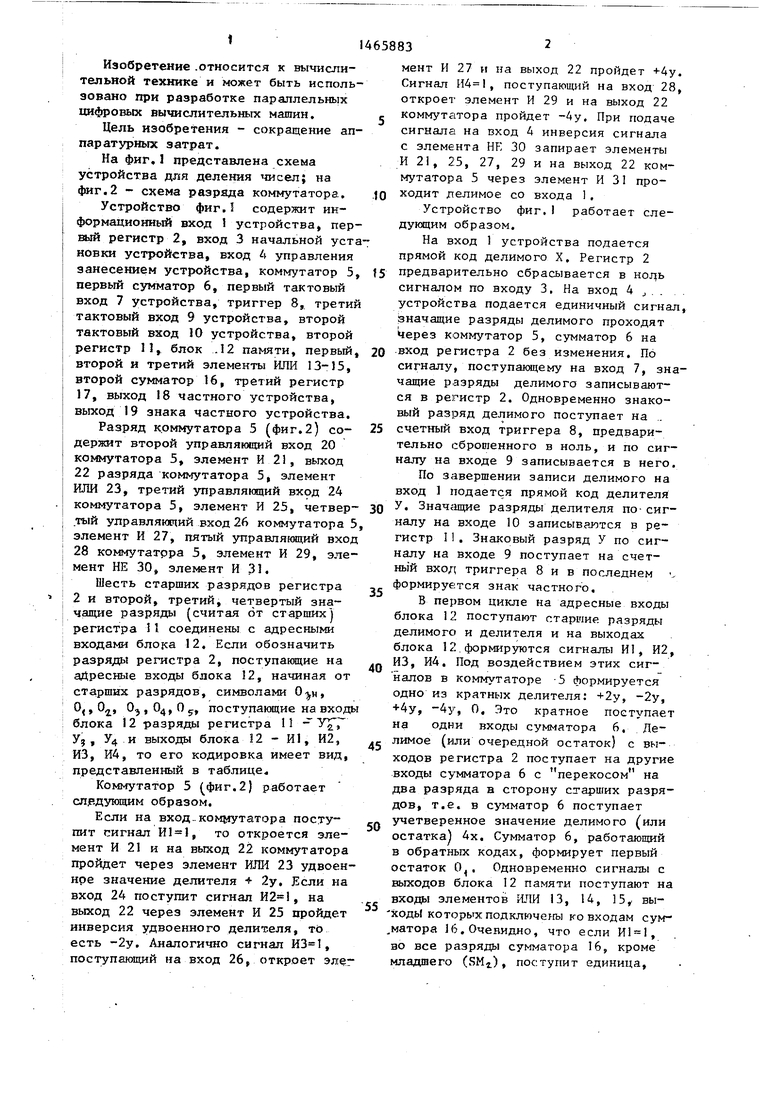

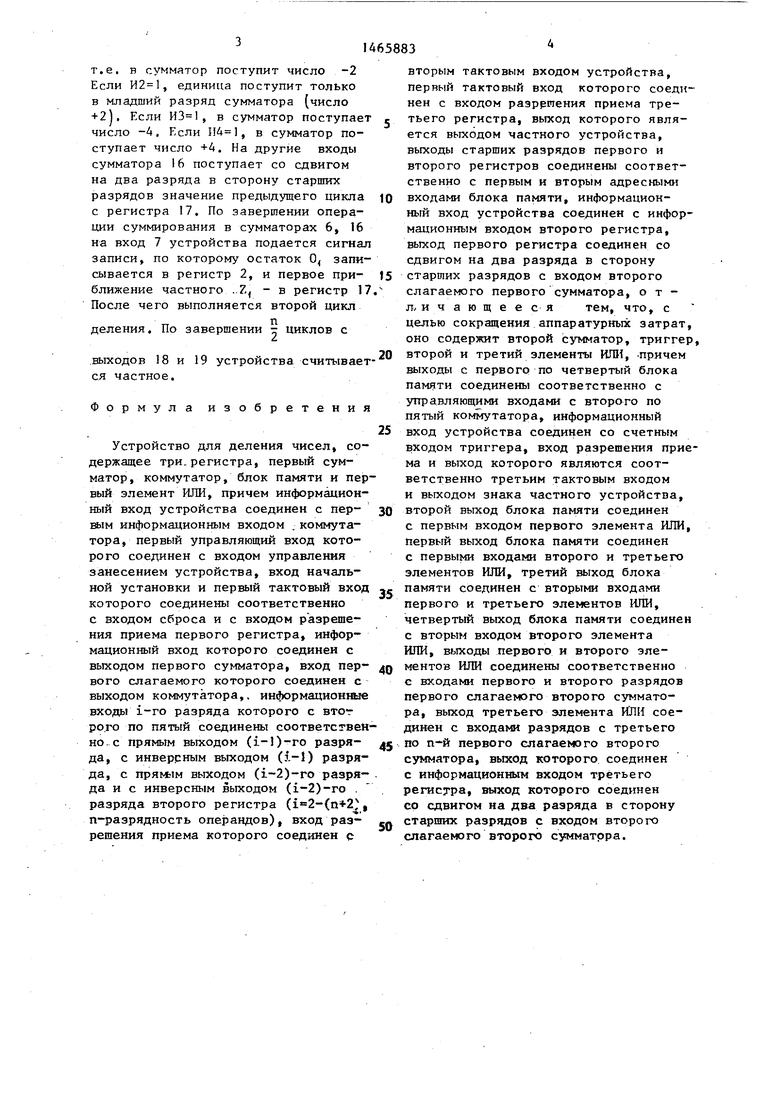

На фиг,1 представлена схема устройства для деления шсел; на фиг.2 - схема разряда коммутатора. .}о

Устройство фиг. содержит информационный вход 1 устройства, первый регистр 2, вход 3 начальной установки устройства, вход 4 управления

занесением устройства, коммутатор 5, 15 предварительно сбрасывается в первый сумматор 6, первый тактовый сигналом по входу 3. На вход 4 вход 7 устройства, триггер 8, третий тактовый вход 9 устройства, второй тактовый вход Ш устройства, второй регистр 11, блок .12 памяти, первый, 20 второй и третий элементы ИЛИ 13-15, второй сумматор 16, третий регистр 17, выход 18 частного устройства, выход 19 знака частного устройства.

Разряд коммутатора 5 (фиг.2) со- 25 держит второй управляющий вход 20 коммутатора 5, элемент И 21, выход 22 разряда коммутатора 5, элемент

ИЛИ 23, третий управлякщий вход 24 ., ..„„ ...„

коммутатора 5, элемент И 25, четвер- 30 Значгицие разряды делителя по-сиг- .тый управляюртий вход 26 коммутатора 5, налу на входе 10 записываится в ре- элемент И 27, пятый управляющий вход 28 коммутатрра 5, элемент И 29, элемент НЕ 30, элемент И 31.

Шесть старших разрядов регистра 2 и второй, третий, четвертый значащие разряды (считая от старших регистра 11 соединены с адресными входами блока 12. Если обозначить разряды регистра 2, поступающие на адресные входы блока 12, начиная от старших разрядов, символами , О,, 0,j, О, , 64, О у, поступающие на входы блока 12 разряды регистра П - У, У4 и выходы блока 32 - И1, И2, ИЗ, И4, то его кодировка имеет вид, представленный в таблице.

Коммутатор 5 (фиг.2) работает

мент И 27 и на выход 22 пройдет +4У Сигнал И4, поступающий на вход 28 откроет элемент И 29 и на выход 22 коммутатора пройдет -4у. При подаче сигнала на вход 4 инверсия сигнала с элемента НЕ 30 запирает элементы И 21, 25, 27, 29 и на выход 22 коммутатора 5 через элемент И 31 проходит делимое со входа 1,

Устройство фиг.I работает следующим образом.

На вход 1 устройства подается прямой код делимого X. Регистр 2

устройства подается единичный сигнал значащие разряды делимого проходят |через коммутатор 5, сумматор 6 на вход регистра 2 без изменения. По сигналу, поступающему на вход 7, зна чащие разряды делимого записываются в регистр 2. Одновременно знаковый разряд делимого поступает на счетный вход триггера 8, предварительно (:бров1енного в ноль, и по сигналу на входе 9 записывается в него. По завершении записи делимого на вход 1 подается прямой код делителя

слрдующим образом.

ЕСЛИ на вход..коммутатора поступит сигнал , то Откроется элемент И 21 и на выход 22, коммутатора пройдет через элемент ИЛИ 23 удвоен- нре значение делителя + 2у. Если на вход 24 поступит сигнал , на выход 22 через элемент И 25 пройдет инверсия удвоенного делит.еля, то есть -2у. Аналогично сигнал , поступакяций на вход 26, откроет элег

гистр I1. Знаковый разряд У по сигналу на входе 9 поступает на счет- ны й вход триггера Вив последнем . формируется знак частного.

В первом цикле на адресные входы блока 12 поступают старшие разряды делимого и делителя и на выходах блока 12.формируются сигналы И1, И2, ИЗ, И4. Под воздействием этих сигналов в коммутаторе -5 формируется одно из кратных делителя: +2у, -2у, , -4у, О, Это кратное поступает на одни входы сумматора 6. Де- дд лимое (или очередной остаток) с выходов регистра 2 поступает на другие входы сумматора 6 с перекосом на два разряда в сторону старших разря35

40

дов, т.е. в сумматор 6 поступает ,Q учетверенное значение делимого (или остатка 4х. Сумматор 6, работающий в обратных кодах, формирует первый остаток 0. Одновременно сигналы с выходов блока 12 памяти поступают на входы элементов ИЛИ 13, 14, 15, вы- ходьГ которых подключогы ко входам сум- матора 16. Очевидно, что если И1 1, во все разряды сумматора 16, кроме младшего (SMj.), поступит единица.

55

предварительно сбрасывается в сигналом по входу 3. На вход 4

мент И 27 и на выход 22 пройдет +4У. Сигнал И4, поступающий на вход 28, откроет элемент И 29 и на выход 22 коммутатора пройдет -4у. При подаче сигнала на вход 4 инверсия сигнала с элемента НЕ 30 запирает элементы И 21, 25, 27, 29 и на выход 22 коммутатора 5 через элемент И 31 проходит делимое со входа 1,

Устройство фиг.I работает следующим образом.

На вход 1 устройства подается прямой код делимого X. Регистр 2

предварительно сбрасывается в сигналом по входу 3. На вход 4

., ..„„ ...„

Значгицие разряды делителя по-сиг- налу на входе 10 записываится в ре-

устройства подается единичный сигнал значащие разряды делимого проходят |через коммутатор 5, сумматор 6 на вход регистра 2 без изменения. По сигналу, поступающему на вход 7, значащие разряды делимого записываются в регистр 2. Одновременно знаковый разряд делимого поступает на счетный вход триггера 8, предварительно (:бров1енного в ноль, и по сигналу на входе 9 записывается в него. По завершении записи делимого на вход 1 подается прямой код делителя

30 Значгицие разряды делителя по-сиг- налу на входе 10 записываится в ре-

гистр I1. Знаковый разряд У по сигналу на входе 9 поступает на счет- ны й вход триггера Вив последнем . формируется знак частного.

В первом цикле на адресные входы блока 12 поступают старшие разряды делимого и делителя и на выходах блока 12.формируются сигналы И1, И2, ИЗ, И4. Под воздействием этих сигналов в коммутаторе -5 формируется одно из кратных делителя: +2у, -2у, , -4у, О, Это кратное поступает на одни входы сумматора 6. Де- д лимое (или очередной остаток) с выходов регистра 2 поступает на другие входы сумматора 6 с перекосом на два разряда в сторону старших разря35

0

дов, т.е. в сумматор 6 поступает Q учетверенное значение делимого (или остатка 4х. Сумматор 6, работающий в обратных кодах, формирует первый остаток 0. Одновременно сигналы с выходов блока 12 памяти поступают на входы элементов ИЛИ 13, 14, 15, вы- ходьГ которых подключогы ко входам сум- матора 16. Очевидно, что если И1 1, во все разряды сумматора 16, кроме младшего (SMj.), поступит единица.

5

т.е. в сумматор поступит число -2 ЕСЛИ , единица поступит только в младший разряд сумматора (число +2), Если , в сумматор поступает число -4. ЕСЛИ И4, в сумматор поступает число +4. На другие входы сумматора 16 поступает со сдвигом на два разряда в сторону старших разрядов значение предыдущего цикла с регистра 17. По завершении операции суммирования в сумматорах 6, 16 на вход 7 устройства подается сигнал записи, по которому остаток О, записывается в регистр 2, и первое при- ближение частного ..Z - в регистр 17 После чего выполняется второй цикл

ттП

деления. По завершении - циклов с

.выходов 18 и 19 устройства считывается частное.

Формула изобретения

Устройство для деления чисел, содержащее три.регистра, первый сумматор, коммутатор, блок памяти и первый элемент ИЛИ, причем информационный вход устройства соединен с пер- вым информационным входом . коммутатора, первый управляющий вход которого соединен с входом управления занесением устройства, вход начальной установки и первый тактовый вход которого соединены соответственно с входом сброса и с входом разрешения приема первого регистра, информационный вход которого соединен с выходом первого сумматора, вход пер- вого слагаемого которого соединен с выходом коммутатора,, информационшда входы i-ro разряда которого с втог рого по пятый соединены соответственно, с прямым выходом (i-J)-ro разря- да, с инверрным выходом (з.-1) разряда, с прямым выходом (i-2)-ro разря- да и с инверсным выходом (i-2)-ro . разряда второго регистра ((n+2, п-разрядность опе зандов), вход раз- решения приема которого соединен с

вторым тактовым входом устройства, первый тактовый вход которого соединен с входом разррпения приема третьего регистра, выход которого является выходом частного устройства, выходы старших разрядов первого и второго регистров соединены соответственно с первым и вторым адресными входами блока памяти, информационный вход устройства соединен с информационным входом второго регистра, выход первого регистра соединен со сдвигом на два разряда в сторону старших разрядов с входом второго слагаемого первого сумматора, о т - л. ичающееся тем, что, с целью сокращения аппаратурных затрат оно содержит второй сумматор, тригге второй и третий элементы ИЛИ, -причем выходы с первого по четвертый блока памяти соединены соответственно с управляющими входами с второго по пятый коммутатора, информационный вход устройства соединен со счетным входом триггера, вход разрешения прима и выход которого являются соответственно третьим тактовым входом и выходом знака частного устройства, второй выход блока памяти соединен с первым входом первого элемента ИЛИ первый выход блока памяти соединен с первыми входами второго и третьего элементов ИЛИ, третий выход блока памяти соединен с вторыми входами первого и третьего элементов ИЛИ, четвертый выход блока памяти соедине с вторым входом второго элемента ШШ, выходы первого и второго элементов ИЛИ соединены соответственно с входами первого и второго разрядов первого слагаемого второго сумматора, выход третьего элемента соединен с входами разрядов с третьего по п-й первого слагаемого второго сумматора, выход которого соединен с информационным входом третьего регистра, выход которого соединен со сдвигом на два разряда в сторону старших разрядов с входом второго слагаемого второго сумматора.

| Устройство для деления двоичных чисел | 1981 |

|

SU1008733A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления чисел с фиксированной запятой | 1986 |

|

SU1417009A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

Авторы

Даты

1989-03-15—Публикация

1987-04-23—Подача