ру

№ 7 5.3

(Л

о о

со

Изобретение Рзтйосится к вычислительной технике и может быть использовано при создании специапизирован- ных систем переработки информации,

Цепью изобретения является сокращение аппаратурных затрат.

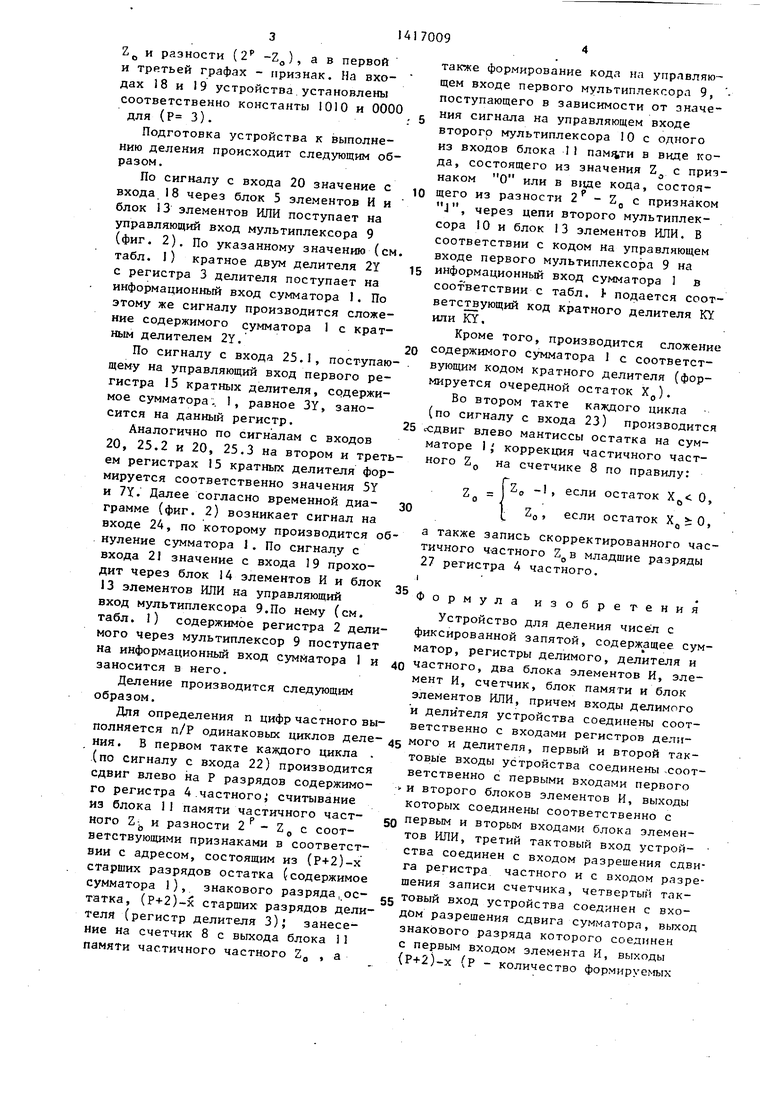

На фиг. 1 изображена схема устройства для деления чисел с фиксированной запятой (для Р З); на фиг. 2 - временная диаграмма поступления тактовых импульсов на входы устройства (для Р 3, где Р - ко- дичество формируемых разрядов частного) . Устройство содержит сумматор 1, регистры делимого 2, делителя 3, частного 4, блок 5 элементов И, элемент ИЛИ 6, элемент И 7, счетчик 8, мультиплексоры 9 и 10, блок 11 па- пяти, элемент 12 задержкл, блок 3 Элементов ИЛИ, блок 14 элементов И, группу регистров 15 кратных делителя вход 16 делителя устройства, вход 17 делимого устройства, входы 18 и 19. константы устройства, тактовые входы 20-24 устройства, группу тактовых входов 25.1-25.3 устройства, выход 26 частотного устройства, младшие рпзряды 27 регистра 4 частотного, знаковый разряд 28 сумматора 1, старшие разряды 29 сумматора , старшие разряды 30 регистра 3 делителя.

В устройстве действия производятся над числами с запятой, фиксированной перед старшим разрядом, Делитель нормирован, и выполняются условия ,5; Xi-Y, где X - делимое (остаток), Y - делитель.

Предварительно для всех комбинаций, усеченных до (Р-(-2)-х старших разрядов, остатка Х, и делителя YQ получают частное Z. Частичное частное ZQполучают от Z путем усечения его до Р старших разрядов с предварительным добавлением в (Р+1)-й отбрасываемый разряд единицы.

Абсолютная ошибка определения частичного частного равна

Хо . „-P-I Хо+ йХ

z f

IQ

f 2

YO

uY

, (1)

,-р

где О iXi 2

Численное значение деляется выражением

uZ « 2

р

(2)

Из формулы (2) следует, что час,- тичное частное, полученное таким образом, равно его точному значению или больше на единицу младшего разряда.

На этапе получения частичных разрядов ZQ для соответствующих Х, Ye получают отрицательный остаток и разность 2 -Zg.

В блок памяти по адресам Х, Yg записьшают соответствующие частичные частные Z, а по адресам. (Х,- Y ) разности ( ZQ) .

Перед циклом деления формируются и записываются на выполненные регистры значения частичных сумм делителя ЗУ, 5У, 7У,..., (2 -l)Y).

При зтом цикл деления описывается следующим алгоритмом.

На основе анализа (Р+2)-х старших разрядов остатка делителя и знака остатка определяется Р-разрядное частичное частное Z; (i - номер цикла).

Определяется остаток

x;

X;-2 - Z;Y, если X;b 0,

X--2 + (2 - Z;)Y, если X,

Корректируются значения частичного частного

Z;

,; , если X; i О,

Z; - 2, если X; 0. .

(4)

5

Q

0

5

Для получения п-разрядного частного цикл деления повторяем п/Р раз.

Устройство работает следующим образом.В исходном положении устройства в сумматоре I и регистре 3 делителя находится значение делителя Y, в регистре 2 делимого - значение делимого X.

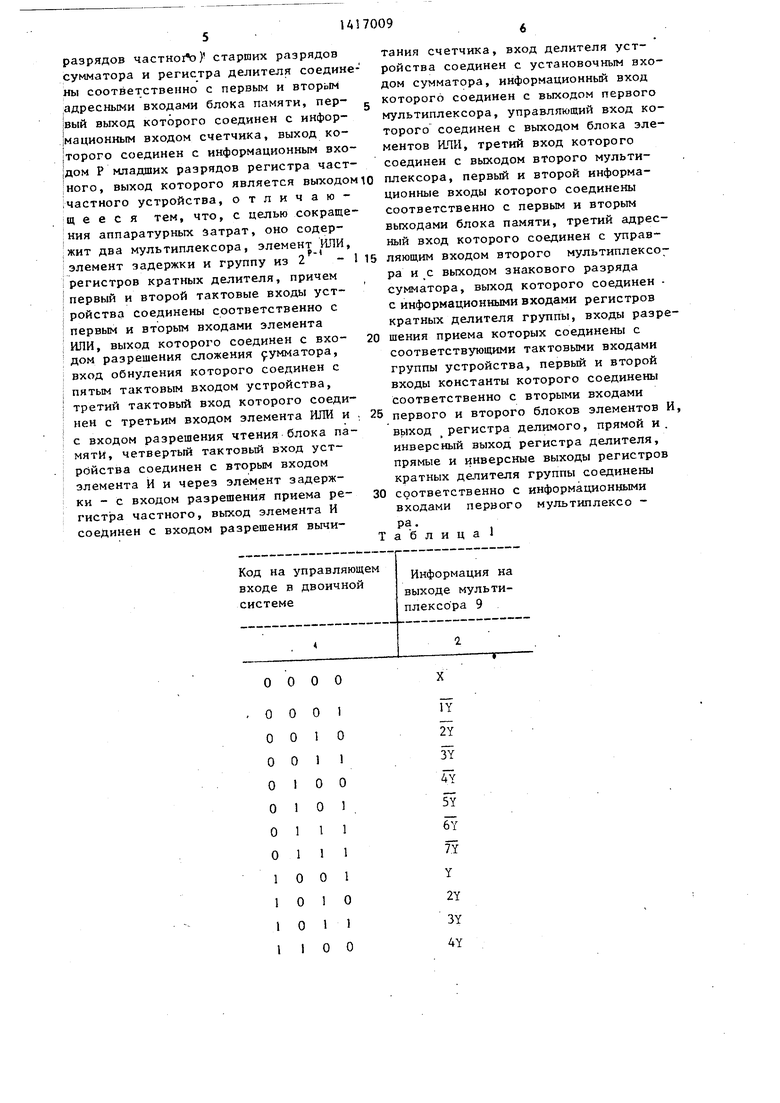

В зависимости от кода, поступающего на управляющий вход первого муль-i типлексора У, выбор информационного входа с передачей сигналов на выход производится согласцр табл. 1 соответствия (см. пример для Р 3 в табл. 1 ) , где KY (К 1 ,2, . .. ,) - инвертированное значение KY, включая знаковый разряд.

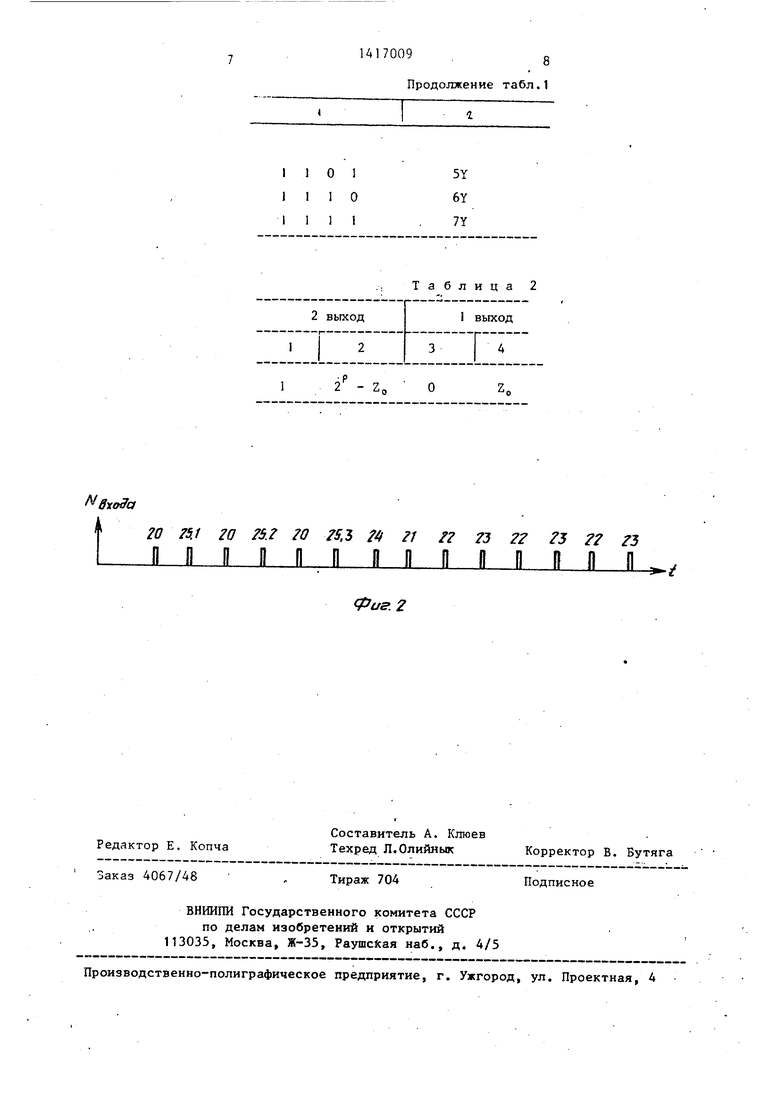

В ( )-разрядных ячейках блока 11 памяти по адресам X , (Х - -Yjj)Yjj хранится предварительно сформированная информация в виде, показанном в табл.. 2. I .

Во второй и четвертой графах табл. 2 соответственно расположен Р-разрядный код частичного частного

Z и разности (2 -Z), а в первой и третьей графах - признак. На входах 18 и 19 устройства установлены соответственно константы 1010 и 0000 для (Р 3).

Подготовка устройства к выполнению деления происходит следующим образом.

По сигналу с входа 20 значение с входа 18 через блок 5 элементов И и блок 13 элементов ИЛИ поступает на управляющий вход мультиплексора 9 (фиг. 2). По указанному значению (см табл. I) кратное двум делителя 2У с регистра 3 делителя поступает на информационный вход сумматора 1. По этому же сигналу производится сложение содержимого сумматора 1 с кратным делителем 2У,

По сигналу с входа 25.1, поступающему на управляющий вход первого регистра 15 кратных делителя, содержимое сумматора; I, равное 3Y, заносится на данный регистр.

Аналогично по сигналам с входов 20, 25.2 и 20, 25.3 на втором и третем регистрах 15 кратньк делителя формируется соответственно значения 5Y и 7Y. Далее согласно временной диаграмме (фиг. 2) возникает сигнал на входе 24, по которому производится онуление сумматора J. По сигналу с входа 21 значение с входа 19 проходит через блок 14 элементов И и блок 13 элементов ИЛИ на управляющий вход мультиплексора 9.По нему (см. табл. I) содержимое регистра 2 делимого через мультиплексор 9 поступает на информационный вход сумматора 1 и заносится в него.

Деление производится следующим образом.

Для определения п цифр частного выполняется п/Р одинаковых циклов деления . В первом такте каждого цикла . .(по сигналу с входа 22) производится сдвиг влево на Р разрядов содержимого регистра 4.частного, считывание из блока 11 памяти частичного частр

ного Z- и разности 2 - Z с соответствующими признаками в соответствии с адресом, состоящим из (Р+2)-х старших разрядов остатка (содержимое сумматора 1), знакового разряда,остатка, ()-х старших разрядов делителя (регистр делителя 3), занесение на счетчик 8 с выхода блока 11 памяти частичного частного Zg , а

также формирование кода на управляющем входе первого мультиплексора 9, поступающего в зависимости от значения сигнала на управляющем входе второго мультиплексора 10 с одного из входов блока I 1 в виде кода, состоящего из значения Z с признаком О или в виде кода, состоящего из разности 2 - Z с признаком J, через цепи второго мультиплек- . сора 10 и блок 13 элементов ИЛИ. В соответствии с кодом на управляющем входе первого мультиплексора 9 на

информационный вход сумматора 1 в соответствии с табл. f подается соответствующий код кратного делителя KY или KY.

Кроме того, производится сложение

содержимого сумматора 1 с соответствующим кодом кратного делителя (формируется очередной остаток Х).

Во втором такте каждого цикла (по сигналу с входа 23) производится

ссдвиг влево мантиссы остатка на сумматоре 1 , коррекция частичного частного ZP на счетчике 8 по правилу:

2 о если остаток Х О, о J .

( ZQ , если остаток ,

а также запись скорректированного частичного ч-астного младшие разряды 27 регистра 4 частного.

35

Формула изобретения

Устройство для деления чисел с фиксированной запятой, содержащее сумматор, регистры делимого, делителя и

40 частного, два блока элементов И, элемент И, счетчик, блок памяти и блок элементов ИЛИ, причем входы делимого и дели теля устройства соединены соответственно с входами регистров дели45 мого и делителя, первый и второй тактовые входы устройства соединены .соответственно с первыми входами первого и второго блоков элементов И, выходы которых соединены соответственно с

50 первым и вторым входами блока элементов ИЛИ, третий тактовый вход устройства соединен с входом разрешения сдвига регистра частного и с входом разрешения записи счетчика, четвертый такgg товый вход устройства соединен с входом разрешения сдвига сумматора, выход знакового разряда которого соединен с первым входом элемента И, выходы (Р+2)-х (р - количество фopмиpye fыx

разрядов частноЛэ}- старших разрядов сумматора и регистра делителя соединены соответственно с первым и вторым .адресными входами блока памяти, пер- , JBbtft выход которого соединен с инфор- мационным входом счетчика, выход ко- {Торого соединен с информационным вхо- 1дом Р младших разрядов регистра часттания счетчика, вход делителя устройства соединен с установочным входом сумматора, информационный вход которого соединен с выходом первого мультиплексора, управляющий вход которого соединен с выходом блока элементов ИЛИ, третий вход которого соединен с выходом второго мульти

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления последовательных чисел | 1987 |

|

SU1462298A1 |

| Устройство для деления | 1984 |

|

SU1242935A1 |

| Устройство для деления | 1984 |

|

SU1259251A1 |

| Устройство для деления чисел | 1985 |

|

SU1287149A1 |

| Устройство для деления десятичных чисел | 1990 |

|

SU1774328A1 |

| Устройство для деления чисел | 1987 |

|

SU1465883A1 |

| Устройство для деления | 1990 |

|

SU1783522A1 |

| Устройство управления микропроцессором | 1983 |

|

SU1156072A1 |

| Устройство для деления двоичных чисел | 1985 |

|

SU1325466A1 |

| Устройство для деления | 1979 |

|

SU773618A1 |

Изобретение относится к вычислительной технике и может быть использовано, в частности, при создании, специализированных систем переработки информации. Цель изобретения - сокращение аппаратурных затрат. Поставленная цель достигается тем, что в устройство для деления чисел с фиксированной запятой, содержащее сумматор 1, регистр 2 делимого, регистр 3 делителя, регистр 4 частного, блоки 5, 14 элементо з И, элемент И 7, счетчик 8, блок II памяти и блок 3 элементов И, введены элемент ИЛИ 6, мультиплексоры 9, 10, элемент 12 задержки и группа регистров I5 кратных делителя с соответствующими связями. 2 ил., 2 табл.

jHoro, выход которого является выходомю плексора, первый и второй информаэлемент ИЛИ, .-«

гчастного устройства, отличающееся тем, что, с целью сокраще Iния аппаратурных затрат, оно содер- жит два мультиплексора, элемент задержки и группу из 2 i регистров кратных делителя, причем первый и второй тактовые входы устройства соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соединен с входом разрешения сложения умматора, вход обнуления которого соединен с пятьм тактовым входом устройства, третий тактовый вход которого соединен с третьим входом элемента ИЛИ и с входом разрешения чтения блока памяти, четвертый тактовый вход устройства соединен с вторым входом злемента И и через элемент задержки - с входом разрешения приема регистра частного, выход элемента И соединен с входом разрешения вьми

0000

ционные входы которого соединены соответственно с первым и вторым выходами блока памяти, третий адресный вход которого соединен с управ15 ляющим входом второго мультиплексора и с выходом знакового разряда сумматора, выход которого соединен - с информационными входами регистров кратных делителя группы, входы разре- 20 шения приема которых соединены с соответствующими тактовыми входами группы устройства, первый и второй входы константы которого соединены соответственно с вторыми входами

25 первого и второго блоков элементов И, выход регистра делимого, прямой и, инверсный выход регистра делителя, прямые и инверсные выходы регистров кратных депителя группы соединены 30 соответственно с информационными входами первого мультиплексо - ра. Таблица 1

1Y

2Y

3Y

4Y

5Y

6Y

71

Y

2Y

3Y

4Y

1101 1110 1111

20 75.1 2Q 25.2 20 ДЗ 2 21 2 3 22 /5 22 /5

О Л i Л П П fl О О ( О О И П

Редактор Е. Копча

Составитель А. Клюев Техред Л.Олийнык

Заказ 4067/48

Тираж 704

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушс«сая наб., д. 4/5

Продолжение табл.1

5Y 6Y

7Y

Таблица 2

i

Фие.2

Корректор В. Бутяга

Подписное

| Делительное устройство | 1982 |

|

SU1104508A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Устройство для деления | 1985 |

|

SU1283752A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-08-15—Публикация

1986-12-12—Подача