-11

Изобретение относится к вычислительной технике и может быть использовано при разработке цифровых вычислительных машин последовательного действия.

Целью изобретения является повышение быстродействия устройства.

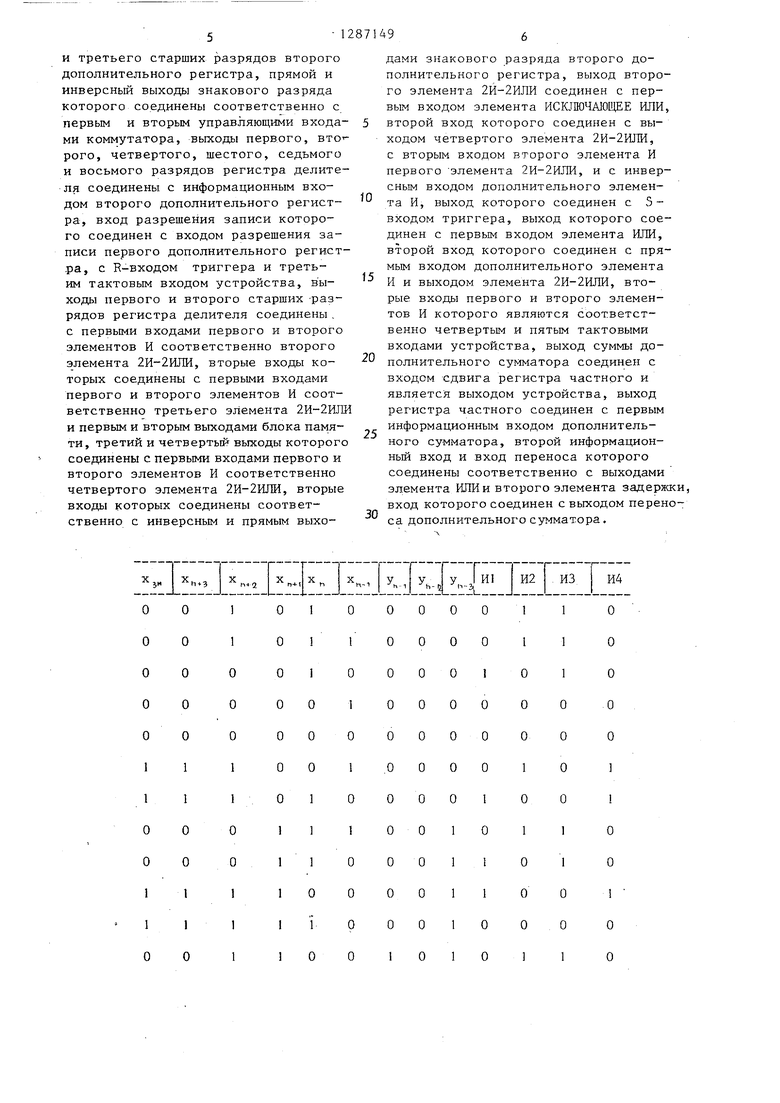

На фиг. 1 приведена функциональная схема предлагаемого устройства; на фиг. 2 - временная диаграмма вы- работки тактовых сигналов устройства.

Устройство для деления чисел содержит регистр 1 делимого, первый элемент И 2, первый тактовый вход 3, сумматор 4, регистр 5 делителя, первый дополнительный регистр 6, третий тактовый вход 7, второй дополнительный триггер 8, коммутатор 9, блок 10 памяти, второй и четвертый элементы 2И-2ИЛИ 11 и 12,элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 13, первьш элемент 14 задержки, первый элемент 2И-2ИЛИ 15, второй тактовый вход 16, третий элемент 2И-2ИЛИ 17, элемент ИЛИ 18, второй элемент И 1.9, триггер 20, дополнительный сумматор 21, регистр 22 частного, второй элемент 23 задержки, четвертый и пятый тактовые входы 24 и 25, выход 26.

Цикл работы устройства составляет ;п+5 тактов, где I, 2,...,п такты предназначены для обработки 1-го (младшего) 2-го,...,п-го дробных разрядов операндов, (п+1)-й, (п+2)-й и (п+3)-й такты предназначены для обработки целых разрядов операндов (очередной остаток после сдвига на два разряда в сторону старших разрядов может иметь 3 целых разряда), (п+4)-- такт для представления знака и (п+5)-й такт - служебньш, для управления схемой. Регистр 1, предназначенный для хранения делимого X и очередного остатка 0 , содержит п +7 разрядов. В каждом цикле в нем производится сдвиг операнда на 2 разряда в сторону старших разрядов. Делитель Ч хранится в регистре 5, имеющем п+5 разрядов. Единичные выходы первого второго - шестого триггеров регистра 1 (считая слева) соединены с входами шестиразрядного параллельного регистра 6, построенного на D- триггерах. Управление записью в ре- гистр 6 производится сигналом С 5, поступающим с входа 7. В начале служебного такта шесть старших разрядов X или Q переписываются в регистр 6

492

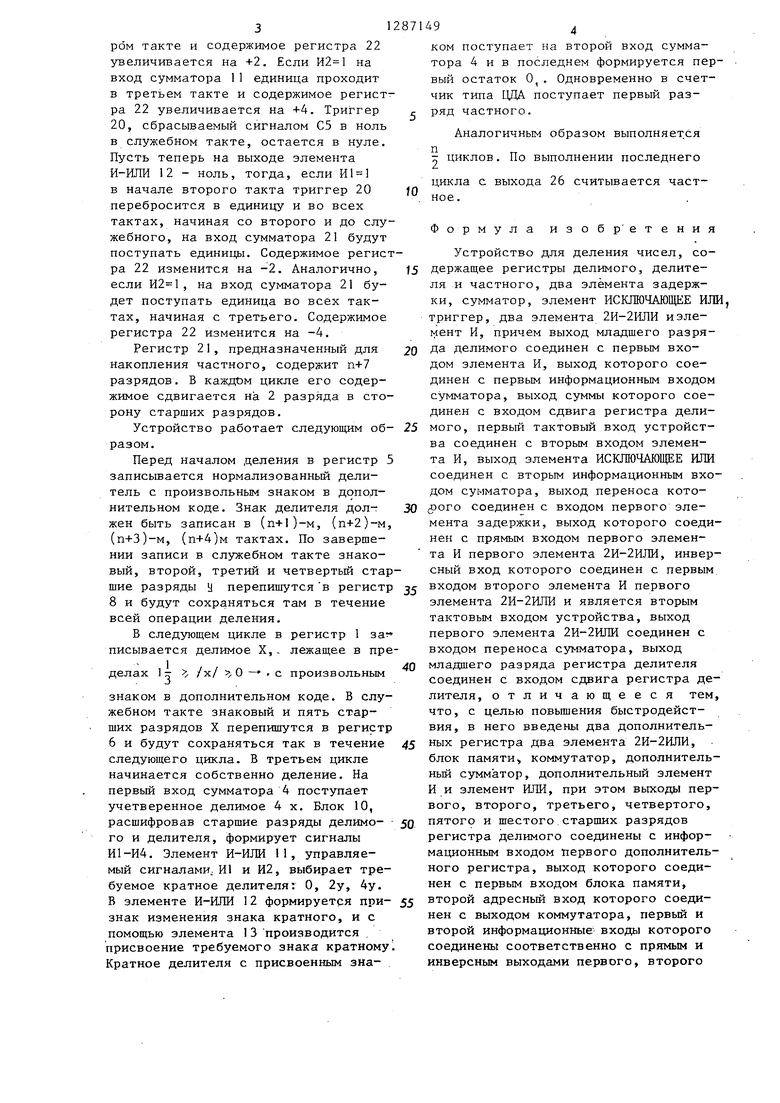

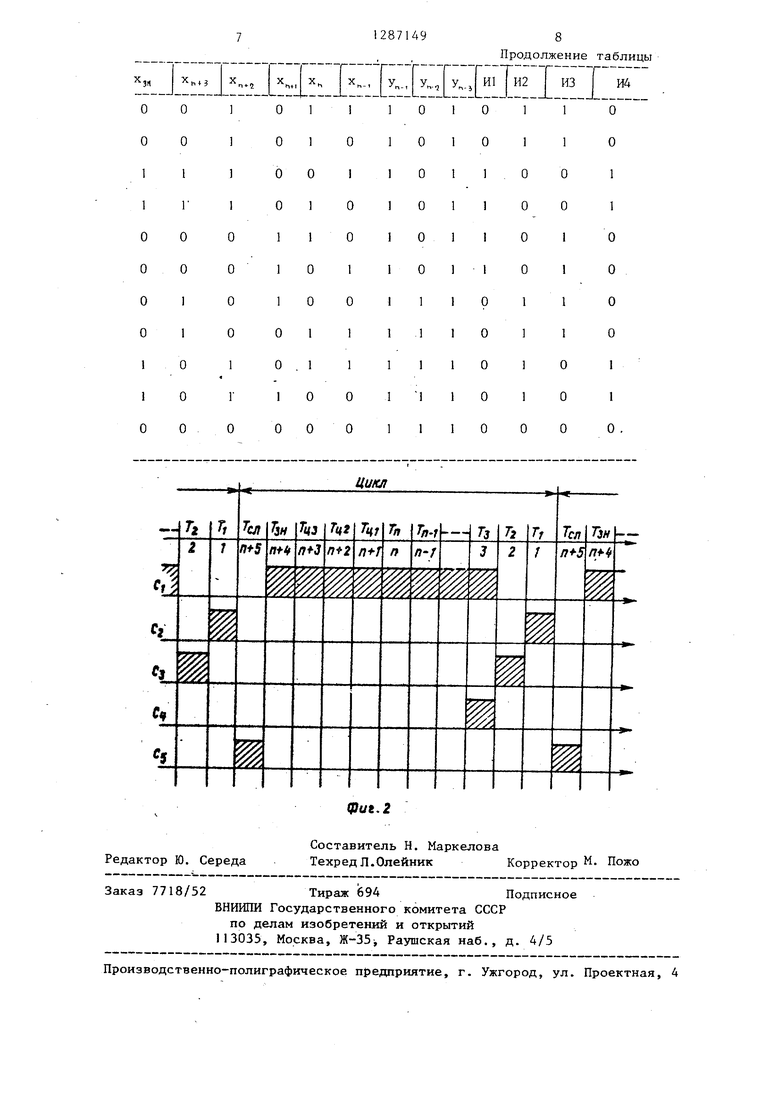

и хранятся в нем весь цикл. Единичные выходы четвертого, шестого, седьмого и восьмого триггеров регистра 5 соединены с входами параллельного четырехразрядного регистра 8 аналогично регистру 6. Управление записью в регистр 8 также производится сигналом С 5,. потому в регистр 8 в служебном такте записывается знак и второй, третий, четвертый старшие разряды делителя (делитель полагается нормализованным, поэтому первый старший разряд У не нужен). Прямой и инверсный выходы знакового разряда () регистра 8 подключены к управляющим входам коммутатора 9, который состоит из 3-х элементов И-ИЛИ. Если Т О, второй, третий и четвертый разряды У проходят через коммутатор, не меняясь. Если.Т, 1 - они инвертируются. Блок 10 имеет 4 выхода: И1, И2, ИЗ и И4. Прошивка блока 10 произведена в соответствии с данными, приведенными в табдице. Ввиду громоз д- кости таблица приведена с пропусками. В таблице выходы регистра 6 обозначены X

5 tn-ij - ni-n t

Выходы регистра В обозначены У„,, У.,) у , Выходы блока 10 И1 и И2 управ- ляют входами 1 и 2 элемента И-ИЛИ 11 Выходы ИЗ и И4 блока 10 соединены с первьм и вторым входами элемента И-ИЛИ 12. Элемент И-ИЛИ 12 формирует знак, который необходимо присвоить делителю. Присвоение знака производится с помощью элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13. Если на выходе элемента i . И-ИЛИ 12 - ноль, кратное делителю проходит через элемент 12 не меняясь если - единица, кратное делителю инвертируется. Перенос, формируемый в сумматоре 4, задерживается на один такт в элементе 14 задержки. Элемент И-ИЛИ 15 служит для гашения переноса в младший разряд и коррекции инверсии кратного делителю в дополнение при присвоении ему знака минус. Элементы И-ИЛИ 17, ИЛИ 18 и И 19, триггер 20, сумматор 21, регистр 22 и элемент 23 задержки представляет собой счетчик типа ЦДА. На вкоды элементы И-ИЛИ 17 с входов устройства 24 и 25 поступают сигналы СЗ и С4. Сигнал СЗ 1 во втором такте, сигнал С4 1 в третьем такте. Пусть на выходе элемента И-ИПИ 12 - единица, тогда, если через элементы И-ИЛИ 17 и ИЛИ 18 на вход сумматора 21 единица проходит во вто31

ром такте и содержимое регистра 22 увеличивается на +2. Если на вход сумматора 11 единица проходит в третьем такте и содержимое регистра 22 увеличивается на +4. Триггер 20, сбрасываемый сигналом С5 в ноль в служебном такте, остается в нуле. Пусть теперь на выходе элемента И-ИЛИ 12 - ноль, тогда, если И1 в начале второго такта триггер 20 перебросится в единицу и во всех тактах, начиная со второго и до служебного, на вход сумматора 21 будут поступать единицы. Содержимое регистра 22 изменится на -2. Аналогично, если , на вход сумматора 21 будет поступать единица во всех тактах, начиная с третьего. Содержимое регистра 22 изменится на -4.

Регистр 21, предназначенный для накопления частного, содержит п+7 разрядов. В кажд1эм цикле его содержимое сдвигается на 2 разряда в сторону старших разрядов.

Устройство работает следующим об- разом.

Перед началом деления в регистр 5 записьшается нормализованный делитель с произвольным знаком в дополнительном коде. Знак делителя дол- жен быть записан в (п+1)-м, (п+2)-м, (п+3)-м, (п+4)м тактах. По завершении записи в служебном такте знаковый, второй, третий и четвертый старшие разряды у перепишутся в регистр 8 и будут сохраняться там в течение всей операции деления.

В следующем цикле в регистр 1 за писывается делимое X,. лежащее в пределах 1 :г , /X/ . О - г с произвольным

знаком в дополнительном коде. В служебном такте знаковый и пять старших разрядов X перепишутся в регистр 6 и будут сохраняться так в течение следующего цикла. В третьем цикле начинается собственно деление. На первый вход сумматора 4 поступает учетверенное делимое 4 х. Блок 10, расшифровав старшие разряды делимо- го и делителя, формирует сигналы И1-И4. Элемент И-ИЛИ 11, управляемый сигналами И1 и И2, выбирает требуемое кратное делителя: О, 2у, 4у. В элементе И-ИЛИ 12 формируется при- знак изменения знака кратного, и с помощью элемента 13 производится присвоение требуемого знака кратному Кратное делителя с присвоенным зна494

ком поступает на второй вход сумматора 4 и в последнем формируется первый остаток 0. Одновременно в счетчик типа ЦДА поступает первый разряд частного.

Аналогичным образом выполняет.ся г циклов. По выполнении последнего

цикла с выхода 26 считывается частное.

Формула изобр етения

Устройство для деления чисел, содержащее регистры делимого, делителя и частного, два элемента задержки, сумматор, элемент ИСКЛЮЧАЮЩЕЕ ИЛ триггер, два элемента 2И-21 ЛИ и элемент И, причем выход младшего разряда делимого соединен с первьм входом элемента И, выход которого соединен с первым информационным входом сумматора, выход суммы которого соединен с входом сдвига регистра делимого, первый тактовый вход устройства соединен с вторым входом элемента И, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с вторым информационным входом сумматора, выход переноса кото- (рого соединен с входом первого элемента задержки, выход которого соединен с прямым входом первого элемента И первого элемента 2И-2ИЛИ, инверсный вход которого соединен с первым входом второго элемента И первого элемента 2И-2ИЛИ и является вторым тактовым входом устройства, выход первого элемента 2И-2ИЛИ соединен с входом переноса сумматора, выход младшего разряда регистра делителя соединен с входом сдвига регистра делителя, отличающееся тем что, с целью повышения быстродействия, в него введены два дополнительных регистра два элемента 2И-2ИЛИ, блок памяти, коммутатор, дополнительный сумматор, дополнительный элемент И и элемент ИЛИ, при этом выходы первого, второго, третьего, четвертого, пятого и шестого старших разрядов регистра делимого соединены с информационным входом tiepBoro дополнительного регистра, выход которого соединен с первым входом блока памяти, второй адресный вход которого соединен с выходом коммутатора, первый и второй информационные входы которого соединены соответственно с прямым и инверсным выходами первого, второго

и третьего старших разрядов второго дополнительного регистра, прямой и инверсный выходы знакового разряда которого соединены соответственно с первым и вторым управляющими входа ми коммутатора, выходы первого, вто рого, четвертого, шестого, седьмого и восьмого разрядов регистра делителя соединены с информационным входом второго дополнительного регистра, вход разрешения записи которого соединен с входом разрешения записи первого дополнительного регистра, с R-входом триггера и третьим тактовым входом устройства, в ы- ходы первого и второго старших -разрядов регистра делителя соединены . с первыми входами первого и второго элементов И соответственно второго элемента , вторые входы которых соединены с первыми входами первого и второго элементов И соответственно третьего элемента 2И-2ИЛИ и первым и вторым выходами блока памяти, третий и четвертый выходы которого соединены с первыми входами первого и второго элементов И соответственно четвертого элемента 2И-2ИЛИ, вторые входы которых соединены соответственно с инверсным и прямым выхо-

дами знакового разряда второго дополнительного регистра, выход второго элемента 2Й-2ИЛИ соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом четвертого элемента 2И-2ИЛИ, с вторым входом второго элемента И первого элемента 2И-2ИЛИ, и с инверсным входом дополнительного элемента И, выход которого соединен с S- входом триггера, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с прямым входом дополнительного элемента И и выходом элемента 2И-2ИЛИ, вторые входы первого и второго элементов И которого являются соответственно четвертььм и пятым тактовыми входами устройства, выход суммы дополнительного сумматора соединен с входом сдвига регистра частного и является выходом устройства, выход, регистра частного соединен с первым информационным входом дополнительного сумматора, второй информационный вход и вход переноса которого соединены соответственно с выходами элемента ИЛИ и второго элемента задержки, вход которого соединен с выходом переноса дополнительного сумматора.

TCJI

Тзн

Тцз

Тцг

ni-S

ni-tf

iH-3

ni-2

rj

L fj.

1

5

Редактор Ю. Середа

ф(/е.2

Составитель Н. Маркелова Техр е д Л. Олейник

Заказ 7718/52Тираж 694Подписное

ВНИШШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35 Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Продолжение таблицы

Tn-i

7 Tt

Тел

nt-J

n-r

n-f-5 n

Корректор W Пожо

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления двоичных чисел | 1985 |

|

SU1325466A1 |

| Устройство для деления последовательных чисел | 1987 |

|

SU1462298A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Устройство для умножения @ -разрядных чисел | 1984 |

|

SU1256018A1 |

| Устройство для деления десятичных чисел | 1989 |

|

SU1688239A1 |

| Устройство для деления десятичных чисел | 1990 |

|

SU1774328A1 |

| Устройство для деления чисел | 1987 |

|

SU1465883A1 |

| Устройство для деления нормализованных чисел | 1985 |

|

SU1290302A1 |

| Устройство для деления десятичных чисел | 1984 |

|

SU1241235A1 |

| Устройство для деления чисел | 1981 |

|

SU1056183A1 |

Изобретение относится к области вычислительной техники и может ис- лользоваться при построении специализированных и универсальных ЦВМ. Для повышения быстродействия устройства в него введены два регистра 6 и 8, блок 10 памяти, два элемента И-РШИ 15, 17, сумматор 4, коммутатор 9, элемент И 19, элемент ИЛИ 18. 2 ил., 1 табл. Зо (Л 1C 00 4i СО

Авторы

Даты

1987-01-30—Публикация

1985-06-17—Подача