Изобретение относится к вычислительной технике и может быть использовано при разработке цифровых вычислительных машин.

Цель изобретения - расширение функциональных возможностей устройства за счет выполнения операции деления для чисел с произвольными знаками и уменьшение аппаратных затрат.

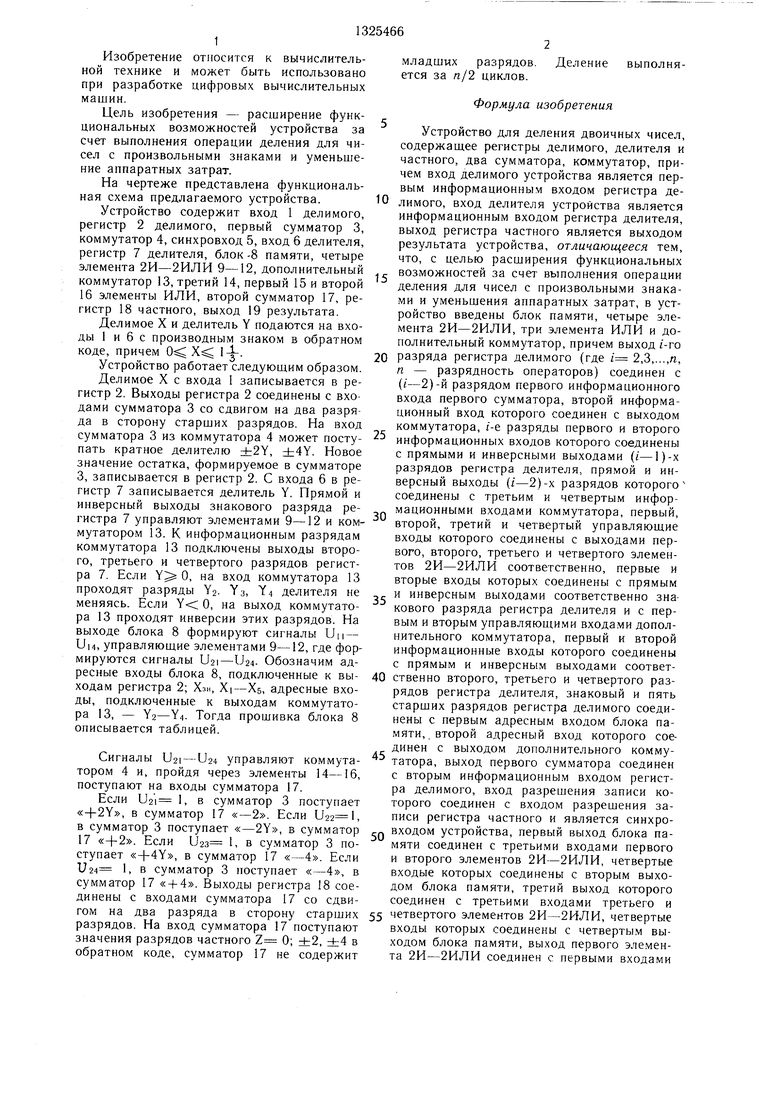

На чертеже представлена функциональная схема предлагаемого устройства.

Устройство содержит вход 1 делимого, регистр 2 делимого, первый сумматор 3, коммутатор 4, синхровход 5, вход 6 делителя, регистр 7 делителя, блок -8 памяти, четыре элемента 2И-2ИЛИ 9-12, дополнительный коммутатор 13, третий 14, первый 15 и второй 16 элементы ИЛИ, второй сумматор 17, регистр 18 частного, выход 19 результата.

Делимое X и делитель Y подаются на входы 1 и 6 с производным знаком в обратном коде, причем 0 Х 1-|-.

Устройство работает следующим образом.

Делимое X с входа 1 записывается в регистр 2. Выходы регистра 2 соединены с входами сумматора 3 со сдвигом на два разряда в сторону старших разрядов. На вход

младших разрядов. ется за л/2 циклов.

Деление выполня10

Формула изобретения

Устройство для деления двоичных чисел, содержащее регистры делимого, делителя и частного, два сумматора, коммутатор, причем вход делимого устройства является первым информационным входом регистра делимого, вход делителя устройства является информационным входом регистра делителя, выход регистра частного является выходом результата устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет выполнения операции деления для чисел с произвольными знаками и уменьшения аппаратных затрат, в устройство введены блок памяти, четыре элемента 2И-2ИЛИ, три элемента ИЛИ и дополнительный коммутатор, причем выход г -го 20 разряда регистра делимого (где / 2,3,...,/г, п - разрядность операторов) соединен с (( -2)-и разрядом первого информационного входа первого сумматора, второй информационный вход которого соединен с выходом коммутатора, г -е разряды первого и второго

15

сумматора 3 из коммутатора 4 может посту- 25 информационных входов которого соединены

пать кратное делителю ±2Y, ±4Y. Новое значение остатка, формируемое в сумматоре 3, записывается в регистр 2. С входа 6 в регистр 7 записывается делитель У. Прямой и инверсный выходы знакового разряда регистра 7 управляют элементами 9-12 и коммутатором 13. К информационным разрядам коммутатора 13 подключены выходы второго, третьего и четвертого разрядов регистра 7. Если У О, на вход коммутатора 13

30

с прямыми и инверсными выходами (г-)-х разрядов регистра делителя, прямой и инверсный выходы (/-2)-х разрядов которого соединены с третьим и четвертым информационными входами коммутатора, первый, второй, третий и четвертый управляющие входы которого соединены с выходами первого, второго, третьего и четвертого элементов 2И-2ИЛИ соответственно, первые и вторые входы которых соединены с прямым

проходят разряды У2. Уз, Y.I делителя неи инверсным выходами соответственно знаменяясь. Если О, на выход коммутато-кового разряда регистра делителя и с перра 13 проходят инверсии этих разрядов. Навым и вторым управляющими входами дополвыходе блока 8 формируют сигналы Un-нительного коммутатора, первый и второй

Uu, управляющие элементами 9-12, где фор-информационные входы которого соединены

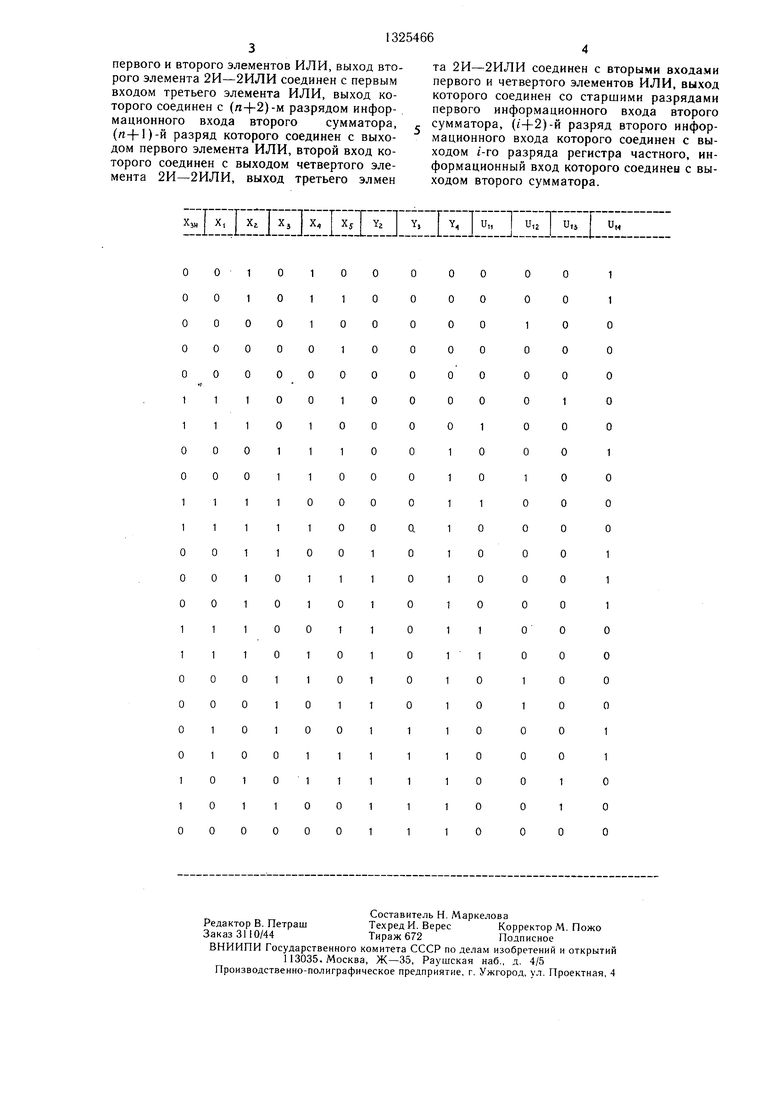

мируются сигналы U2i-ih. Обозначим ад-с прямым и инверсным выходами соответ- ресные входы блока 8, подключенные к вы- 40 ственно второго, третьего и четвертого разходам регистра 2; Хзн, Xi-ХБ, адресные входы, подключенные к выходам коммутатора 13, - У2-У4. Тогда прошивка блока 8 описывается таблицей.

рядов регистра делителя, знаковый и пять старших разрядов регистра делимого соединены с первым адресным входом блока памяти,, второй адресный вход которого соединен с выходом дополнительного коммутатора, выход первого сумматора соединен с вторым информационным входом регистра делимого, вход разрешения записи которого соединен с входом разрешения записи регистра частного и является синхрорядов регистра делителя, знаковый и пять старших разрядов регистра делимого соединены с первым адресным входом блока памяти,, второй адресный вход которого соединен с выходом дополнительного коммутатора, выход первого сумматора соединен с вторым информационным входом регистра делимого, вход разрешения записи которого соединен с входом разрешения записи регистра частного и является синхроСигналы U21 - U24 управляют коммута- тором 4 и, пройдя через элементы 14-16, поступают на входы сумматора 17.

Если U2 i 1, в сумматор 3 поступает «-f2y, в сумматор 17 «-2. Если ,

в сумматор 3 поступает «-2У, в сумматорj- входом устройства, первый выход блока па17 «-(-2. Если U23 1, в су.мматор 3 по-мяти соединен с третьими входами первого

ступает «+4У, в сумматор 17 «-4. Еслии второго элементов 2И-2ИЛИ, четвертые

и24 1, в сумматор 3 поступает «-4, ввходые которых соединены с вторым выходом блока памяти, третий выход которого соединен с третьими входами третьего и

гом на два разряда в сторону старших55 четвертого элементов 2И-2ИЛИ, четвертые

разрядов. На вход сумматора 17 поступаютвходы которых соединены с четвертым вызначения разрядов частного Z 0; ±2, ±4 входом блока памяти, выход первого эле.менобратном коде, сумматор 17 не содержитта 2И-2ИЛИ соединен с первыми входами

сумматор 17 « + 4. Выходы регистра 18 соединены с входами сумматора 17 со сдвимладших разрядов. ется за л/2 циклов.

Деление выполня0

Формула изобретения

Устройство для деления двоичных чисел, содержащее регистры делимого, делителя и частного, два сумматора, коммутатор, причем вход делимого устройства является первым информационным входом регистра делимого, вход делителя устройства является информационным входом регистра делителя, выход регистра частного является выходом результата устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет выполнения операции деления для чисел с произвольными знаками и уменьшения аппаратных затрат, в устройство введены блок памяти, четыре элемента 2И-2ИЛИ, три элемента ИЛИ и дополнительный коммутатор, причем выход г -го 0 разряда регистра делимого (где / 2,3,...,/г, п - разрядность операторов) соединен с (( -2)-и разрядом первого информационного входа первого сумматора, второй информационный вход которого соединен с выходом коммутатора, г -е разряды первого и второго

5

5 информационных входов которого соединены

информационных входов которого соединены

с прямыми и инверсными выходами (г-)-х разрядов регистра делителя, прямой и инверсный выходы (/-2)-х разрядов которого соединены с третьим и четвертым информационными входами коммутатора, первый, второй, третий и четвертый управляющие входы которого соединены с выходами первого, второго, третьего и четвертого элементов 2И-2ИЛИ соответственно, первые и вторые входы которых соединены с прямым

и инверсным выходами соответственно знарядов регистра делителя, знаковый и пять старших разрядов регистра делимого соединены с первым адресным входом блока памяти,, второй адресный вход которого соединен с выходом дополнительного коммутатора, выход первого сумматора соединен с вторым информационным входом регистра делимого, вход разрешения записи которого соединен с входом разрешения записи регистра частного и является синхропервого и второго элементов ИЛИ, выход второго элемента 2И-2ИЛИ соединен с первым входом третьего элемента ИЛИ, выход которого соединен с (л+2)-м разрядом информационного входа второго сумматора, (л+1)-й разряд которого соединен с выходом первого элемента ИЛИ, второй вход которого соединен с выходом четвертого элемента 2И-2ИЛИ, выход третьего элмен

та 2И-2ИЛИ соединен с вторыми входами первого и четвертого элементов ИЛИ, выход которого соединен со старшими разрядами первого информационного входа второго сумматора, (г-|-2)-й разряд второго информационного входа которого соединен с выходом i-ro разряда регистра частного, информационный вход которого соединен с выходом второго сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел | 1985 |

|

SU1287149A1 |

| Устройство для деления чисел | 1981 |

|

SU1056183A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

| Устройство для деления чисел без восстановления остатка | 1989 |

|

SU1605228A1 |

| Устройство для деления | 1990 |

|

SU1803913A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Устройство для деления | 1985 |

|

SU1283752A1 |

| Устройство для деления | 1990 |

|

SU1709352A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018933C1 |

| Устройство для деления нормализованных чисел | 1985 |

|

SU1290302A1 |

Изобретение относится к вычислительной технике и может быть использовано при разработке цифровых вычислительных машин. Целью изобретения являются расширение функциональных возможностей устройства за счет выполнения операции деления для чисел с произвольными знаками и уменьшение аппаратных затрат. В устройство, содержащее регистры делимого 2, делителя 7 и частного 18, сумматоры 3, 17 и коммутатор 4, введены блок 8 памяти, элементы 2И- 2ИЛИ 9-12, элементы ИЛИ 14-16 и дополнительный коммутатор 13. Деление выполняется для делимого X и делителя Y с произвольными знаками в обратном коде, причем 1, 1. Текуш,ий разряд частного может принимать значения 0; ±2; ±4. 1 ил. 00 tN3 сл 4 О) а

| Устройство для деления чисел | 1981 |

|

SU1119006A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления двоичных чисел | 1981 |

|

SU1008733A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-23—Публикация

1985-06-12—Подача