Изобретение относится к импульсно технике и может быть использовано в гдифровых интегралькьк схемах, к которым предъявляются требования установки триггеров и триггерньгх устройств Б определенное исходное состояние в процессе нарастания напря- же ния питания.

Цель изобретения - снижение потг ребляемой триггером мощности в статическом -режиме и повьшгегше надежности его установки в определенное исходно состояние в процессе нарастания напряжения питания.

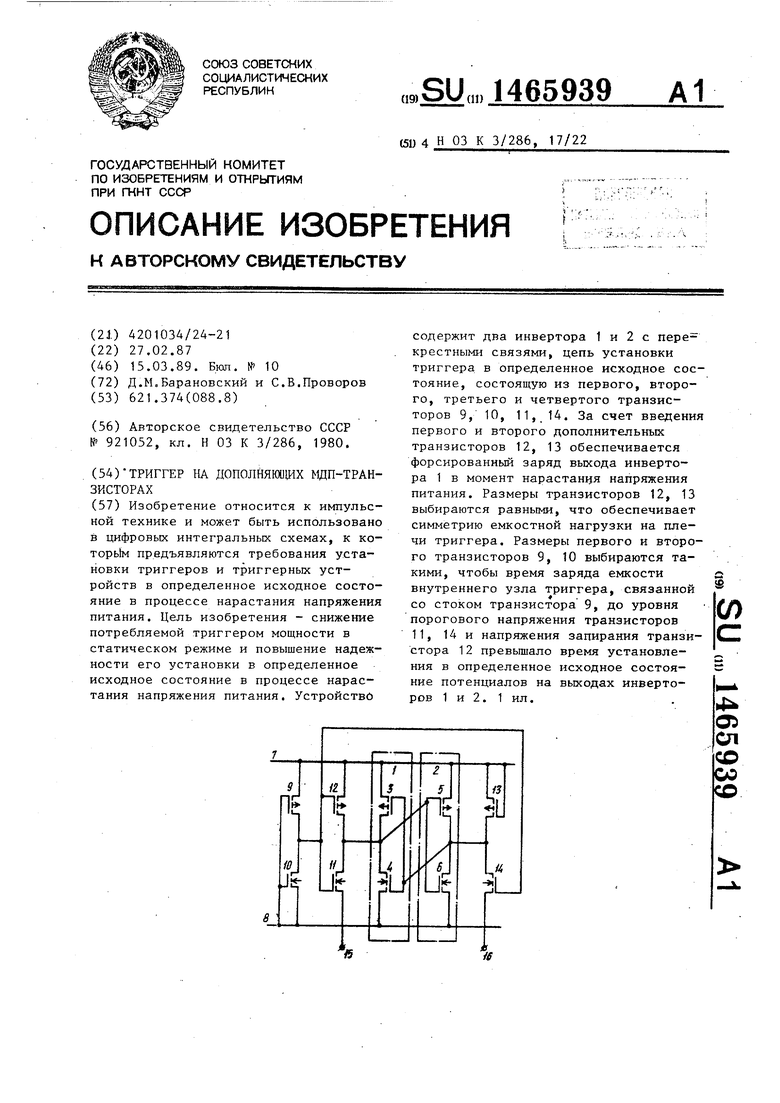

На чертеже представлена электрическая принципиальная схема описываемого триггера.

Триггер состоит из инверТ оров 1 и 2 с перекрестными связями, каждый из которых содержит два .комплемет - тарных транзистора 3, 4 и 5,6 соответственно, последовательно включенных между тиной 7 питания и общей шиной 8, первого тралзистора 9 первого типа проводимости, исток кототорого подключен к тине 7, затвор - к шине 8, сток - к стоку и затвору соответственно п торого 10-и третьего 11 транзисторов второго типа проводимое ти, истоки которых подключены к шине 8 и выходу инвертора 1 соответственно. - Истоки двух дополнительно введенных транзисторов 12 и 13 перво го типа проводимости подключены к аш ; не 7. При этом сток транзистора 12 подключен к выходу инвертора 1, а ег затвор - к затвору четвертого транзистора 14 и стоку транзистора 10,

затвор которого подключен к истоку

и шине 8, затвор транзистора 13 подключен к шине 7, сток - к выходу инвертора 2 и истоку транзистора 14. Прямым 15 и инверсным 16 выходами триггера являются стоки транзисторов 11 и 14 соответственно.

Триггер на дополнительных МДП- транзисторах работает следующим образом,

В процессе нарастания, напряжения питания вначале открываются транзисторы 3, 5р 9, 12, что приводит к постоянному заряду внутренних узлов триггера. Размеры транзисторов 3, 4, 11 и 12 выбираются равными размерам транзисторов 5, 6, 14 и 13 соответственно, что обеспечивает симметрию емкостной нагрузки на плечи триггера при этом суммарная ширина канала

je

20 25 30 эс

дд

дг

50

5

транзисторов 3 и 12 больше ширины канала транзистора 5, что приводит в процессе нарастания напряжения питания к более быстрому заряду выхода . первого инвертора по сравнению с выходом второго инвертора. Размеры,/ транзисторов 9 и 10 выбираются такими, чтобы время заряда емкости внутреннего узла триггера, связанной со стоком транзистора 9, до уровня порогового напряжения транзисторов 11,

14и напряжения запирания транзистора 12 превышало как время установления в определенное исходное состояние потенциалов на выходах инверторов 1

и 2 с перекрестными связями, так и время переходньгх процессов во внешних устройствах, подключенных к выходам

15и 16 триггера.

Таким образом, после заряда внутреннего узла триггера, связанного со стоком транзистора 9, до уровня напряжения питания транзистор 12 оказывается закрытым, а транзисторы 11 и 14 открытыми по затвору, на прямом 15 и инверсном 16 выходах триггера устанавливаются потенциалы питания и общей шины . соответственно. В дальнейшем триггер по выходам 15 и 16 может управляться внешними логическими сигналами .

Фо-рмула изобретения

Триггер на дополняющих МДП-тран- зисторах, содержащий два инвертора с перекрестными связями, первый транзистор первого типа проводимости, исток которого подключен к шине питания, затвор - к общей шине, сток - к стоку и затвору соответственно второго и третьего транзисторов второго типа проводимости, истоки которых подключены соответственно к общей шине и к выходу первого инвертора, четвертьш транзистор второго типа проводимости, отличающийся тем, что, с целью снижения потребляемой триггером мощности в статическом режиме и повышения надежности его установки в определенное исходное состояние в процессе нарастания напряжения питания, в триггер введены два дополнительных транзистора первого типа проводимости, истоки которых подключены к шине питания, сток первого дополнительного транзистора подключен к выходу первого инвертора.

14659

а его затвор - к затвору четвертого транзистора и стоку второго транзистора, затвор которого подключен к общей шине, при этом затвор второго дополнительного транзистора подключен к шине питания, сток - к выходу второго инвертора и истоку четвертого транзистора, стоки третьего и четвертого транзисторов являются прямым и ю инверсным выходами триггера соответ

бенр ю

ственно, причем , размеры первого и второго транзисторов выбираются из условия О, „ Cj 7 , где 17, - время заряда емкости, связанной.со стоком первого транзистора, С - время заряда емкости, связанной со стоком второго дополнительного транзистора, - время заряда емкости, связанной со стоком первого дополнительного транзистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггер на КМОП транзисторах | 1980 |

|

SU921052A1 |

| Преобразователь уровня напряжений на КМОП-транзисторах | 1987 |

|

SU1471306A1 |

| БАЗОВЫЙ УСИЛИТЕЛЬНЫЙ ЭЛЕМЕНТ ДИФФЕРЕНЦИАЛЬНОЙ ДИНАМИЧЕСКОЙ ЛОГИКИ (ВАРИАНТЫ) | 1999 |

|

RU2154338C1 |

| Преобразователь уровней напряжения на дополняющих МДП-транзисторах | 1983 |

|

SU1129739A1 |

| Усилитель считывания | 1981 |

|

SU970461A1 |

| Буферный усилитель (его варианты) | 1983 |

|

SU1112409A1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДП-ТРАНЗИСТОРАХ | 1995 |

|

RU2107387C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КОМПАРАТОР С ВЫБОРКОЙ ВХОДНОГО СИГНАЛА | 2008 |

|

RU2352061C1 |

| Тактируемый триггер на комплементарных МДП-транзисторах | 1985 |

|

SU1499435A1 |

| Усилитель считывания на моп-транзисторах /его варианты/ | 1980 |

|

SU883968A1 |

Изобретение относится к импульсной технике и может быть использовано в цифровых интегральных схемах, к ко- торьЫ предъявляются требования установки триггеров и триггерных устройств в определенное исходное состояние в процессе нарастания напряжения питания. Цель изобретения - снижение потребляемой триггером мощности в статическом режиме и повышение надежности его установки в определенное исходное состояние в процессе нарастания напряжения питания. Устройство содержит два инвертора 1 и 2 с перекрестными связями, цепь установки триггера в определенное исходное состояние, состоящую из первого, второго, третьего и четвертого транзисторов 9, 10, 11, 14. За счет введения первого и второго дополнительных транзисторов 12, 13 обеспечивается форсированный заряд выхода инвертора 1 в момент нарастанця напряжения питания. Размеры транзисторов 12, 13 выбираются равными, что обеспечивает симметрию емкостной нагрузки на плечи триггера. Размеры первого и второго транзисторов 9, 10 выбираются такими, чтобы время заряда емкости внутреннего узла триггера, связанной со стоком транзистора 9, до уровня порогового напряжения транзисторов 11, 14 и напряжения запирания транзистора 12 превьшало время установления в определенное исходное состояние потенциалов на выходах инверторов 1 и 2. 1 ил. (Л О) ел о со

| Триггер на КМОП транзисторах | 1980 |

|

SU921052A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-03-15—Публикация

1987-02-27—Подача