Изобретение относится к области цифровой вычислительной техники и может быть использовано в МДП больших интегральных схемах (СБИС) в устройствах каскадной логики и конвейерной обработки данных в качестве элемента сумматора, умножителя, мультиплексора, регистра и других арифметико-логических устройств.

Известна реализация логических цифровых устройств на основе КМДП схем типа "домино" (Электроника, 1981, N 20, с.36). Они обладают повышенным быстродействием по сравнению с традиционными статическими МДП элементами. Их недостаток - функциональная ограниченность, обусловленная отсутствием запоминания или фиксации логического состояния в самом элементе, что ограничивает количество последовательно включенных элементов, работающих под общей синхронизацией, и приводит к зависимости быстродействия устройств от числа каскадов логики и требует дополнительной аппаратуры и тактовых сигналов для фиксации и передачи данных, особенно в случае каскадно- конвейерных устройств.

Наиболее близким техническим решением к предлагаемому является парафазное каскадное логическое устройство, предназначенное для выполнения логических операций над несколькими переменными с одновременным выполнением функции фиксации результата и с использованием парафазных входных и выходных сигналов (Европатент, EP H 03 K 19/0948, N 0440514, 03.01.91).

Это устройство, принятое нами за прототип, содержит R-S триггер на инверторах, узлы которого через тактовые транзисторы подключены к выходам логического блока, который содержит не менее четырех комбинационных цепей ключевого типа из МДП транзисторов N-типа. Причем при воздействии заданного набора входных парафазных сигналов одновременно формируются две проводящие цепи. При подаче тактового сигнала один узел триггера коммутируется через первую цепь на шину земли, а второй - через вторую цепь - на шину питания.

Недостатком этого устройства является избыток аппаратуры в логическом блоке, вызванный дублированием комбинационных цепей, и недостаточно высокое быстродействие, обусловленное тем, что перезаряд емкостей нагрузки происходит через комбинационные МДП цепи логического блока. При глубине логики равной трем (три входные переменные) перезаряд нагрузки происходит через четыре МДП транзистора (включая тактовый). При этом нельзя обеспечить высокую скорость переключения, не увеличивая существенным образом размеры МДП транзисторов логического блока. Причем переключение нагрузки с низкого до высокого уровня напряжения через МДП транзисторы происходит медленнее и с потерей уровня напряжения.

Целью изобретения является повышение быстродействия устройства. Дополнительной целью изобретения является повышение надежности устройства.

Поставленная цель достигается тем, что в парафазный логический элемент на МДП транзисторах, содержащий R-S триггер, выходы которого являются парафазными выходами устройства, тактовый транзистор N-типа, затвор которого подключен к тактовой шине, и логический блок, содержащий по меньшей мере две комбинационные цепи, выполненные из последовательно соединенных N-канальных транзисторов каждая, затворы которых подключены к парафазным входам устройства так, что только одна комбинационная цепь нормально замкнута, а все другие - нормально разомкнуты, причем первые выводы комбинационных цепей объединены, а вторые являются соответственно прямым и дополнительным выходами логического блока, введены два предзарядовых транзистора P-типа, затворы которых соединены с тактовой шиной, истоки - с шиной положительного питания, а стоки - с соответствующими выходами логического блока, тактовый транзистор N-типа включен между точкой объединения первых выводов комбинационных цепей и общей шиной, а R-S триггер выполнен на двух элементах 2И-НЕ, первые входы которых являются входами обратной связи и одновременно парафазными выходами R-S триггера, а вторые подключены к соответствующим выходам логического блока.

Для достижения дополнительной цели - повышении надежности - устройство дополнительно содержит два транзистора хранения P-типа, истоки которых соединены с шиной положительного питания, стоки - с соответствующими выходами логического блока, а затворы - с взаимопротивоположными выходами логического блока.

Существенными отличительными признаками в указанной выше совокупности являются выполнение R-S триггера на двухвходовых элементах 2И-НЕ, введение предзарядовых транзисторов P-типа и включение тактового транзистора между общей шиной и точкой объединения первых выводов комбинационных цепей.

Наличие в предлагаемом устройстве перечисленных выше существенных признаков обеспечивает решение поставленной технической задачи - повышение быстродействия устройства. Действительно, процесс переключения элемента заключается в разряде паразитной емкости одного из выходов логического блока (которая была предварительно заряжена до высокого уровня напряжения через предзарядовый транзистор P-типа) через одну из проводящих цепочек МДП транзисторов N-типа и тактовый транзистор N-типа. Одновременно происходит переключение R-S триггера и через МДП транзисторы этого триггера параллельно и независимо от транзисторных цепей логического блока происходит переключение емкостной нагрузки на парафазных выходах устройства. Таким образом, выполнение R-S триггера обеспечивает развязку выходов устройства и выходов логического блока. Цепь переключения внешней нагрузки содержит только один (фронт нарастания) или два (фронт спада) МДП транзистора элемента 2И-НЕ, в то время как цепь логического блока может содержать четыре и более МДП транзисторов. Упрощение логического блока за счет устранения дублирования цепей и соответственно уменьшения в два раза числа МДП транзисторов по сравнению с устройством-прототипом позволяет на той же площади кристалла интегральной схемы увеличить размеры других транзисторов, в частности элементов 2И-НЕ, таким образом дополнительно увеличить быстродействие.

Введение дополнительных транзисторов хранения P-типа обеспечивает поддержку высокого уровня напряжения на том выходе логического блока, состояние которого не должно измениться, т.е. обеспечивается надежная работа на низких частотах и при наличии токов утечки.

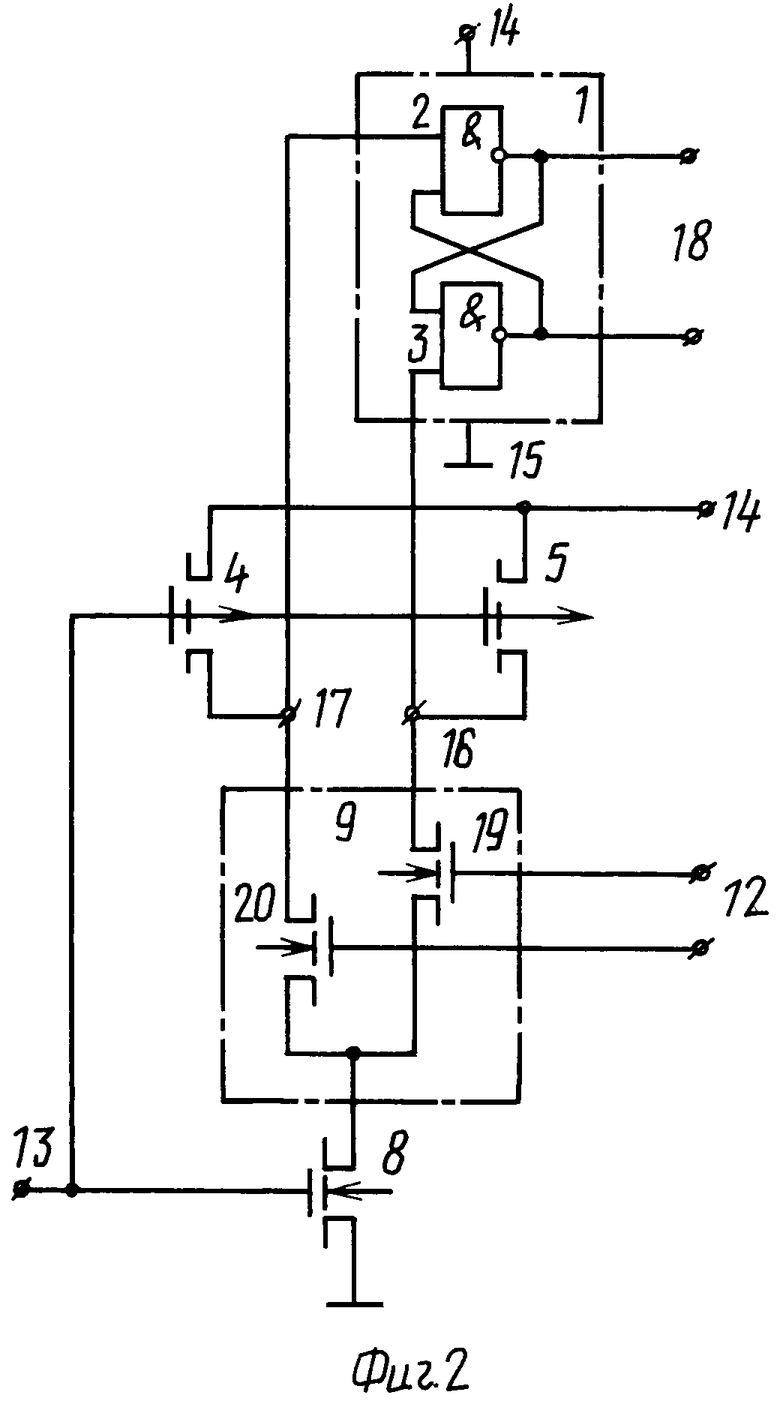

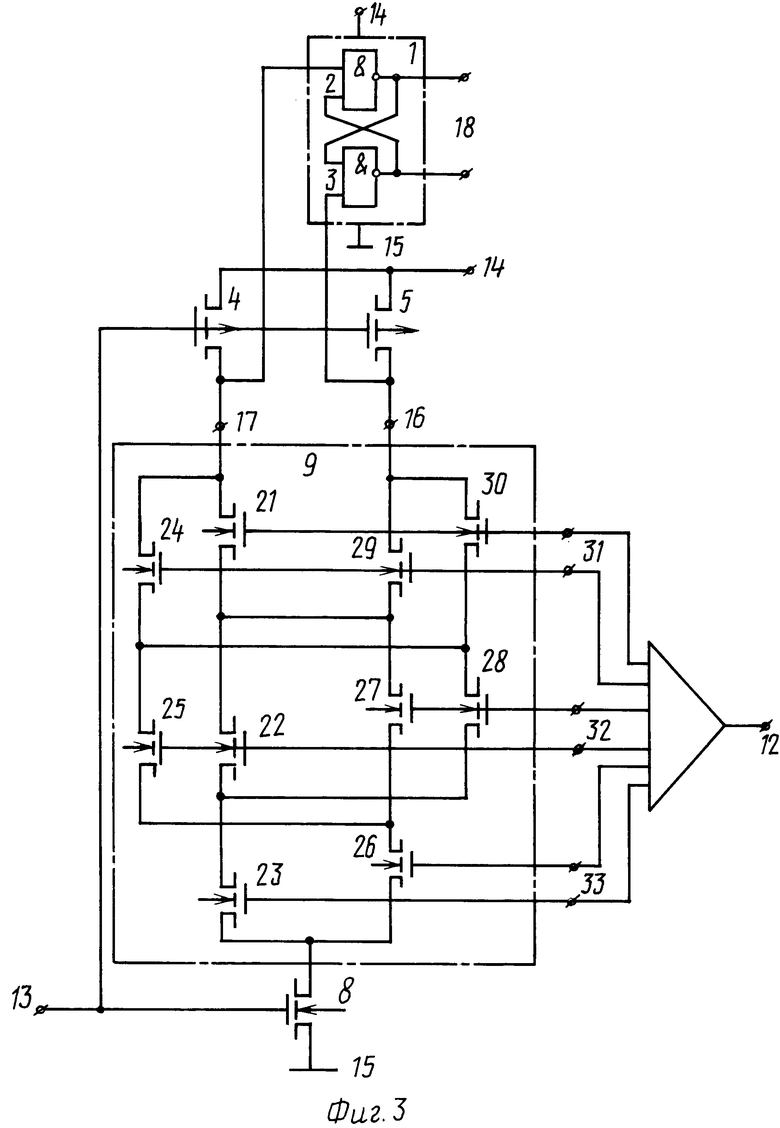

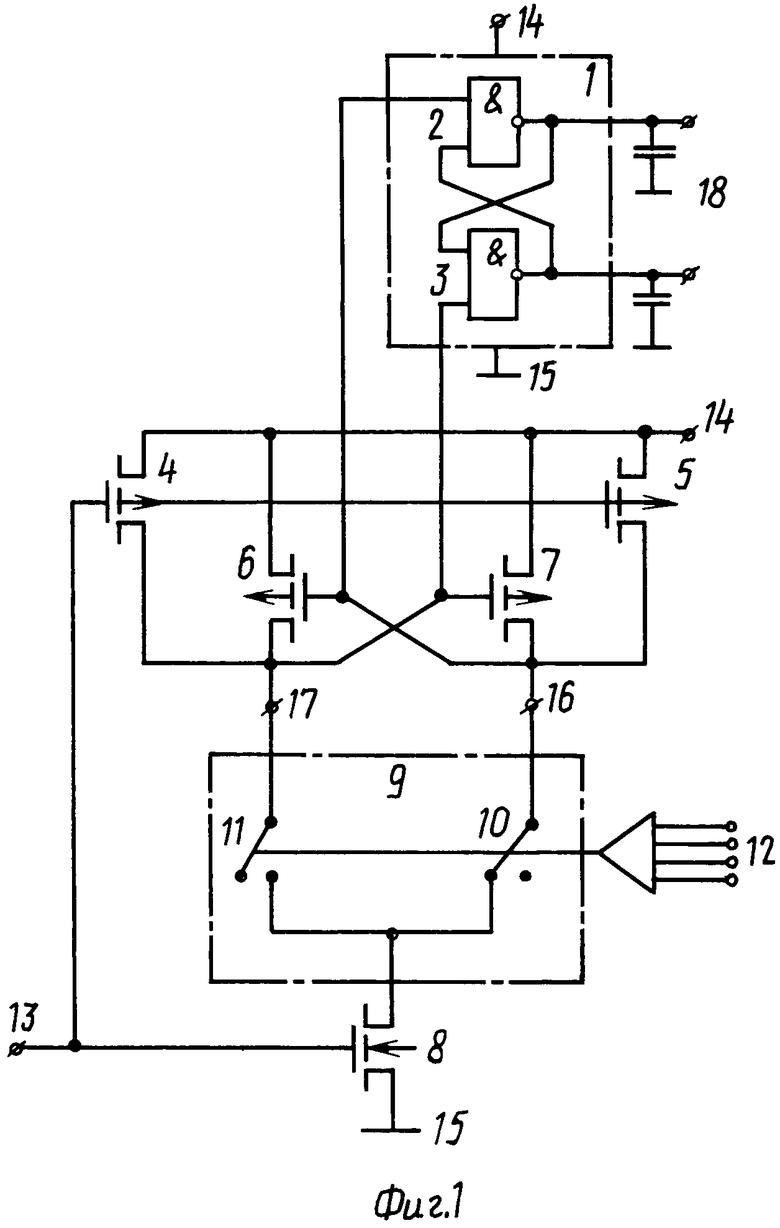

На фиг.1 приведена принципиальная схема парафазного логического элемента в общем виде; на фиг.2 дана реализация этого элемента в качестве Д-триггера; на фиг. 3 - его реализация в качестве однобитного сумматора.

Парафазный логический элемент содержит (фиг.1) R-S триггер 1, выполненный на элементах 2И-НЕ 2 и 3, первый 4 и второй 5 предзарядовые транзисторы P-типа, первый 6 и второй 7 транзисторы хранения P-типа, тактовый транзистор 8 N-типа и логический блок 9, содержащий по меньшей мере две комбинационные цепи, из которых одна 10 - нормально замкнута, а другая 11 - нормально разомкнута. Указанные цепи 10, 11 представляют собой последовательное соединение N-канальных транзисторов, затворы которых подключены к парафазным входам 12 устройства.

Затворы предзарядовых транзисторов 4 и 5 и тактового транзистора 8 подключены к тактовой шине 13. Истоки предзарядовых транзисторов 4 и 5 и транзисторов хранения 6 и 7 соединены с шиной положительного питания 14, а исток тактового транзистора 8 соединен с общей шиной 15.

Первые выводы комбинационных цепей 10 и 11 объединены и соединены со стоком тактового транзистора 8, вторые выводы являются соответственно прямым 16 и дополнительным 17 выходами логического блока 9. К прямому выходу 16 логического блока 9 подключены также стоки второго предзарядового транзистора 5 и второго транзистора хранения 7, а также затвор первого транзистора хранения 6. К дополнительному выходу 17 логического блока 9 подключены стоки первого предзарядового транзистора 4 и первого транзистора хранения 6, а также затвор второго транзистора хранения 7.

Выходы элементов 2И-НЕ 2 и 3 соединены по схеме обратной связи с первыми входами этих же элементов соответственно 3 и 2 и являются одновременно выходами R-S триггера 1 и парафазными выходами 18 логического элемента. Вторые входы элементов 2И-НЕ 2 и 3 подключены соответственно к прямому 16 и дополнительному 17 выходам логического блока 9. R-S триггер 1 включен между шиной положительного питания 14 и общей шиной 15.

При реализации Д-триггера (фиг.2) комбинационные цепи 10 и 11 ключевого типа логического блока 9 выполнены каждая на одном транзисторе - соответственно 19 и 20, а число парафазных входов 12 устройства равно единице.

При реализации парафазного логического элемента в качестве однобитного сумматора (фиг.3). Логический блок 9 выполнен на десяти транзисторах 21-30 и в соответствии с выполняемой функцией от трех переменных в качестве входных парафазных шин имеет три пары парафазных входных шин 31-33.

В соответствии с числом состояний логического элемента от трех переменных равным двум в степени три, т.е. восьми, логический блок 9 содержит восемь комбинационных цепей по три последовательно соединенных транзисторов каждая. К дополнительному выходу 17 логического блока 9 подключены первая цепь (первый 21, второй 22 и третий 23 транзисторы), вторая цепь (четвертый 24, пятый 25 и шестой 26 транзисторы), третья цепь (первый 21, седьмой 27 и шестой 26 транзисторы) и четвертая цепь (четвертый 24, восьмой 28 и третий 23 транзисторы). К прямому выходу 16 логического блока 9 подключены пятая цепь (девятый 29, седьмой 27 и шестой 26 транзисторы), шестая цепь (девятый 29, второй 22 и третий 23 транзисторы), седьмая цепь (десятый 30, пятый 25 и шестой 26 транзисторы) и восьмая цепь (десятый 30, восьмой 28 и третий 23 транзисторы).

Соответственно затворы первого 21 и десятого 30 транзисторов подключено к прямому входу, а затворы четвертого 24 и девятого 29 транзисторов - к обратному входу первой пары 31 парафазных входов 12 устройства. Аналогично затворы седьмого 27, восьмого 28 транзисторов и второго 22, пятого 25 транзисторов подключены к второй паре 32 парафазных входов 12 так же, как затворы шестого 26 и третьего 23 транзисторов подключены к третьей паре 33 парафазных входов устройства.

Вторые выводы всех комбинационных цепей объединены и подключены к стоку тактового транзистора 8. Транзистор, входящий одновременно в две цепи, может рассматриваться как два параллельно по затвору, истоку и стоку включенных транзистора при независимом рассмотрении цепей.

Парафазный логический элемент работает следующим образом. В исходном состоянии на тактовой шине 13 низкий уровень напряжения и тактовый транзистор 6 закрыт, а предзарядовые транзисторы 4 и 5 открыты и через них узловые емкости обоих выходов 16 и 17 логического блока 9 заряжаются до напряжения питания. Наличие на вторых выводах элементов 2И-НЕ 2 и 3 высокого уровня напряжения соответствуют режиму хранения R-S триггера 1. Во время этого полутакта предзаряда на парафазных входах 12 устройства устанавливаются логические сигналы, над которыми необходимо осуществить операцию, соответствующую выполнению логического блока 9.

Комбинационные цепи логического блока 9 построены по известным правилам, когда единичному состоянию цепи соответствует ее замкнутость (проводимость), а нулевому - разомкнутость (см. С. Мурога. Системное проектирование СБИС. М. : Мир, 1985, т. 1, с.197). Таким образом, при любом наборе входных сигналов на шинах 12 (но при обязательном условии противофазности в каждой паре сигналов) только одна комбинационная цепь будет замкнута, остальные - разомкнуты. В качестве ключа используются МДП транзисторы. Число транзисторов в комбинационной цепи равно числу пар входных сигналов. Пусть, например, комбинационная цепь 10 замкнута, а цепь 11 - разомкнута.

При подаче тактового сигнала высокого уровня на тактовую шину 13 предзарядовые транзисторы 4 и 5 закрываются, а тактовый транзистор 8 открывается. При этом создается один единственный путь для тока, который разряжает предварительно заряженную до напряжения положительного питания емкость узла схемы соответствующего прямому выходу 16 логического блока 9. Этот процесс идет достаточно быстро, т.к. величина внутренней емкости узла интегральной схемы невелика (нагрузка - вход элемента 2И-НЕ). Одновременно происходит переключение элемента 2И-НЕ 2 под действием низкого уровня напряжения на его втором входе и далее посредством обратной связи изменяется состояние другого элемента 2И-НЕ 3, т.е. происходит переключение триггера 1 (если тот был в исходном противоположном состоянии). Причем перезаряд конденсаторов, представляющих собой внешнюю емкостную нагрузку элемента на его парафазных выходах 18, происходит только через один МДП транзистор элемента 2И-НЕ (фронт нарастания), или два МДП транзистора такого же элемента 2И-НЕ (фронт спада). Таким образом, выполнение R-S триггера обеспечивает развязку выходов 18 устройства и выходов 16 и 17 логического блока 9, в результате чего большая внешняя нагрузка перезаряжается через один или два транзистора, а малая внутренняя нагрузка перезаряжается через существенно большое число транзисторов, чем и обеспечивается более высокое быстродействие устройства.

Функционирование Д-триггера (по фиг.2) происходит следующим образом. При подаче на парафазные входы 12 элемента кода 1,0 транзистор 19 открыт, а транзистор 20 закрыт. Подачей тактового сигнала обнуляется прямой выход 16 логического блока 9. При подаче кода 0,1 отпирается транзистор 20, а транзистор 19 закрыт. Соответственно обнуляется дополнительный выход 17 логического блока 9 и состояние R-S триггера 1 изменяется на противоположное. Такой Д- триггер требует меньшее число транзисторов и является более быстродействующим, чем известные типы Д-триггеров с парафазным входом и однофазным тактированием.

Аналогично функционируют однобитный сумматор (по фиг.3). При подаче на парафазные входы 31, 32, и 33 соответственно кода 1,0,0 (единица соответствует высокому уровню на верхней клемме каждой пары и низкому уровню на нижней клемме) проводящая комбинационная цепь реализуется на транзисторах - первом 21, втором 22 и третьем 23. При подаче кода 1,1,1 проводящая цепь формируется из транзисторов первого 21, седьмого 27 и шестого 26. В обоих случаях обнуляется дополнительный выход 17 логического блока 9, что соответствует состоянию R-S триггера 1 при сумме равной 1. И наоборот, при подаче кода 1,1,0 проводящая цепь состоит из транзисторов десятого 30, восьмого 28 и третьего 23. В обоих случаях обнуляется прямой выход 16 логического блока 9 и R-S триггер 1 устанавливается в противоположное состояние, соответствующее сумме равной 0.

Подобным же образом реализуется суммирование трех переменных при любом наборе входных сигналов.

После окончания действия тактового сигнала тактовый транзистор 8 закрывается, а предзарядовые транзисторы 4 и 5 открываются и обеспечивают возвращение обоих выходов 16 и 17 логического блока 9 в исходное состояние (высокий уровень напряжения).

Транзисторы хранения 6 и 7 служат для поддержания высокого уровня напряжения на том выходе (16 и 17) логического блока 9, состояние которого не должно измениться во время действия тактового сигнала. Низкий уровень напряжения на том выходе, который обнуляется, открывает противоположный транзистор хранения, через который соответствующий узел схемы с высоким уровнем напряжения подзаряжается от источника положительного питания в том случае, если имеет место потеря уровня напряжения в результате токов утечки, перераспределения зарядов или емкостных связей на фронтах сигналов. Это обеспечивает работу элемента на низких частотах и при воздействии неблагоприятных внешних факторов, т.е. повышается надежность элемента.

При построении устройств каскадной логики выходы логического элемента соединяются с парафазными входами следующего каскада и обеспечивается противофазное тактирование соседних каскадов. .

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КМДП ТРАНЗИСТОРАХ | 2003 |

|

RU2258303C1 |

| МНОГОРАЗРЯДНЫЙ СУММАТОР НА КМДП-ТРАНЗИСТОРАХ | 2003 |

|

RU2239227C1 |

| СУММАТОР НА КМДП ТРАНЗИСТОРАХ | 2001 |

|

RU2185655C1 |

| КАСКАДНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА КМДП ТРАНЗИСТОРАХ | 1998 |

|

RU2132591C1 |

| ПАРАФАЗНОЕ КАСКАДНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА КМДП ТРАНЗИСТОРАХ | 2002 |

|

RU2209507C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КМДП ТРАНЗИСТОРАХ | 2007 |

|

RU2355104C1 |

| КАСКАДНОЕ ПАРАФАЗНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2008 |

|

RU2349028C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2009 |

|

RU2393631C1 |

| ТАКТИРУЕМЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2010 |

|

RU2427073C1 |

| УСТРОЙСТВО СРАВНЕНИЯ НА КМДП ТРАНЗИСТОРАХ | 2003 |

|

RU2236696C1 |

Изобретение относится к цифровой вычислительной технике и может использоваться в МДП больщих интегральных схемах устройств каскадной логики. Повышение быстродействия достигается за счет выполнения R-S триггера 1 логического состяния на элементах 2И-НЕ 2 и 3, введения предзарядовых транзисторов (Т) 4 и 5 и включения тактового Т 8 между общей шиной 15 и точкой объединения комбинационных цепей 10 и 11 ключевого типа логического блока 9, выходы 16 и 17 которого подключены к соответствующим входам R-S триггера 1. 1 з.п. ф-лы, 3 ил.

| EP, патент N 0440514, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1998-03-20—Публикация

1995-12-26—Подача