сд

со оо

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения фазового дрожания | 1987 |

|

SU1469556A1 |

| Адаптивный регенератор | 1986 |

|

SU1363490A1 |

| Формирователь сигналов со сдвигом фазы | 1986 |

|

SU1396239A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2000 |

|

RU2179787C1 |

| Устройство для индикации | 1989 |

|

SU1667150A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ПАКЕТНОЙ ИНФОРМАЦИИ ПО РАДИОКАНАЛУ | 1999 |

|

RU2168282C1 |

| Система связи с асинхронной дельта-модуляцией | 1989 |

|

SU1624695A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1997 |

|

RU2116004C1 |

| Устройство поэлементной синхронизации | 1987 |

|

SU1517142A1 |

| Способ цифрового управления многофазным инвертором | 1989 |

|

SU1683154A1 |

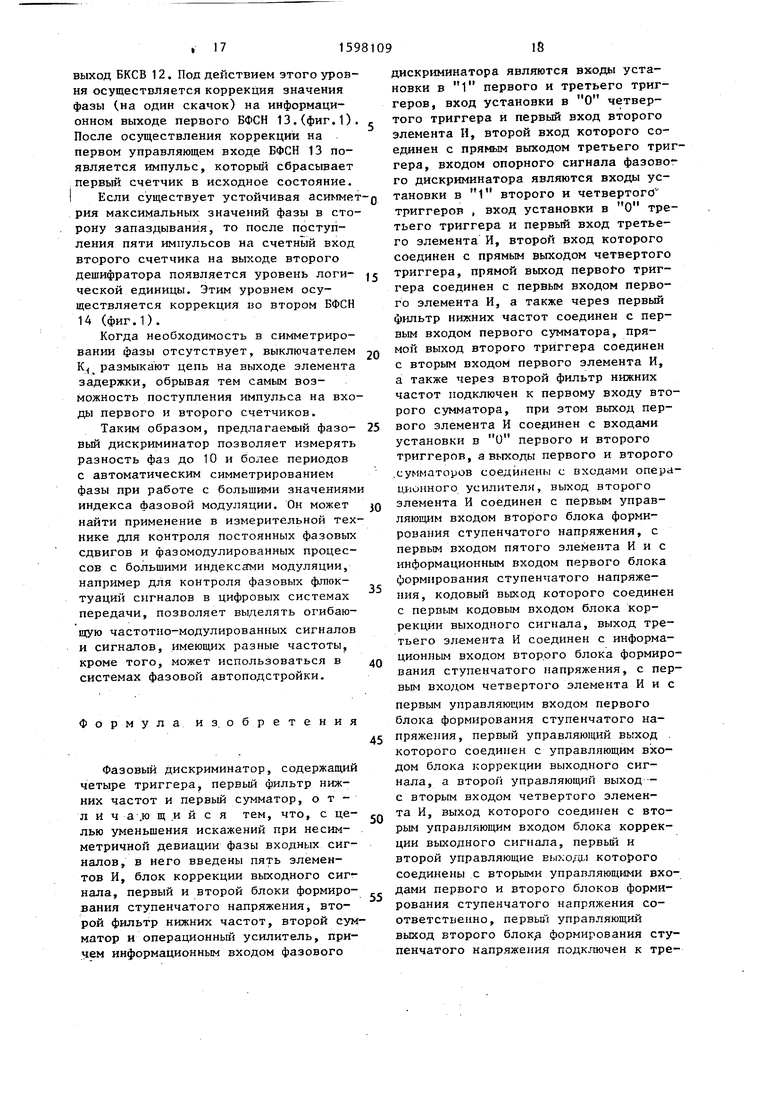

Изобретение относится к измерительной технике и может быть использовано для измерения разности фаз двух сигналов. Целью изобретения является уменьшение искажений при несимметричной девиации фазы входного сигнала. Фазовый дискриминатор содержит триггеры 1-4, фильтры нижних частот (ФНЧ) 5 и 15, сумматоры 6 и 16, элементы И 7-11, блок коррекции выходного сигнала (БКВС) 12, блоки формирования ступенчатого напряжения (БФСН) 13 и 14, операционный усилитель (ОУ) 17. Цель достигается за счет введения элементов И 7-11, БКВС 12, ФНЧ 15, сумматора 16, ОУ 17, БФСН 13 и 14 и их функциональной связи с блоками фазового дискриминатора. Признаком перехода фазы сигнала через точки 2φ, 4φ, 6φ и т.д. является наличие двух подряд импульсов на информационном входе дискриминатора, умещающихся между двумя импульсами на его входе опорного сигнала, либо наличие двух подряд импульсов на входе опорного сигнала дискриминатора умещающихся между двумя импульсами на его информационном входе. 4 ил.

со

Изобретение относится к измери- тельной технике и может быть использовано для измерения разности .фаз двух сигналов, а также в устройст- вах автоматической подстройки частоты и фазы сигналов.

Цель изобретения - уменьшение искажений при несимметричной девиации фазы входного сигнала.

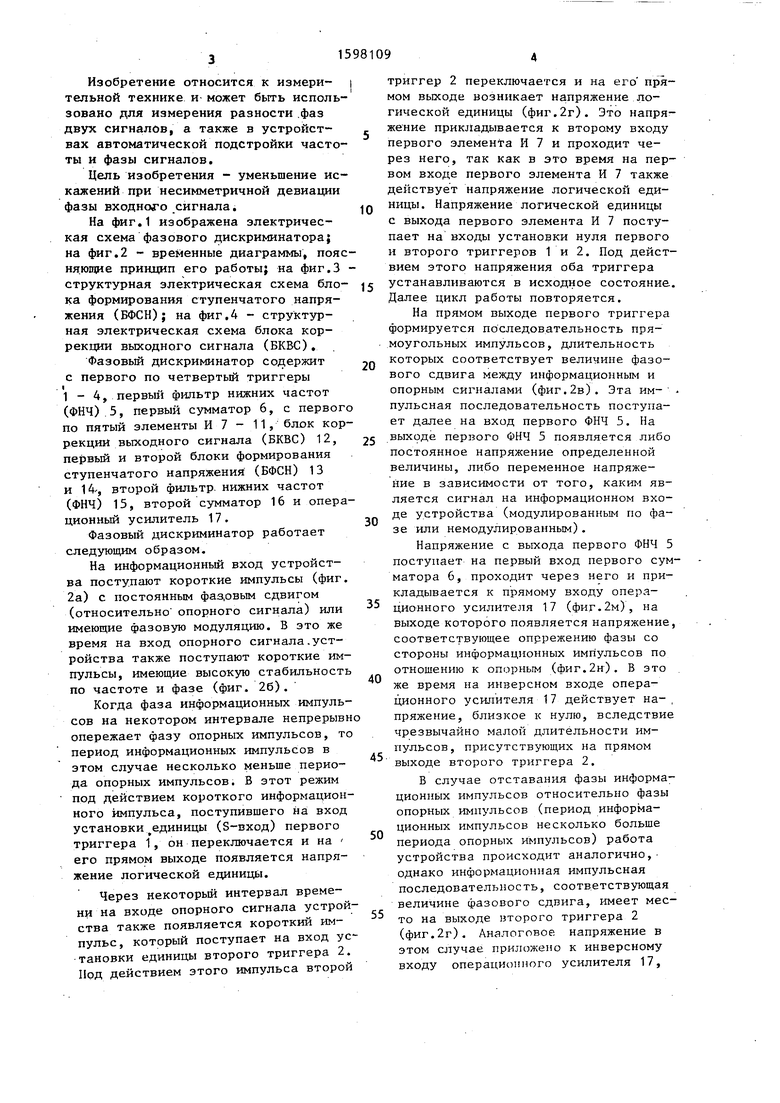

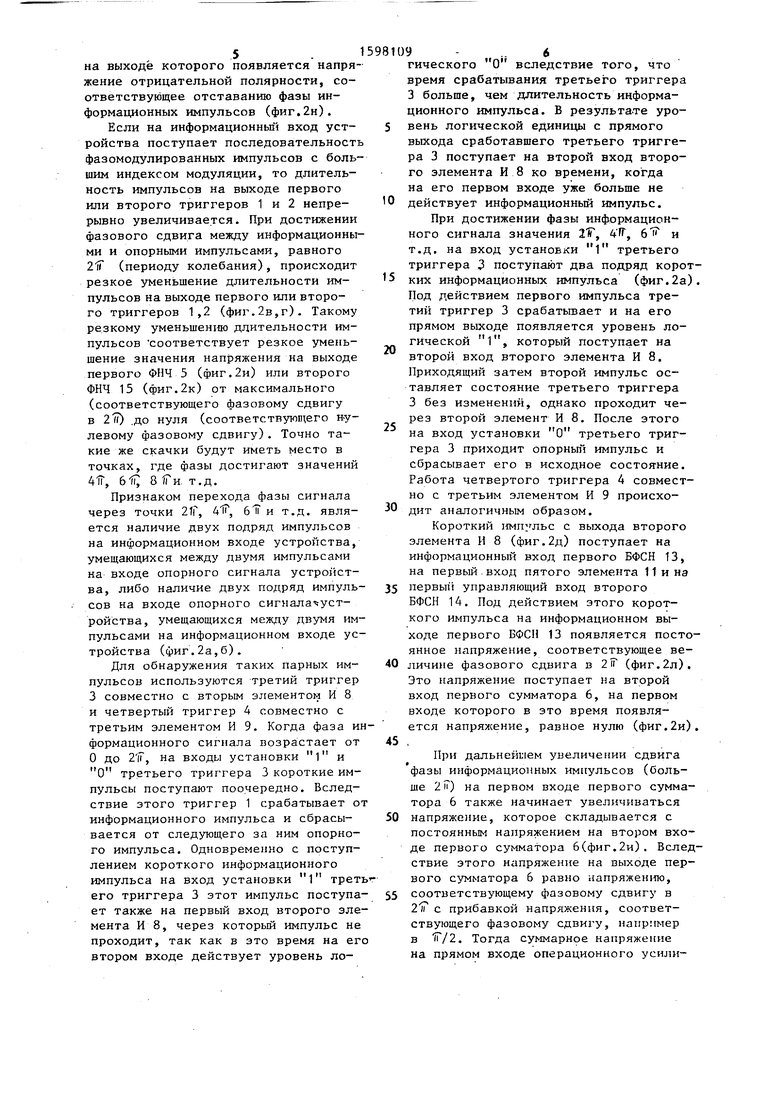

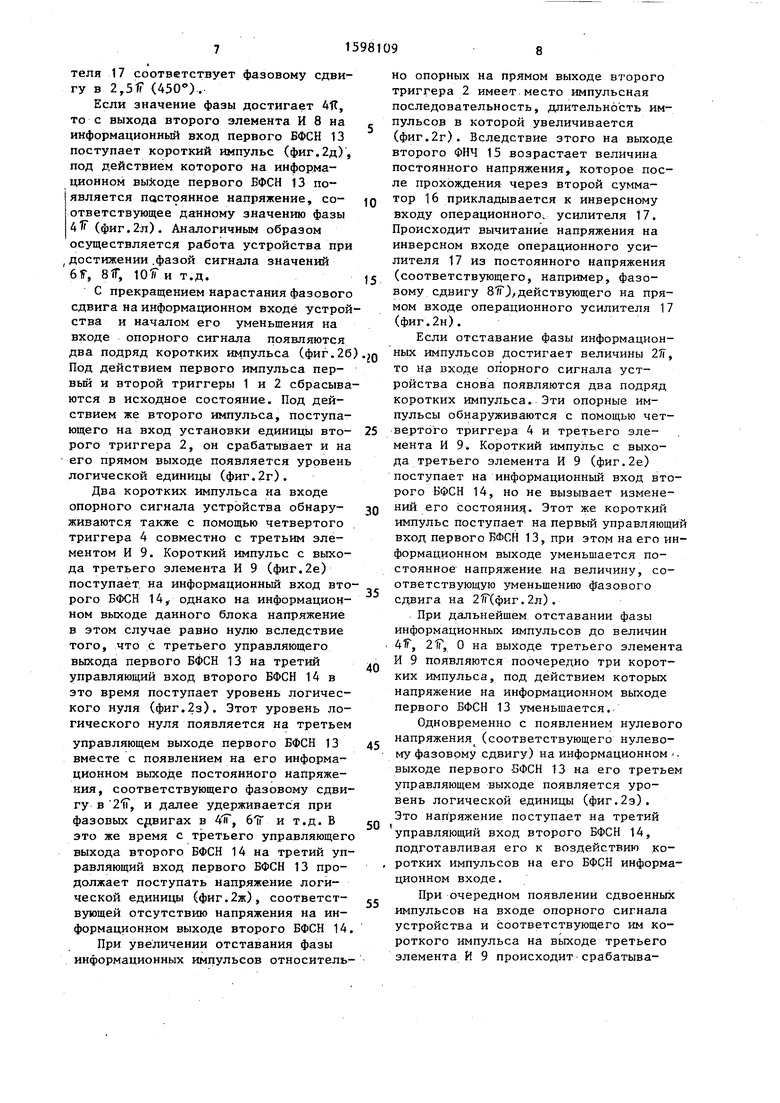

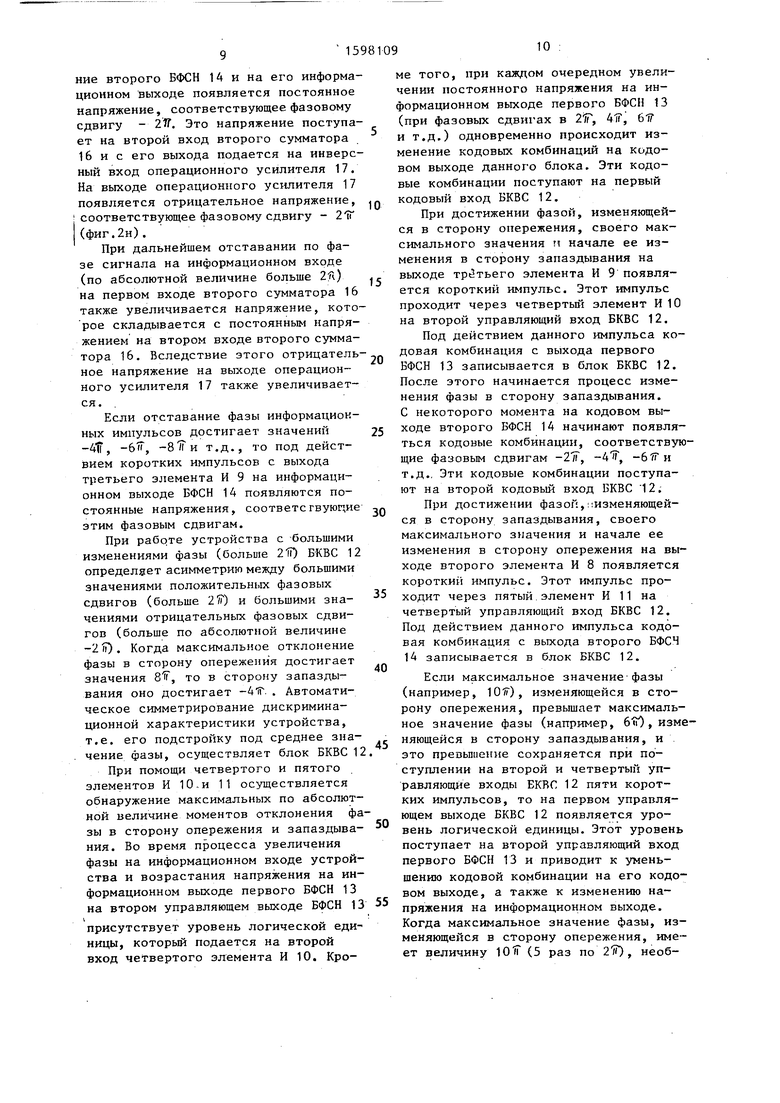

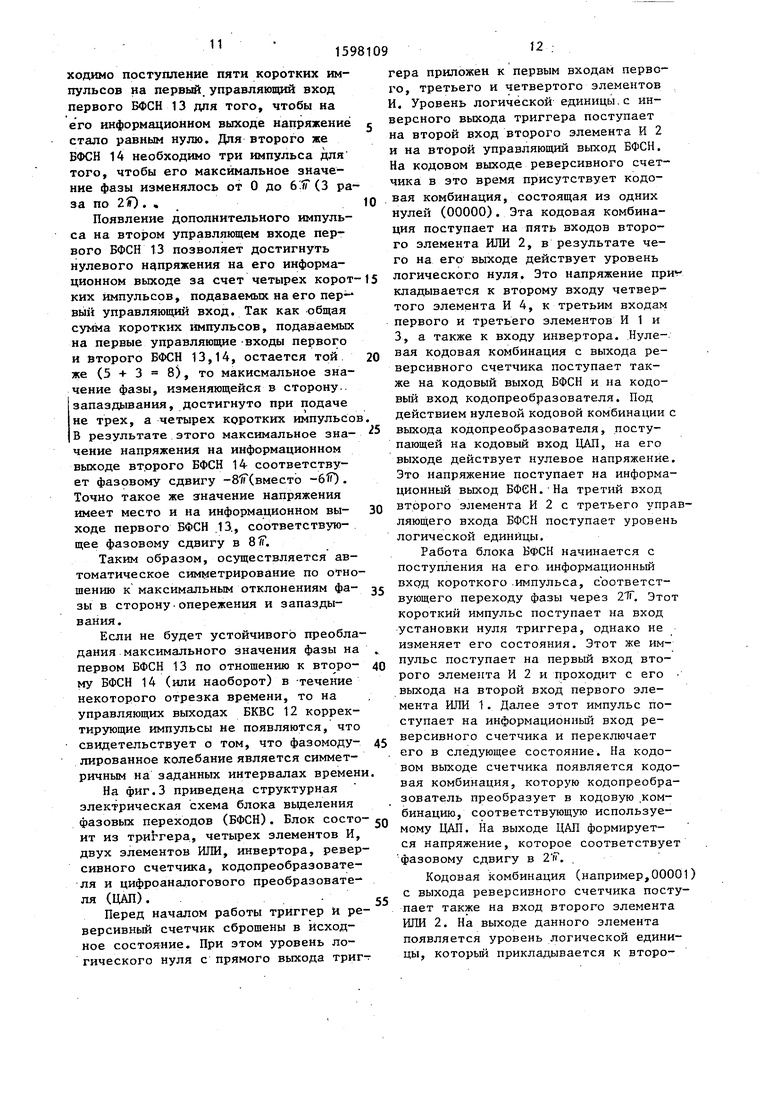

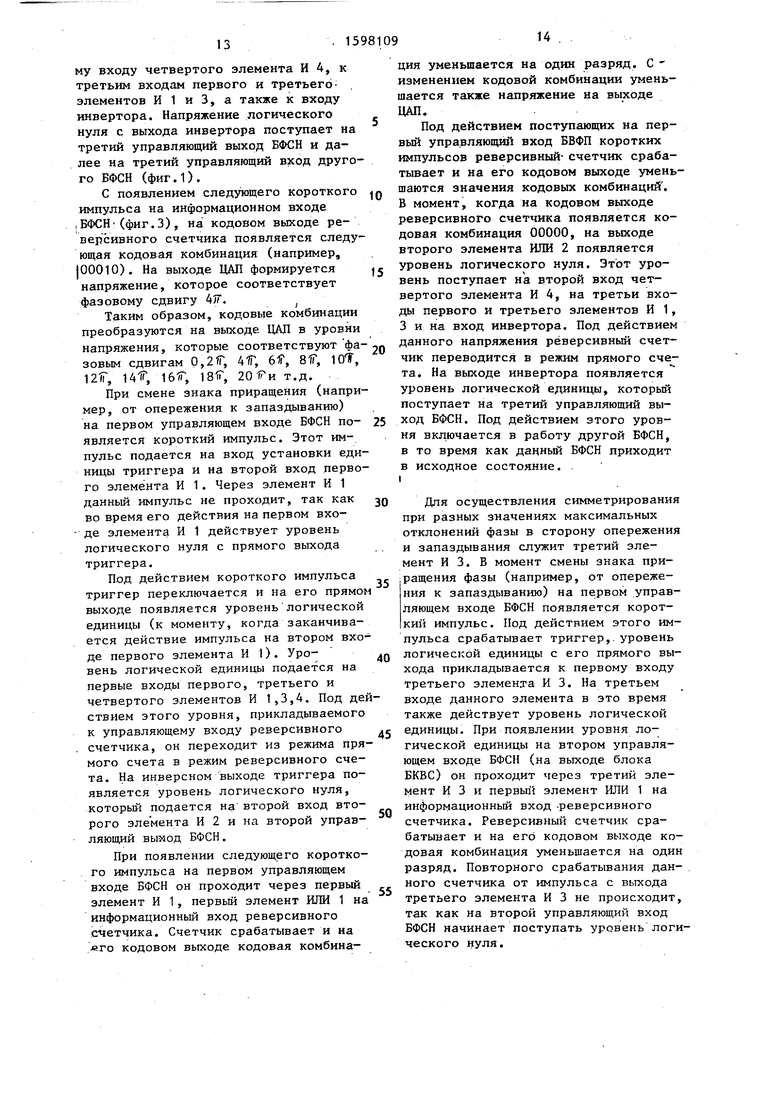

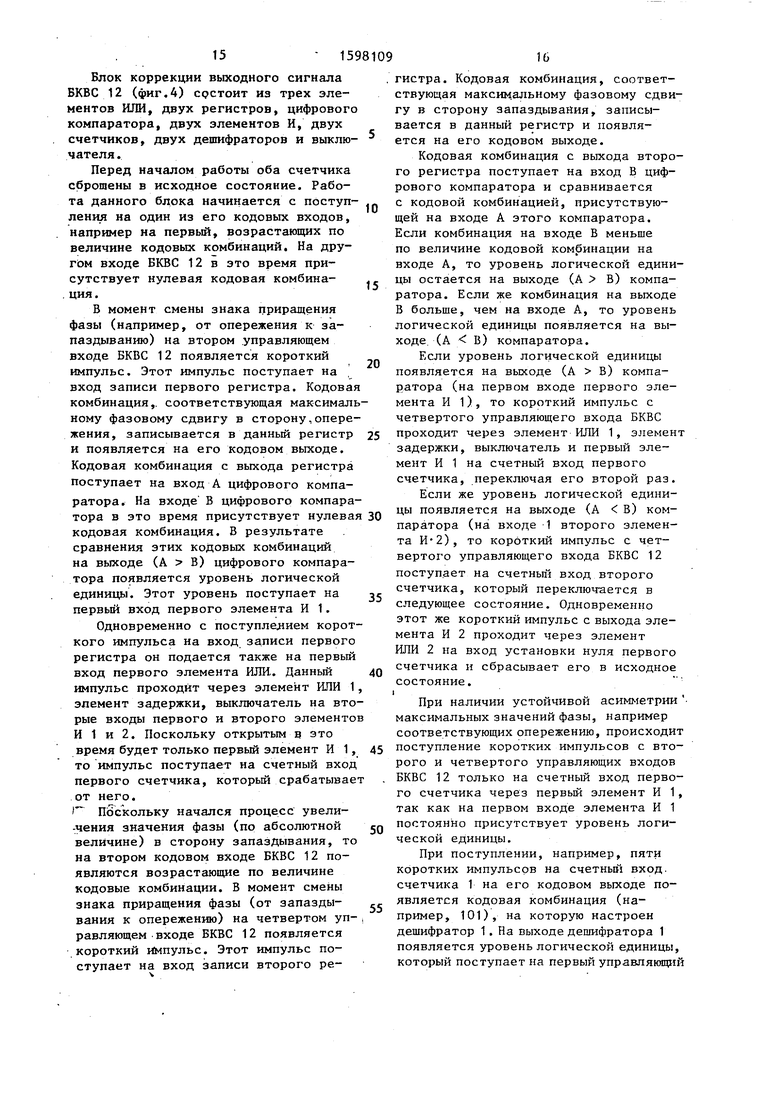

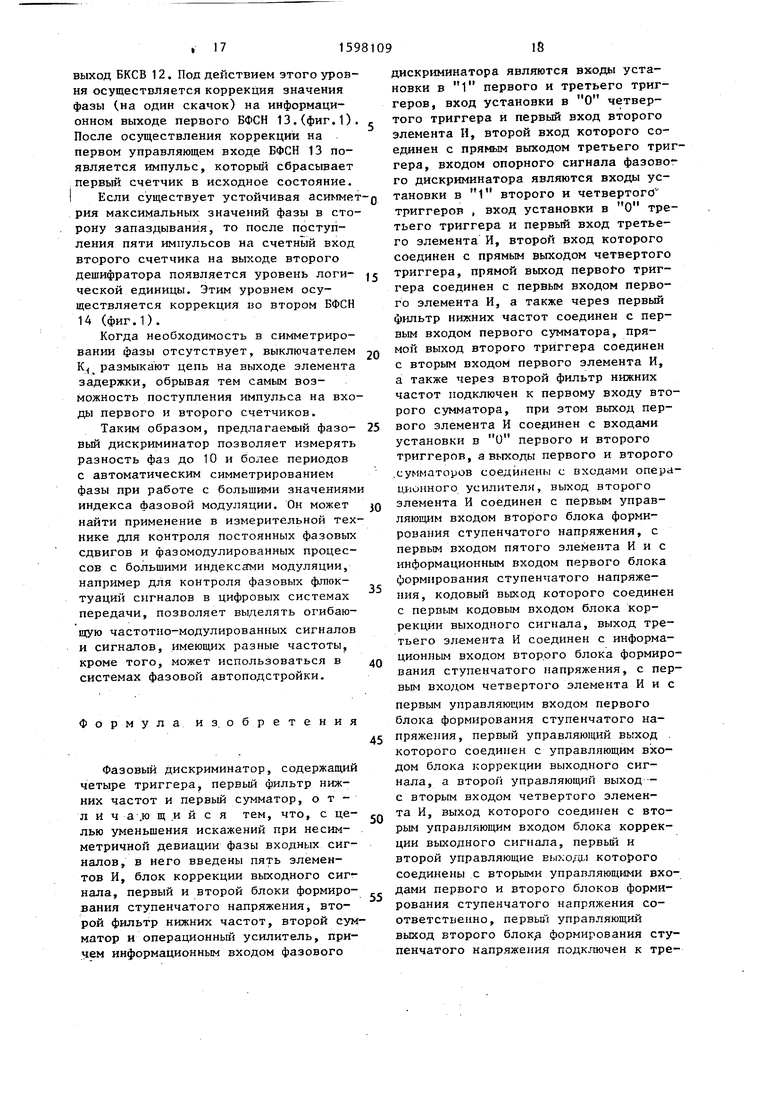

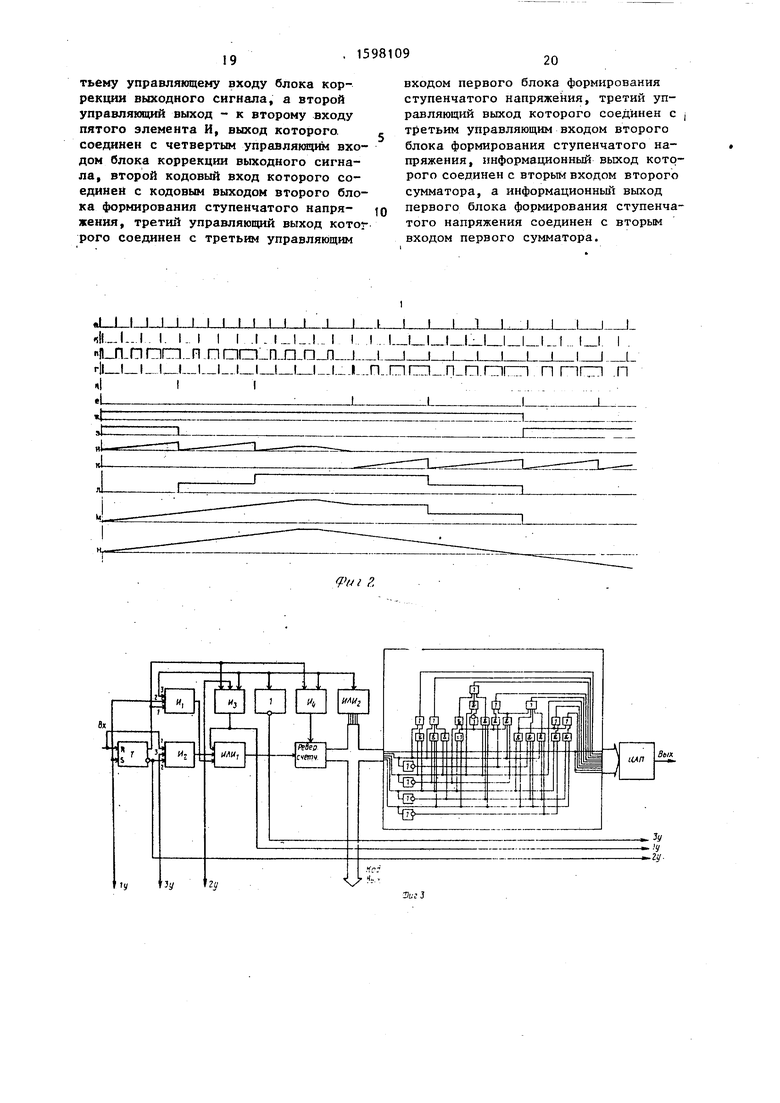

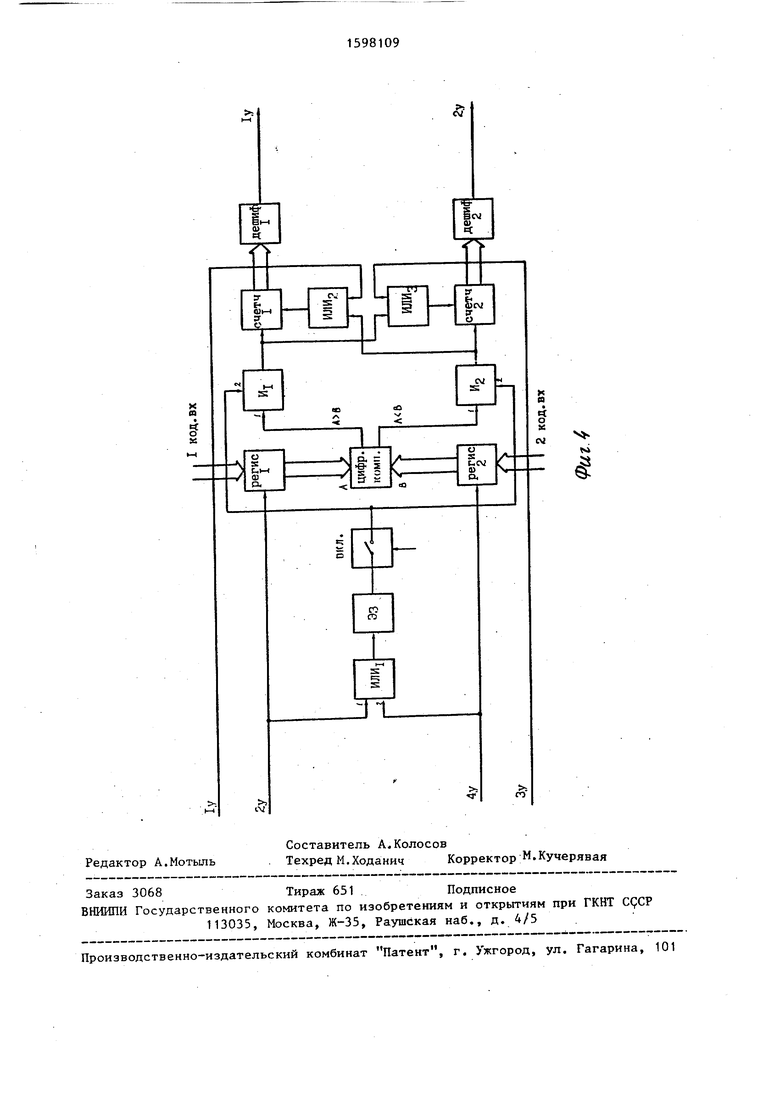

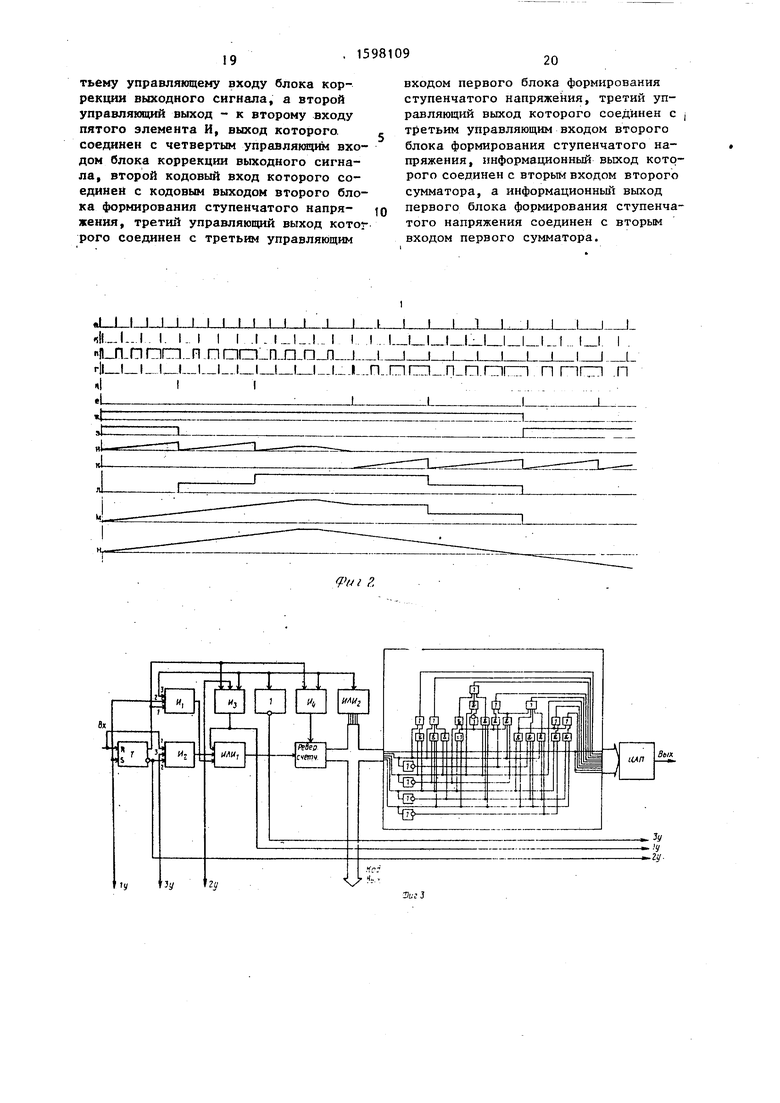

На фиг.1 изображена электрическая схема фазового дискриминатора; на фиг.2 - временные диаграммы, пояс- ня.ющие принцип его работы} на фиг.З - структурная электрическая схема бло- ка формирования ступенчатого напряжения (БФСН); на фиг.4 - структурная электрическая схема блока коррекции выходного сигнала (БКВС),

Фазовый дискриминатор содержит с первого по четвертый триггеры 1 - 4, первый фильтр нижних частот (ФНЧ).5, первый сумматор 6, с первого по пятый элементы И 7 - 11, блок коррекции выходного сигнала (БКВС) 12, первый и второй блоки формирования ступенчатого напряжения (БФСН) 13 и 14, второй фильтр нижних частот (ФНЧ) 15, второй сумматор 16 и операционный усилитель 17.

Фазовый дискриминатор работает следующим образом.

На информационный вход устройства поступают короткие импульсы (фиг. 2а) с постоянным фаз,овым сдвигом (относительно опорного сигнала) или имеющие фазовую модуляцию. В это же время на вход опорного сигнала.устройства также поступают короткие импульсы, имеющие высокую стабильность по частоте и фазе (фиг. 26).

Когда фаза информационных импульсов на некотором интервале непрерывн опережает фазу опорных импульсов, то период информационных импульсов в этом случае несколько меньше периода опорных импульсов. В этот режим под действием короткого информационного импульса, поступившего на вход установки единицы (S-вход) первого триггера 1, он переключается и на его прямом выходе появляется напряжение логической единицы. Через некоторый интервал времени на входе опорного сигнала устрой ства также появляется короткий импульс, который поступает на вход установки единицы второго триггера 2. Иод действием этого импульса второй

0

5

0

5

50

триггер 2 переключается и на его прямом выходе возникает напряжение логической единицы (фиг.2г). Это напряжение прикладывается к второму входу первого элемента И 7 и проходит через него, так как в это время на первом входе первого элемента И 7 также действует напряжение логической единицы. Напряжение логической единицы с выхода первого элемента И 7 поступает на входы установки нуля первого и второго триггеров 1 и 2. Под действием этого напряжения оба триггера устанавливаются в исходное состояние. Далее цикл работы повторяется.

На прямом выходе первого триггера формируется последовательность прямоугольных импульсов, длительность которых соответствует величине фазового сдвига между информационным и опорным сигналами (фиг.2в). Эта им- . пульсная последовательность поступает далее на вход первого ФНЧ 5. На выходе первого ФНЧ 5 появляется либо постоянное напряжение определенной величины, либо переменное напряжение в зависимости от того, каким является сигнал на информационном входе устройства (модулированным по фазе или немодулированным).

Напряжение с выхода первого ФНЧ 5 поступает на первый вход первого сумматора 6, проходит через него и прикладывается к прямому входу операционного усилителя 17 (фиг.2м), на выходе которого появляется напряжение, соответствующее опррежению фазы со стороны информационных импульсов по отношению к опорным (фиг.2н). Б это же время на инверсном входе операционного усилителя 17 действует на- , пряжение, близкое к нулю, вследствие чрезвычайно малой длительности импульсов, присутствующих на прямом выходе второго триггера 2.

В случае отставания фазы информационных импульсов относительно фазы опорных импульсов (период информационных импульсов несколько больше периода опорных импульсов) работа устройства происходит аналогично,- однако информационная импульсная последовательность, соответствующая величине фазового сдвига, имеет место на выходе второго триггера 2 (фиг.2г). Аналоговое напряжение в этом случае приложено к инверсному входу операционного усилителя 17,

на выходе которого появляется напряжение отрицательной полярности, соответствующее отставанию фазы информационных импульсов (фиг.2н).

Если на информационньш вход устройства поступает последовательность фазомодулированных импульсов с большим индексом модуляции, то длительность импульсов на выходе первого или второго триггеров 1 и 2 непрерывно увеличивается. При достижении фазового сдвига между информационными и опорными импульсами, равного 2 |Г (периоду колебания), происходит резкое уменьшение длительности импульсов на выходе первого или второго триггеров 1,2 (фиг.2в,г). Такому резкому уменьшению длительности импульсов соответствует резкое уменьшение значения напряжения на выходе первого ФНЧ 5 (фиг.2и) или второго ФНЧ 15 (фиг.2к) от максимального (соответствующего фазовому сдвигу в 2 ii) .яо нуля (соответствующего нулевому фазовому сдвигу). Точно такие же скачки будут иметь место в точках, где фазы достигают значений Atr, Sfi; 8 f и. т.д.

Признаком перехода фазы сигнала через точки 2ТГ, 41, 6 и т.д. является наличие двух подряд импульсов на информационном входе устройства, умещающихся между двумя импульсами на входе опорного сигнала устройства, либо наличие двух подряд импуль- сов на входе опорного сигнала уст- ройства, умещающихся между двумя импульсами на информационном входе устройства (фиг.2а,б).

Для обнаружения таких парных импульсов используются третий триггер 3 совместно с вторым элементом И 8 и четвертый триггер 4 совместно с третьим элементом И 9. Когда фаза иформационного сигнала возрастает от О до 2 |Т, на входы установки 1 и О третьего триггера 3 короткие импульсы поступают поочередно. Вследствие этого триггер 1 срабатывает о информационного импульса и сбрасы- вается от следующего за ним опорного импульса. Одновременно с поступлением короткого информационного импульса на вход установки 1 трет его триггера 3 этот импульс поступа ет также на первый вход второго элемента И 8, через который импульс не

проходит, так как в это время на его втором входе действует уровень ло

10

20

25

354550 г 55 гического О вследствие того, что время срабатывания третьего триггера 3 больше, чем длительность информационного импульса. В результате уровень логической единицы с прямого выхода сработавшего третьего триггера 3 поступает на второй вход второго элемента ИВ ко времени, когда на его первом входе уже больше не действует информационный импульс.

При достижении фазы информационного сигнала значения 2, 4 Т, 6 и т.д. на вход установки 1 третьего триггера 3 поступают два подряд корот 5 ких информационных импульса (фиг.2а). Под действием первого импульса третий триггер 3 срабатьшает и на его прямом выходе появляется уровень логической 1, который поступает на второй вход второго элемента И 8. Приходящий затем второй импульс оставляет состояние третьего триггера 3 без изменений, однако проходит через второй элемент И 8. После этого на вход установки О третьего триггера 3 приходит опорньп импульс и сбрасывает его в исходное состояние. Работа четвертого триггера 4 совместно с третьим элементом И 9 происходит аналогичным образом.

Короткий 1мпульс с выхода второго элемента И 8 (фиг.2д) поступает на информационный вход первого БФСН 13, на первый вход пятого элемента 11 и на первый управляющий вход второго БФСН 14. Под действием этого короткого импульса на информационном выходе первого БФСН 13 появляется постоянное напряжение, соответствующее ве40 личине фазового сдвига в 2|Г (фиг. 2л). Это напряжение поступает на второй вход первого сумматора 6, на первом входе которого в это время появляется напряжение, равное нулю (фиг.2и).

30

При дальней1;1ем увеличении сдвига фазы информационных импульсов (больше 2ii ) на первом входе первого сумматора 6 также начинает увеличиваться напряжение, которое складывается с постоянным напряжением на втором входе первого сумматора 6(фиг.2и). Вследствие этого напряжение на выходе первого сумматора 6 равно напряжению, соответствующему фазовому сдвигу в 21Г с прибавкой Напряжения, соответствующего фазовому сдвигу, например в |Г/2. Тогда суммарное напряжение на прямом входе операционного усилителя 17 соответствует фазовому сдвигу в 2,5ТГ (450)..

Если значение фазы достигает 4ff, то с выхода второго элемента И 8 на информационный вход первого БФСН 13 поступает короткий импульс (фиг.2д), под действием которого на информационном вызсоде первого БФСН 13 появляется постоянное напряжение, со- ответствующее данному значению фазы (фиг,2л) . Аналогичным образом осуществляется работа устройства при ,достижении.фазой сигнала значений , 81Г, 10 и т.д.

С прекращением нарастания фазового сдвига на информационном входе устройства и началом его уменьшения на входе опорного сигнала появляются два подряд коротких импульса (фиг.26 Под действием первого импульса первый и второй триггеры 1 и 2 сбрасываются в исходное состояние. Под действием же второго импульса, поступающего на вход установки единицы вто- рого триггера 2, он срабатывает и на его прямом выходе появляется уровень логической единицы (фиг.2г).

Два коротких импульса на входе опорного сигнала устройства обнару- живаются также с помощью четвертого триггера 4 совместно с третьим элементом И 9. Короткий импульс с выхода третьего элемента И 9 (фиг.2е) поступает, на информационный вход второго БФСН 14,. однако на информационном выходе данного блока напряжение в этом случае равно нулю вследствие того, что с третьего управляющего выхода первого БФСН 13 на третий управляющий вход второго БФСН 14 в это время поступает уровень логического нуля (фиг.2з). Этот уровень логического нуля появляется на третьем

управляющем выходе первого БФСН 13 вместе с появлением на его информационном выходе постоянного напряжения, соответствующего фазовому сдвигу в 21, и далее удерживается при фазовых сдвигах в 4, б и и т.д. В это же время с третьего управляющего выхода второго БФСН 14 на третий управляющий вход первого БФСН 13 продолжает поступать напряжение логической единицы (фиг.2ж), соответст- вующей отсутствию напряжения на информационном выходе второго БФСН 14.

При увеличении отставания фазы информационных импульсов относитель

Q 5

о

5 Q с

5

но опорных на прямом выходе второго триггера 2 имеет.место импульсная последовательность, длительность импульсов в которой увеличивается (фиг.2г). Вследствие этого на выходе второго ФНЧ 15 возрастает величина постоянного напряжения, которое после прохождения через второй сумматор 16 прикладывается к инверсному входу операционного, усилителя 17. Происходит вычитание напряжения на инверсном входе операционного усилителя 17 из постоянного напряжения (соответствующего, например, фазовому сдвигу 87Г),действующего на прямом входе операционного усилителя 17 (фиг.2н).

Если отставание фазы информационных импульсов достигает величины 27Г, то на входе опорного сигнала устройства снова появляются два подряд коротких импульса. Эти опорные импульсы обнаруживаются с помощью четвертого триггера 4 и третьего элемента И 9. Короткий импульс с выхода третьего элемента И 9 (фиг.2е) поступает на информационный вход второго БФСН 14, но не вызывает изменений его состояние. Этот же короткий импульс поступает на первый управляющий вход первого БФСН 13, при этом на его информационном выходе уменьшается постоянное напряжение на величину, соответствующую уменьшению фазового сдвига на 2 1Г(фиг.2л).

При дальнейшем отставании фазы информационных импульсов до величин . 4F, 2F, О на выходе третьего элемента И 9 появляются поочередно три коротких импульса, под действием которых напряжение на информационном выходе первого БФСН 13 уменьшается.

Одновременно с появлением нулевого напряжения (соответствующего нулевому фазовому сдвигу) на информационном - выходе первого -БФСН 13 на его третьем управляющем выходе появляется уровень логической единицы (фиг.2з). Это напряжение поступает на третий управляющий вход второго БФСН 14, подготавливая его к воздействию ко- , ротких импульсов на его БФСН информационном входе.

При очередном появлении сдвоенных импульсов на входе опорного сигнала устройства и соответствующего им короткого импульса на выходе третьего элемента И 9 происходит срабатыва

ние второго БФСН 14 и на его информационном выходе появляется постоянное напряжение, соответствующее фазовому сдвигу - 2lf, Это напряжение поступает на второй вход второго сумматора 16 и с его выхода подается на инверсный вход операционного усилителя 17. На выходе операционного усилителя 17 появляется отрицательное напряжение, соответствующее фазовому сдвигу - 2 ir (фиг.2н).

При дальнейшем отставании по фазе сигнала на информационном входе (по абсолютной величине больше 2fO на первом входе второго сумматора 16 также увеличивается напряжение, кото- рое складывается с постоянным напряжением на втором входе второго сумматора 16, Вследствие этого отрицательное напряжение на выходе операционного усилителя 17 также увеличивается. .

Если отставание фазы информационных импульсов достигает значений -4f, -б, -8 и т.д., то под действием коротких импульсов с выхода третьего элемента И 9 на информационном выходе БФСН 14 появляются постоянные напряжения, соответствующие этим фазовым сдвигам.

При работе устройства с большими изменениями фазы (больше 2 ir) БКВС 12 определяет асимметрию между большими значениями положительных фазовых сдвигов (больше 2) и большими значениями отрицательных фазовых сдвигов (больше по абсолютной величине -2Я). Когда максимальное отклонение фазы Б сторону опережени я достигает значения Sf, то в сторону запаздывания оно достигает -41Г. . Автоматическое симметрирование дискриминационной характеристики устройства, т.е. его подстройку под среднее значение фазы, осуществляет блок БКВС 1

При помощи четвертого и пятого элементов И 10.и 11 осуществляется обнаружение максимальных по абсолютной величине моментов отклонения фазы в сторону опережения и запаздывания. Во время процесса увеличения фазы на информационном входе устройства и возрастания напряжения на информационном выходе первого БФСН 13 на втором управляющем выходе БФСН 13

присутствует уровень логической единицы, который подается на второй вход четвертого элемента И 10. Кро

5

0

5

55

0

5

0

45

50

ме того, при каждом очередном увеличении постоянного напряжения на информационном выходе первого БФСН 13 (при фазовых сдвигах в 21Г, 4, 61Г и т.д.) одновременно происходит изменение кодовых комбинаций на кодовом выходе данного блока. Эти кодовые комбинации поступают на первый кодовый вход БКВС 12.

При достижении фазой, изменяющейся в сторону опережения, своего максимального значения п начале ее изменения в сторону запаздывания на выходе тр1 тьего элемента И 9 появляется короткий импульс. Этот импульс проходит через четвертый элемент И 10 на второй управляющий вход БКВС 12.

Под действием данного импульса кодовая комбинация с выхода первого БФСН 13 записывается в блок БКВС 12. После этого начинается процесс изменения фазы в сторону запаздывания. С некоторого момента на кодовом выходе второго БФСН 14 начинают появляться кодовые комбинации, соответствующие фазовым сдвигам -27, -4 Г, -бТГи т.д., Эти кодовые комбинации поступают на второй кодовый вход БКВС 12.

При достижении фазой,изменяющейся в сторону запаздывания, своего максимального значения и начале ее изменения в сторону опережения на выходе второго элемента И 8 появляется короткий импульс. Этот импульс проходит через пятый элемент И 11 на четвертый управляющий вход БКВС 12. Под действием данного импульса кодовая комбинация с выхода второго БФСЧ 14 записывается в блок БКВС 12.

Если максимальное значение-фазы (например, 107Г), изменяющейся в сторону опережения, превышает максимальное значение фазы (например, б ЯО , изменяющейся в сторону запаздывания, и это превьпнение сохраняется при поступлении на второй и четвертый управляющие входы БКВС 12 пяти коротких импульсов, то на первом управляющем выходе БКВС 12 появляется уровень логической единицы. Этот уровень поступает на второй управляющий вход первого БФСН 13 и приводит к уменьшению кодовой комбинации на его кодовом выходе, а также к изменению напряжения на информационном выходе. Когда максимальное значение фазы, изменяющейся в сторону опережения, имеет величину 10 Г (5 раз по 250 , необходимо поступление пяти коротких импульсов на первый, управляющий вход первого БФСН 13 для того, чтобы на его информационном выходе напряжение стало равным нулю. Для второго же БФСН 14 необходимо три импульса для того, чтобы его максимальное значение фазы изменялось от О до 6.F (3 раза по 2f). .

Появление дополнительного импульса на втором управляющем входе первого БФСН 13 позволяет достигнуть нулевого напряжения на его информационном выходе за счет четырех корот- ких импульсов, подаваемых на его пер- выи управляющий вход. Так как общая сумма коротких импульсов, подаваемых на первые управляющие входы первого и второго БФСН 13,14, остается той же (), то макисмальное значение фазы, изменяющейся в сторону, запаздьшания, достигнуто при подаче не трех, а четырех коротких импульсов В результате этого максимальное зна- чение напряжения на информационном выходе второго БФСН 14 соответствует фазовому сдвигу -8 /Г(вместо Точно такое же значение напряжения имеет место и на информационном вы- ходе первого БФСН .13., соответствующее фазовому сдвигу в 8.

Таким образом, осуществляется автоматическое симметрирование по отношению к максимальным отклонениям фа- зы в сторонуопережения и запаздывания.

Если не будет устойчивого преобладания максимального значения фазы на первом БФСН 13 по отношению к второ- му БФСН 14 (или наоборот) в -течение некоторого отрезка времени, то на управляющих выходах БКВС 12 корректирующие импульсы не появляются, что свидетельствует о том, что фазомоду- лированное колебание является симметричным на заданных интервалах времен

На фиг.З приведена структурная электрическая схема блока вьщеления фазовых переходов (БФСН). Блок состо ит из триггера, четырех элементов И, двух элементов ИЛИ, инвертора, реверсивного счетчика, кодопреобразователя и цифроаналогового преобразователя (ЦАП).

Перед началом работы триггер И реверсивный счетчик сброшены в Исходное состояние. При этом уровень логического нуля с прямого выхода триггера приложен к первым входам первого, третьего и четвертого элементов И. Уровень логической единицы.с инверсного выхода триггера поступает на второй вход второго элемента И 2 и на второй управляющий выход БФСН. На кодовом выходе реверсивного счетчика в это время присутствует кодовая комбинация, состоящая из одних нулей (00000). Эта кодовая комбинация поступает на пять входов второго элемента ИЛИ 2, в результате чего на его выходе действует уровень логического нуля. Это напряжение при кладывается к второму входу четвертого элемента И 4, к третьим входам первого и третьего элементов И 1 и 3, а также к входу инвертора. Нулевая кодовая комбинация с выхода реверсивного счетчика поступает также на кодовый выход БФСН и на кодовый вход кодопреобразователя. Под действием нулевой кодовой комбинации с выхода кодопреобразователя, поступающей на кодовый вход ЦАП, на его выходе действует нулевое напряжение. Это напряжение поступает на информационный выход БФеН. На третий вход второго элемента И 2 с третьего упраляющего входа БФСН поступает уровень логической единицы.

Работа блока БФСН начинается с поступления на его информационный вхрд короткого .импульса, соответствующего переходу фазы через 2ТГ. Этот короткий импульс поступает на вход установки нуля триггера, однако не изменяет его состояния. Этот же импульс поступает на первый вход второго элемента И 2 и проходит с его выхода на второй вход первого элемента ИЛИ 1. Далее этот импульс поступает на информационный вход реверсивного счетчика и переключает его в следующее состояние. На кодовом выходе счетчика появляется кодовая комбинация, которую кодопреобразователь преобразует в кодовую .комбинацию, соответствующую используемому ЦАП. На выходе ЦАП формируется напряжение, которое соответствует фазовому сдвигу в 2 г7.

Кодовая комбинация (например,000 с выхода реверсивного счетчика постпает также на вход второго элемента НИИ 2. На выходе данного элемента появляется уровень логической единицы, который прикладывается к второму входу четвертого элемента И 4, к третьим входам первого и третьего . элементов И 1 и 3, а также к входу инвертора. Напряжение логического , нуля с выхода инвертора поступает на третий управляющий выход БФСН и далее на третий управляющий вход другого БФСН (фиг.1).

С появлением следующего короткого Q импульса на информационном входе ,БФСН (фиг.3), на кодовом выходе ре- вер сивного счетчика появляется следующая кодовая комбинация (например, J00010). На выходе ЦАП формируется jj напряжение, которое соответствует фазовому сдвигу 4ТГ.

Таким образом, кодовые комбинации преобразуются на выходе ЦАП в уровни напряжения, которые соответствуют фа-2о зовым сдвигам 0,2fi, 41Г, 6IT, StT, lOT, 12tr, Uli; 16, IS iT, т.д.

При смене знака приращения (например, от опережения к запаздыванию)

ция уменьшается на один разряд. С изменением кодовой комбинации уменьшается также напряжение на выходе ЦАП.

Под действием поступающих на первый управляющий вход БВФП коротких импульсов реверсивный- счетчик срабатывает и на его кодовом выходе умень шаются значения кодовых комбинаций . В момент, когда на кодовом выходе реверсивного счетчика появляется кодовая комбинация 00000, на выходе второго элемента ИЛИ 2 появляется уровень логического нуля. Этот уровень поступает на второй вход четвертого элемента И 4, на третьи входы первого и третьего элементов И 1, 3 и на вход инвертора. Под действием данного напряжения реверсивный счетчик переводится в режим прямого счета. На выходе инвертора появляется уровень логической единицы, который поступает на третий управляющий вына первом управляющем входе БФСН по- 25 ОД БФСН. Под действием этого уров30

35

является короткий импульс. Этот импульс подается на вход установки единицы триггера и на второй вход первого элемента И 1. Через элемент И 1 данный импульс не проходит, так как во время его действия на первом входе элемента И 1 действует уровень логического нуля с прямого выхода триггера.

Под действием короткого импульса триггер переключается и на его прямом выходе появляется уровень логической единицы (к моменту, когда заканчивается действие импульса на втором входе первого элемента И 1). Уро- Q вень логической единицы подается на первые входы первого, третьего и четвертого элементов И 1,3,4. Под действием этого уровня, прикладываемого к управляющему входу реверсивного j счетчика, он переходит из режима прямого счета в режим реверсивного счета. На инверсном выходе триггера появляется уровень логического нуля, который подается на второй вход второго элемента И 2 и на второй управляющий выход БФСН.

При появлении следующего короткого импульса на первом управляющем входе БФСН он проходит через первый , элемент И 1, первый элемент ИЛИ 1 на информационный вход реверсивного счетчика. Счетчик срабатывает и на .его кодовом выходе кодовая комбина,- 50

ня включается в работу другой БФСН, в то время как данный БФСН приходит

в исходное состояние. I

Для осуществления симметрировани при разных значениях максимальных отклонений фазы в сторону опережени и запаздывания служит третий элемент И 3. Б момент смены знака приращения фазы (например, от опережения к запаздыванию) на первом управ ляющем входе БФСН появляется корот- ки11 импульс. Под действием этого им пульса срабатывает триггер,, уровень логической единицы с его прямого вы хода прикладывается к первому входу третьего элемента ИЗ. На третьем входе данного элемента в это время также действует уровень логической единицы. При появлении уровня логической единицы на втором управляющем входе БФСН (на выходе блока БКВС) он проходит через третий элемент И 3 и первый элемент ИЛИ 1 на информационный вход .реверсивного счетчика. Реверсивный счетчик срабатывает и на его кодовом выходе ко довая комбинация уменьшается на оди разряд. Повторного срабатывания дан ного счетчика от импульса с выхода третьего элемента И 3 не происходит так как на второй управляющий вход БФСН начинает поступать уровень лог ческого нуля.

ция уменьшается на один разряд. С изменением кодовой комбинации уменьшается также напряжение на выходе ЦАП.

Под действием поступающих на первый управляющий вход БВФП коротких импульсов реверсивный- счетчик срабатывает и на его кодовом выходе уменьшаются значения кодовых комбинаций . В момент, когда на кодовом выходе реверсивного счетчика появляется кодовая комбинация 00000, на выходе второго элемента ИЛИ 2 появляется уровень логического нуля. Этот уровень поступает на второй вход четвертого элемента И 4, на третьи входы первого и третьего элементов И 1, 3 и на вход инвертора. Под действием данного напряжения реверсивный счетчик переводится в режим прямого счета. На выходе инвертора появляется уровень логической единицы, который поступает на третий управляющий вы25 ОД БФСН. Под действием этого уров30

35

Qj ,

50

ня включается в работу другой БФСН, в то время как данный БФСН приходит

в исходное состояние. I

Для осуществления симметрирования при разных значениях максимальных отклонений фазы в сторону опережения и запаздывания служит третий элемент И 3. Б момент смены знака приращения фазы (например, от опережения к запаздыванию) на первом управляющем входе БФСН появляется корот- ки11 импульс. Под действием этого импульса срабатывает триггер,, уровень логической единицы с его прямого выхода прикладывается к первому входу третьего элемента ИЗ. На третьем входе данного элемента в это время также действует уровень логической единицы. При появлении уровня логической единицы на втором управляющем входе БФСН (на выходе блока БКВС) он проходит через третий элемент И 3 и первый элемент ИЛИ 1 на информационный вход .реверсивного счетчика. Реверсивный счетчик срабатывает и на его кодовом выходе кодовая комбинация уменьшается на один разряд. Повторного срабатывания дан- . ного счетчика от импульса с выхода третьего элемента И 3 не происходит, так как на второй управляющий вход БФСН начинает поступать уровень логического нуля.

10

15

20

15 - 1598109

Блок коррекции выходного сигнала КВС 12 (фиг,4) CQCTOHT из трех элеентов ИЛИ, двух регистров, цифрового омпаратора, дв5гх элементов И, двух четчиков, двух дешифраторов и выклю- ателя.

Перед началом работы оба счетчика брошены в исходное состояние. Рабоа данного блока начинается с поступения на один из его кодовых входов, например на первый, возрастаюпщх по величине кодовых комбинаций. На другом входе БКВС 12 в это время присутствует нулевая кодовая комбина- ция.

В момент смены знака приращения фазы (например, от опережения к запаздыванию) на втором управляющем входе БКВС 12 появляется короткий импульс. Этот импульс поступает на вход записи первого регистра. Кодовая комбинация,, соответствующая максимальному фазовому сдвигу в сторону,опережения, записывается в данный регистр 25 и появляется на его кодовом выходе. Кодовая комбинация с выхода регистра поступает на вход А цифрового компаратора. На входе В цифрового компаратора в это время присутствует нулевая 30 кодовая комбинация. В результате сравнения этих кодовых комбинаций на выходе (А В) цифрового компаратора появляется уровень логической единицы. Этот уровень поступает на 5 первый вход первого элемента И 1.

Одновременно с поступлением короткого импульса на вход записи первого регистра он подается также на первый вход первого элемента ИЛИ.. Данный 40 импульс проходит через элемент ИЛИ 1, элемент задержки, выключатель на вторые входы первого и второго элементов И 1 и 2, Поскольку открытым в это время будет только первый элемент И 1, 45 то импульс поступает на счетный вход первого счетчика, который срабатывает от него.

Поскольку начался процесс увели- -чения значения фазы (по абсолютной величине) в сторону запаздывания, то на втором кодовом входе БКВС 12 появляются возрастающие по величине кодовые комбинации. В момент смеНы знака приращения фазы (от запаздывания к опережению) на четвертом управляющем входе БКВС 12 появляется короткий импульс. Этот импульс поступает на вход записи второго ре50

55

0

5

0

109

2530 5

40 45

50

55

16

гистра. Кодовая комбинация, соответствующая максим.альному фазовому сдвигу в сторону запаздывания, записывается в данный регистр и появляется на его кодовом выходе.

Кодовая комбинация с выхода второго регистра поступает на вход В цифрового компаратора и сравнивается с кодовой комбинацией, присутствующей на входе А этого компаратора. Если комбинация на входе В меньше по величине кодовой комбинации на входе А, то уровень логической единицы остается на выходе (А В) компаратора. Если же комбинация на выходе В больше, чем на входе А, то уровень логической единицы появляется на выходе. (А В) компаратора.

Если уровень логической единицы появляется на выходе (А В) компаратора (на первом входе первого элемента И 1), то короткий импульс с четвертого управляющего входа БКВС проходит через элемент ИЛИ 1, элемент задержки, выключатель и первый элемент И 1 на счетный вход первого счетчика, переключая его второй раз.

Если же уровень логической единицы появляется на выходе (А В) ком- пара.тора (на входе 1 второго элемента И-2), то короткий импульс с четвертого управляющего входа БКВС 12 поступает на счетный вход второго счетчика, который переключается в следующее состояние. Одновременно этот же короткий импульс с выхода элемента И 2 проходит через элемент ИЛИ 2 на вход установки нуля первого счетчика и сбрасывает его в исходное состояние.

При наличии устойчивой асимметрии максимальных значений фазы, например соответствующих опережению, происходит поступление коротких импульсов с второго и четвертого управляющих входов БКВС 12 только на счетный вход первого счетчика через первый элемент И 1, так как на первом входе элемента И 1 постоянно присутствует уровень логической единицы.

При поступлении, например, пяти коротких импульсов на счетный вход, счетчика 1 на его кодовом выходе появляется кодовая комбинация (например, 101), на которую настроен дешифратор 1. На выходе дешифратора 1 появляется уровень логической единицы, который поступает на первый управляющий

выход БКСВ 12, Под действием этого уровня осуществляется коррекция значения фазы (.на один скачок) на информационном выходе первого БФСН 13.(фиг.1). После осуществления коррекции на первом управляющем входе БФСН 13 появляется импульс, который сбрасывает первый счетчик в исходное состояние. I Если существует устойчивая асиммет рия максимальных значений фазы в сторону запаздывания, то после поступления пяти импульсов на счетный вход второго счетчика на выходе второго дещифратора появляется уровень логи- ческой единицы. Этим уровнем осуществляется коррекция во втором БФСН 14 (фиг.1).

Когда необходимость в симметрировании фазы отсутствует, выключателем К размыкают цепь на выходе элемента задержки, обрывая тем самым возможность поступления импульса на входы первого и второго счетчиков.

Таким образом, предлагаемый фазо- вый дискриминатор позволяет измерять разность фаз до 10 и более периодов с автоматическим симметрированием фазы при работе с большими значениям индекса фазовой модуляции. Он может найти применение в измерительной технике для контроля постоянных фазовых сдвигов и фазомодулированных процессов с большими индексами модуляции, например для контроля фазовых фгаок- туаций сигналов в цифровых системах передачи, позволяет выделять огибающую частотно-модулированных сигналов и сигналов, имеющих разные частоты, кроме того, может использоваться в системах фазовой автоподстройки.

Формула из. обретения

Фазовый дискриминатор, содержащий четыре триггера, первый фильтр нижних частот и первый сумматор, о т - л и ч а .ю щ и и с я тем, что, с це- лью уменьшения искажений при несимметричной девиации фазы входных сигналов, в него введены пять элементов И, блок коррекции выходного сигнала, первый и второй блоки формиро- вания ступенчатого напряжения, второй фильтр нижних частот, второй сумматор и операционный усилитель, причем информационным входом фазового

0

5 Q О

5

Q .

дискриминатора являются входы установки в 1 первого и третьего триггеров, вход установки в О четвертого триггера и первый вход второго элемента И, второй вход которого соединен с прямым выходом третьего триггера, входом опорного сигнала фазового дискриминатора являются входы установки в 1 второго и четвертого триггеров , вход установки в О третьего триггера и первый вход третьего элемента И, второй вход которого соединен с прямьм выходом четвертого триггера, прямой выход первого триггера соединен с первым входом первого элемента И, а также через первый фильтр нижних частот соединен с первым входом первого сумматора, прямой выход второго триггера соединен с вторым входом первого элемента И, а также через второй фильтр нижних частот подключен к первому входу второго сумматора, при этом выход первого элемента И соединен с входами установки в О первого и второго триггеров, а выходы первого и второго .сумматоров соединены с входами операционного усилителя, выход второго элемента И соединен с первым управляющим входом второго блока формирования ступенчатого напряжения, с первым входом пятого элемента И и с информационным входом первого блока формирования ступенчатого напряжения, кодовый выход которого соединен с первым кодовым входом блока коррекции выходного сигнала, выход тре тьего элемента И соединен с информационным входом второго блока формирования ступенчатого напряжения, с первым входом четвертого элемента И и с первым управляющим входом первого блока формирования ступенчатого напряжения, первый управляющий выход которого соединен с управляющим входом блока коррекции выходного сигнала, а второй управляющий выход - с вторым входом четвертого элемента И, выход которого соединен с вторым управляющим входом блока коррекции выходного сигнала, первый и второй управляющие выхо/д. которого соединены с вторыми управляющими входами первого и второго блоков формирования ступенчатого напряжения соответственно, первый управляющий выход второго блок формирования ступенчатого напряжения подключен к третьему управляющему входу блока коррекции выходного сигнала, а второй управляняций выход - к второму входу пятого элемента И, выход которого, соединен с четвертым управляклцнм входом блока коррекции выходного сигнала, второй кодовый вход которого соединен с кодовым выходом второго блока формирования ступенчатого напряжения, третий управляющий выход котог рого соединен с третьим управляющим

.1 I I I I I I I I I I I I I 1|.L

J L jI:iIi

ili-l-i I. I-I I I .1 - I-1--I.. I I I. I I I

lui-D nn.n n nrn ;n n n n jiiijiiГ 7 ii L

,..1...L..n..mni.. men n mrzi n

I:i.1Ij

7

входом первого бпока формирования ступенчатого напряжения, третий управляющий выход которого соединен с j третьим управляющим входом второго блока формирования ступенчатого напряжения, информационный выход которого соединен с вторьм входом второго сумматора, а информационньи выход первого блока формирования ступенчатого напряжения соединен с вторым входом первого сумматора.

Btir.

Уиг J

X

n g

iu

N

Nk

| Фазовый дискриминатор | 1978 |

|

SU809482A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-10-07—Публикация

1988-04-14—Подача