Изобретение относится к вычислительной технике и может быть исполь- зойано в специализированных процес- для преобразования координат группы осесизд етричных векторов.

Цель изобретения - повышение быстродействия и расширение класса решаемых задач за счет преобразования группы; векторов,10

:Рассмотрим функциональное нааначе- ниф предлагаемого устройства, В ряде практических задач возникает необходи- мофть вычисления матрицы:

,(1) 15

мационных входов устройства, вход 20 начальной установки устройства, выход

21строба устройства, мультиплексоры

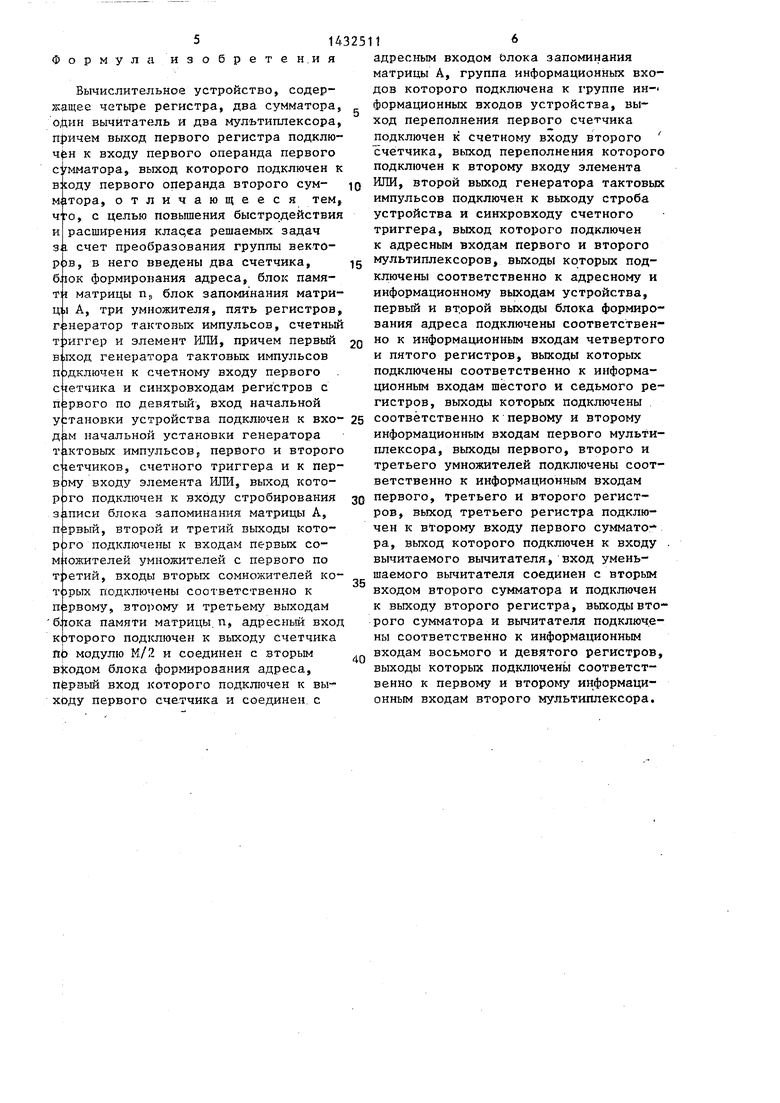

22и 23, регистры 24 - 27, адресный выход 28 устройства, 1информационный выход 29 устройства, элемент ИПИ 30. Блок 5 содержит группы регистров 31 - 33 и группу мультиплексоров 34. Блок 3 содержит блок 35 памяти и сумматор 36. На адресньй вход блока 4 поступает значение Р с выхода счетчика 2, при этом на первый, второй, третий выходы блока 4 выдаются соответствен но значения п

гдф N

Йт

- матрица размерности МхЗ, где М - количество векторов в группе; т - символ транспортирования; . 20 А(а -j) матрица размерР..,

и п

РГ

Блок 35

памяти БФА 3 адресуется значениями Р и К со счетчиков соответственно 2 и 1. При этом на выход блока 35 выдается

значение Ар ЗР+К, которое поступает ц

п

п

п

на первый выход БФА 3 и является адресом записи NO (т.е. номером этого

элемента в матрице N); на второй вынести 3X3.

матрица размерности МхЗ,

обладающая следующими т.л

„ ход БФА 3 поступает значение А,, А- свойствами: пусть вектор25t| г.

) - Р-я

Р ( строка матрицы п, тогда

для любого , М/2-1 существует Номер .+0,5М такой, что п

+1,5 М, которое является адресом записи N

е,

(-п

Ро

-п

- Е

30

Pl f1

npj:Предлагается следующий алгоритм расчета матрицы.

+п,

М,

1.Расчет

2.Расчет р,а j.

3.Расчет Np Fp +Gp и расчет

N

(N

- К-й элемент Р-й

к К строки матрицы N).

; 4. Повторение пп. - 1-3 для К,1,2

5. Повторение пп. 1-4 для ,

М/2-1.

Матрица А в частности может быть матрицей вращения.

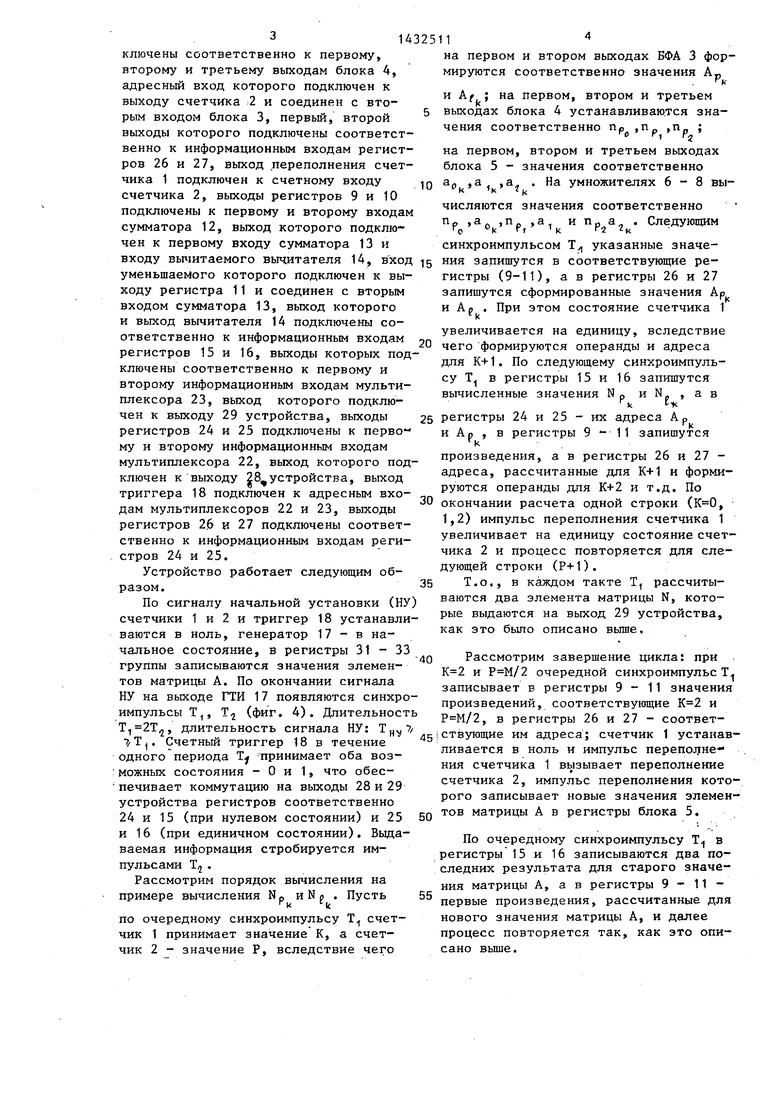

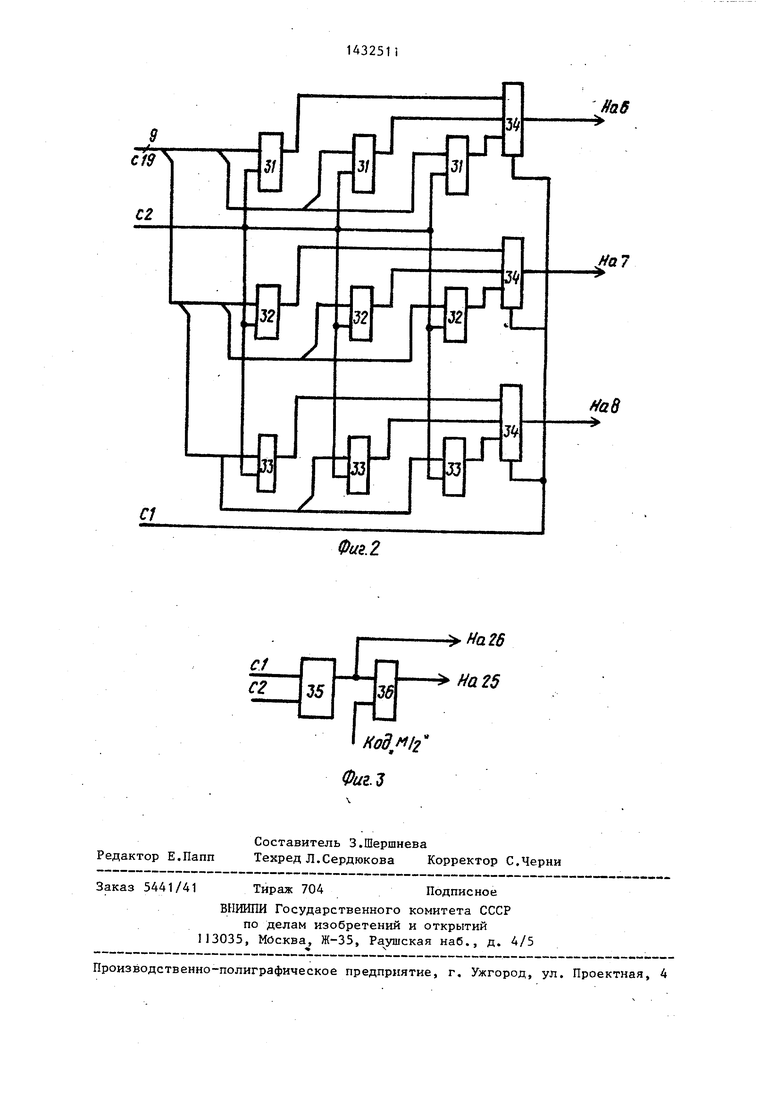

На фиг. 1 представлена функциональная схема устройства; на фиг.2 - пример реализации бл .ка запоминания матрицы А; на фиг. 3 - пример реализации блока формирования адреса.

Устройство содержит счетчик 1 по модулю три, счетчик 2 по модулю М/2, блок 3 формирования адреса (БФА), блок 4 памяти матрицы п, блок 5 запо- минания матрицы А, умножители 6-8, регистры 9-11, сумматоры 12 и 13, вы- читатель 14, регистры 15 и 16, генератор 17 тактовых импульсов (ГТИ), счетный триггер 18, группу 19 инфор40

В регистрах 31-33 групп записаны значения элементов матрицы А, поступающие с группы 19 входов устройства. При этом в регистрах 31 группы записаны элементы первой строки мат- . рицы А, в регистрах 32 и 33 - соответ- ветственно элементы второй и третьей 35 строк, т.е. в каждом такте Т на выходах мультиплексоров 34 группы находятся значения а., . а и а, . k 1)4 «k

Выход Т генератора 17 подключен к счетному входу счетчика 1, синхро- входам регистров 9,10,11,15,16,24-27, выход Т генератора 17 подключен к

счетному входу триггера 12 и выходу 21 устройства, вход 20 устройства подключен к входам начальной установки генератора 17, триггера 18, счетчиков 1 и 2 и к первому входу элемента ИЛИ 30, второй вход которого подключен к выходу переполнения счетчика 2, выход счетчика 1 подключен к , первому входу БФА 3 и к адресному входу блока 5, группа информационных входов которого подключена к группе 19 входов устройства, выход элемента 30 подключен к входу стробирования записи блока 5, первый, второй и третий выходы которого подключены соответственно к первым входам умножите- . лей 6-8, вторые входы которых пои45

50

55

мационных входов устройства, вход 20 начальной установки устройства, выход

21строба устройства, мультиплексоры

22и 23, регистры 24 - 27, адресный выход 28 устройства, 1информационный выход 29 устройства, элемент ИПИ 30. Блок 5 содержит группы регистров 31 - 33 и группу мультиплексоров 34. Блок 3 содержит блок 35 памяти и сумматор 36. На адресньй вход блока 4 поступает значение Р с выхода счетчика 2, при этом на первый, второй, третий выходы блока 4 выдаются соответствен значения п

Р..,

и п

РГ

Блок 35

памяти БФА 3 адресуется значениями Р и К со счетчиков соответственно 2 и 1. При этом на выход блока 35 выдается

значение Ар ЗР+К, которое поступает ц

на первый выход БФА 3 и является адресом записи NO (т.е. номером этого

элемента в матрице N); на второй вы т.л

+1,5 М, которое является адресом записи N

е,

на первом и втором выходах БФА 3 формируются соответственно значения А„

и Af ; на первом, втором и третьем выходах блока 4 устанавливаются значения соответственно

РО

Пр

1 rj

ключены соответственно к первому, второму и третьему выходам блока А, адресньш вход которого подключен к выходу счетчика 2 и соединен с вторым входом блока 3, первый, второй выходы которого подключены соответственно к информационным входам регистров 26 и 27, выход .переполнения счетчика 1 подключен к счетному входу счетчика 2, выходы регистров 9 и 10 подключены к первому и второму входам сумматора 12, выход которого подключен к первому входу сумматора 13 и

входу вычитаемого вычитателя 14, вход 5 ия запишутся в соответствующие ре- уменьшаемого которого подключен к вы- гистры (9-11), а в регистры 26 и 27 ходу регистра 11 и соединен с вторым запишутся сформированные значения Ар входом сумматора 13, выход которого

10

на первом, втором и третьем выходах блока 5 - значения соответственно а ,а ,а . На умножителях 6-8 вычисляются значения соответственно

Следующим

.

Р,

и Пр а .

к Г2 ц

синхроимпульсом Т, указанные значеи А,

При этом состояние счетчика 1

U32511

на первом и втором выходах БФА 3 формируются соответственно значения А„

тттами Af ; на первом, втором и третьем выходах блока 4 устанавливаются значения соответственно

РО

Пр

1 rj

на первом, втором и третьем выходах блока 5 - значения соответственно а ,а ,а . На умножителях 6-8 вычисляются значения соответственно

Следующим

.

Р,

и Пр а .

к Г2 ц

ия запишутся в соответствующие ре- гистры (9-11), а в регистры 26 и 27 запишутся сформированные значения Ар

синхроимпульсом Т, указанные значе ия запишутся в соответствующие ре- гистры (9-11), а в регистры 26 и 27 запишутся сформированные значения Ар

и А,

При этом состояние счетчика 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439618A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1425706A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ТЕЛЕВИЗИОННОГО ИЗОБРАЖЕНИЯ С ИЗМЕНЕНИЕМ МАСШТАБА УПРАВЛЯЕМОГО ФРАГМЕНТА | 1993 |

|

RU2065206C1 |

| Устройство для вычисления скользящего спектра | 1986 |

|

SU1363240A1 |

| СПОСОБ И УСТРОЙСТВО РАСПОЗНАВАНИЯ КЛАССОВ СИГНАЛОВ | 1998 |

|

RU2133501C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Многофункциональный генератор двоичных последовательностей | 1981 |

|

SU991397A1 |

| Программируемая линия задержки | 1986 |

|

SU1406753A1 |

| Цифровой генератор | 1986 |

|

SU1347164A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных процессорах для преобразования координат группы осесимметричных векторов. Цель 19 изобретения - повьпаение быстродействия и расширение класса решаемых задач за счет преобразования группы векторов. Устройство содержит счетчики 1 и 2 по модулю три и М/2, блок 3 формирования адреса, блок 4 памяти матрицы п, блок 5 запоминания матрицы А, умножители 6-8, регистры 9-11, сумматоры 12,13, вычитатель 14, регистры 15,16,24-27, генератор 17 так- товых импульсов, счетньй триггер 18, группу 19 информационных входов уст- ройства, вход 20 начальнойг установки, выход 21 стробирования, мультиплексоры 22,23 адресный выход 28, информационный выход 29, элемент ИЛИ 30. § 3 ил. сл (Г Од tvd СЛ

и выход вычитателя 14 подключены соответственно к информационным входам регистров 15 и 16, выходы которых подключены соответственно к первому и второму информационным входам мультиплексора 23, выход которого подключен к выходу 29 устройства, выходы регистров 24 и 25 подключены к перво му и второму информационным входам мультиплексора 22, выход которого подключен к выходу 28 устройства, выход триггера 18 подключен к адресным входам мультиплексоров 22 и 23, выходы регистров 26 и 27 подключены соответственно к информационным входам реги- стров 24 и 25.

Устройство работает следующим образом.

По сигналу начальной установки (НУ) счетчики 1 и 2 и триггер 18 устанавливаются в ноль, генератор 17 - в начальное состояние, в регистры 31-33 группы записываются значения элементов матрицы А. По окончании сигнала НУ на выходе ГТИ 17 появляются синхроимпульсы Т,, Tj (фиг. 4). Длительность Т т

-I ) iJ-,2

увеличивается на единицу, вследствие 20 чего формируются операнды и адреса для К+1. По следующему синхроимпульсу Т в регистры 15 и 16 запишутся

вычисленные значения N

и N ,

t-K

а в

25 регистры 24 и 25 - их адреса А р

и Ар , в регистры 9 - 11 запишутся

1 произведения, а в регистры 26 и 27 адреса, рассчитанные для К+1 и формируются операнды для К+2 и т.д. По

30 окончании расчета одной строки (, 1,2) импульс переполнения счетчика 1 увеличивает на единицу состояние счетчика 2 и процесс повторяется для следующей строки (Р+1).

35 Т.о., в каждом такте Т рассчитываются два элемента матрицы N, которые выдаются на выход 29 устройства, как это было описано вьппе.

-40 Рассмотрим завершение цикла: при и очередной синхроимпульс Т записывает в регистры 9-11 значения произведений, соответствующие и , в регистры 26 и 27 - соответдлительность сигнала НУ: Т„.,7/ :ствующие им адреса; счетчик 1 устанав- ,. Счетный триггер 18 в течение ча: - fливается в ноль и импульс nepenojjHe

ния счетчика 1 вызывает переполнение счетчика 2, импульс переполнения которого записывает новые значения элементов матрицы А в регистры блока 5.

одного периода Т принимает оба воз- :можных состояния - О и 1, что обес- печивает коммутацию на выходы 28 и 29 устройства регистров соответственно 24 и 15 (при нулевом состоянии) и 25 и 16 (при единичном состоянии). Вьща- ваемая информация стробируется импульсами Т .

Рассмотрим порядок вычисления на примере вычисления N,, иЫл . Пусть

Гц |

по очередному синхроимпульсу Т., счетчик 1 принимает значение К, а счетчик 2 - значение Р, вследствие чего

50

55

По очередному синхроимпульсу Т в регистры 15 и 16 записываются два последних результата для старого значения матрицы А, а в регистры 9-11- первые произведения, рассчитанные для нового значения матрицы А, и далее процесс повторяется так, как это описано Bbmje.

увеличивается на единицу, вследствие чего формируются операнды и адреса для К+1. По следующему синхроимпульсу Т в регистры 15 и 16 запишутся

вычисленные значения N

и N ,

t-K

а в

25 регистры 24 и 25 - их адреса А р

и Ар , в регистры 9 - 11 запишутся

1 произведения, а в регистры 26 и 27 адреса, рассчитанные для К+1 и формируются операнды для К+2 и т.д. По

30 окончании расчета одной строки (, 1,2) импульс переполнения счетчика 1 увеличивает на единицу состояние счетчика 2 и процесс повторяется для следующей строки (Р+1).

35 Т.о., в каждом такте Т рассчитываются два элемента матрицы N, которые выдаются на выход 29 устройства, как это было описано вьппе.

-40 Рассмотрим завершение цикла: при и очередной синхроимпульс Т записывает в регистры 9-11 значения произведений, соответствующие и , в регистры 26 и 27 - соответ :ствующие им адреса; счетчик 1 устанав ча: 50

55

По очередному синхроимпульсу Т в регистры 15 и 16 записываются два последних результата для старого значения матрицы А, а в регистры 9-11- первые произведения, рассчитанные для нового значения матрицы А, и далее процесс повторяется так, как это описано Bbmje.

Формула изобретен.ия

Вычислительное устройство, содер- жцщее четьфе регистра, два сумматора, один вычитатель и два мультиплексора, причем выход первого регистра подклю™ гн к входу первого операнда первого мматора, выход которого подключен к

м;

соду первого операнда второго сум- ю iTopa, отличающееся тем,

что, с целью повьппения быстродействия и расширения класса решаемых задач за счет преобразования группы векто

эв, Б него введены два счетчика, блок формиропания адреса, блок памя- T:I матрицы п., блок запоминания матрица, А, три умножителя, пять регистров, г.шератор тактовых импульсов, счетный триггер и элемент ИЛИ, причем первый генератора тактовых импульсов пэдключен к счетному входу первого счетчика и синхровходам регистров с

зрвого по девятый, вход начальной

:тановки устройства подключен к вхо- д,1м начальной установки генератора

1КТОВЫХ импульсовJ первого и второго счетчиков, счетного триггера и к перэму входу элемента ИЛИ, выход которого подключен к входу стробирования записи блока запоминания матрицы А, П(грвый, второй и третий выходы которого подключены к входам первых со- М:Южителей умножителей с первого по т;)етий, входы вторых сомножителей которых подключены соответственно к первому, второму и третьему выходам блока памяти матрицы, п, адресный вход которого подключен к выходу счетчика пЬ модулю М/2 и соединен с вторым в}содом блока формирования адреса, п0раый вход которого подключен к вы- ходу первого счетчика и соединен с

5

0

5

0

5

0

адресным входом блока запоминания матрицы А, группа информационных входов которого подключена к i-pynne ин-- формационных входов устройства, выход переполнения первого счетчика подключен к счетному входу второго счетчика, выход переполнения которого подключен к второму входу элемента ИЛИ, второй выход генератора тактовых импульсов подключен к выходу строба устройства и синхровходу счетного триггера, выход которого подключен к адресным входам первого и второго мультиплексоров, выходы которых подключены соответственно к адресному и информационному выходам устройства, первый и вт.орой выходы блока формирования адреса подключены соответственно к информационным входам четвертого и пятого регистров, выходы которых подключены соответственно к информационным входам шестого и седьмого регистров, выходы которых подключены соответственно к первому и второму информационным входам первого мультиплексора, выходы первого, второго и третьего умножителей подключены соответственно к информационным входам первого, третьего и второго регистров, выход третьего регистра подключен к второму входу первого суммато- ра, выход которого подключен к входу . вычитаемого вычитателя, вход уменьшаемого вычитателя соединен с вторым входом второго сумматора и подключен к выходу второго регистра, выходы второго сумматора и вычитателя подключ.е- ны соответственно к информационным входам восьмого и девятого регистров, выходы которых подключены соответственно к первому и второму информационным входам второго мультиплексора.

1

j/

г/г2

l f

J/

LJl

3«

1L

/fetf

3if

g

A O

rul

л

IL

/iaB

-

| Вычислительное устройство для поворота вектора | 1982 |

|

SU1109742A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Вычислительное устройство | 1981 |

|

SU959071A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-10-23—Публикация

1987-03-23—Подача