(21)4231127/24-24

(22)23.03.87

(46) 23.09.88. Бюл. № 35

(71)Московский инженерно-физический институт

(72)М.Ю. Силин

(53)681.325(088.8)

(56)ЭВМ и системы/Справочник по цифровой вычислительной технике. - Киев, 1980, с. 62, рис. 2.36.

Авторское свидетельство СССР № 1226484, кл. G 06 F 15/31, 1984.

(54)УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ МАТРИ- ЦЬ1 ФУНКЦИЙ

(57)Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных системах. Целью изобретения является расширение класса решаемых задач. Устройство содержит счетчик 1 по модулю М, счетчик 2 по модулю М,, счетчик 3 по модулю М.,триггеры 4,. 5, генератор 6 тактовых импульсов, блок 7 микропрограммного управления, блоки 8,9 и 10 формирования адреса, блоки 11-14 памяти, мультиплексоры 15-20, регистры 21-28, умножитель 29, сумматор 30, формирователи 31, 32, 33 импульсов, элемент И 34, демулыиплек- сор 35. Поставленная цель достигается за счет вычисления матрицы Т функций

.-

ПрАг,р,

причем выборка векторов s

с

осуществляется по специальным алгоритмам. 7 ил. 1 табл.

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439618A1 |

| Вычислительное устройство | 1987 |

|

SU1432511A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Устройство для формирования широкополосного случайного процесса | 1986 |

|

SU1432514A1 |

| Микропрограммный процессор | 1984 |

|

SU1211746A1 |

| Микропрограммное устройство сопряжения | 1989 |

|

SU1700560A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Микропрограммный модуль | 1986 |

|

SU1427366A1 |

| Функциональный преобразователь многих переменных | 1990 |

|

SU1742836A1 |

ла Л

J7

SS

ел

О5

Фиг.

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных системах.

Целью изобретения является расширение класса решаемых задач за счет возможности вычисления матрицы Т функции п , где вектор , необходимый для вычисления К-го элемента Р-й строки матрицы Т, выбирается по определенному алгоритму как функция Р и К.

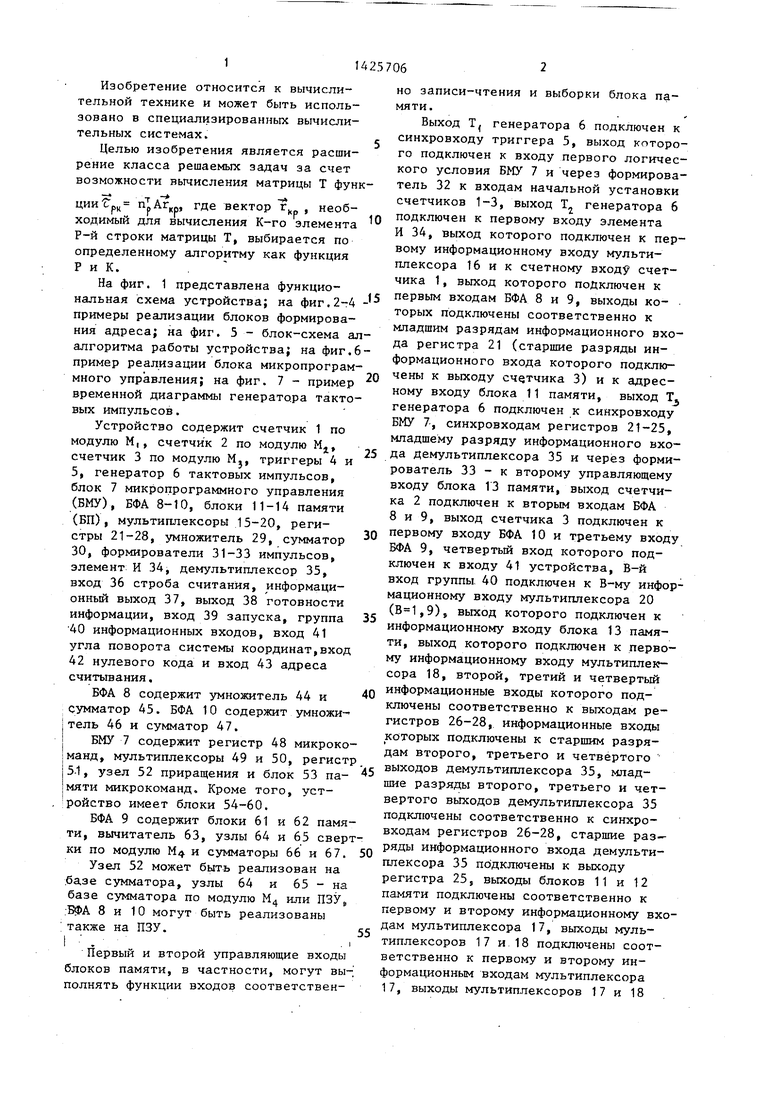

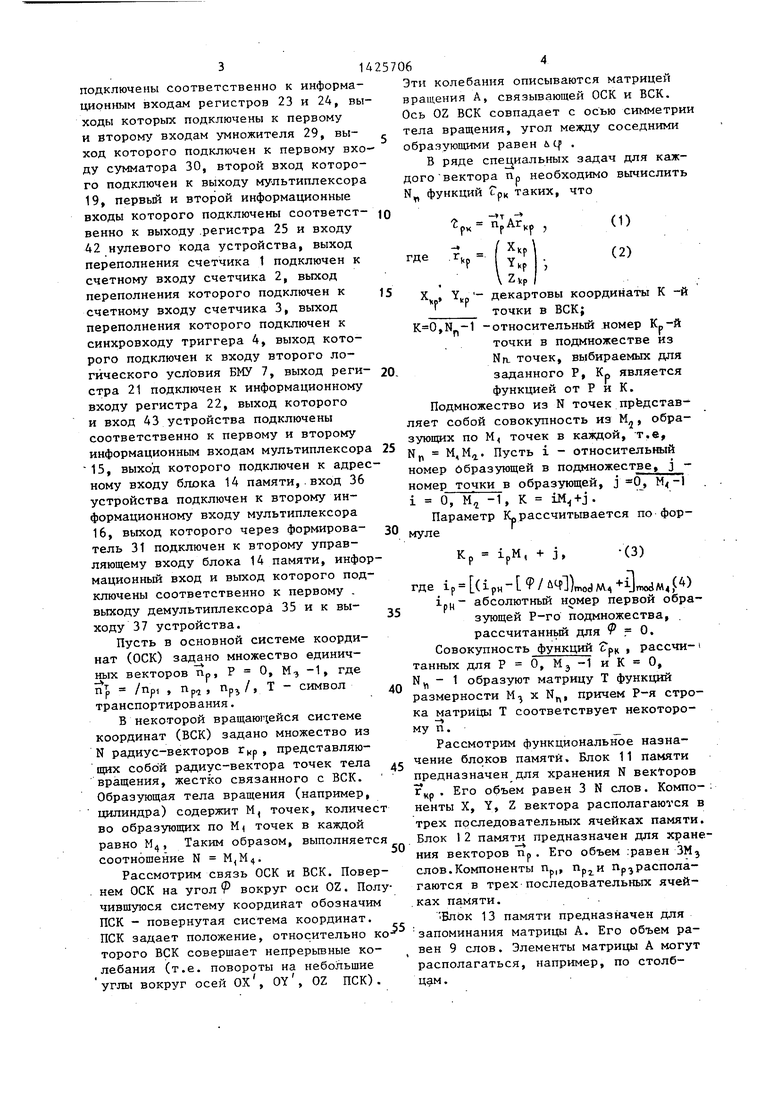

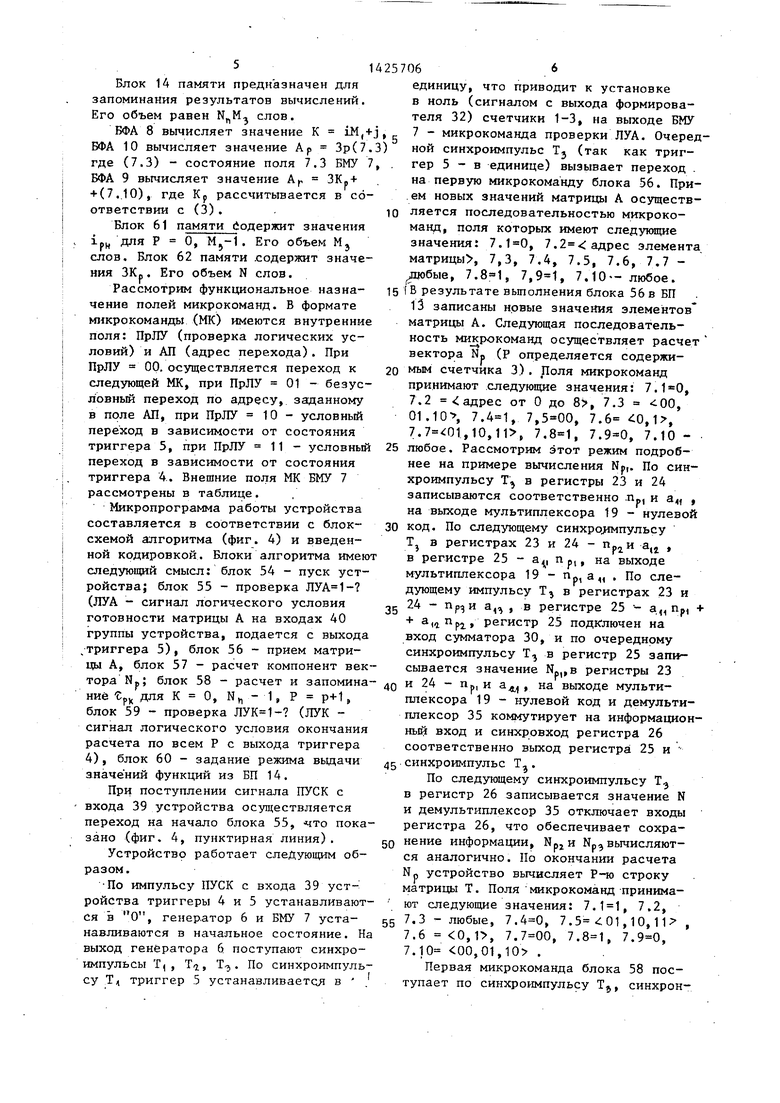

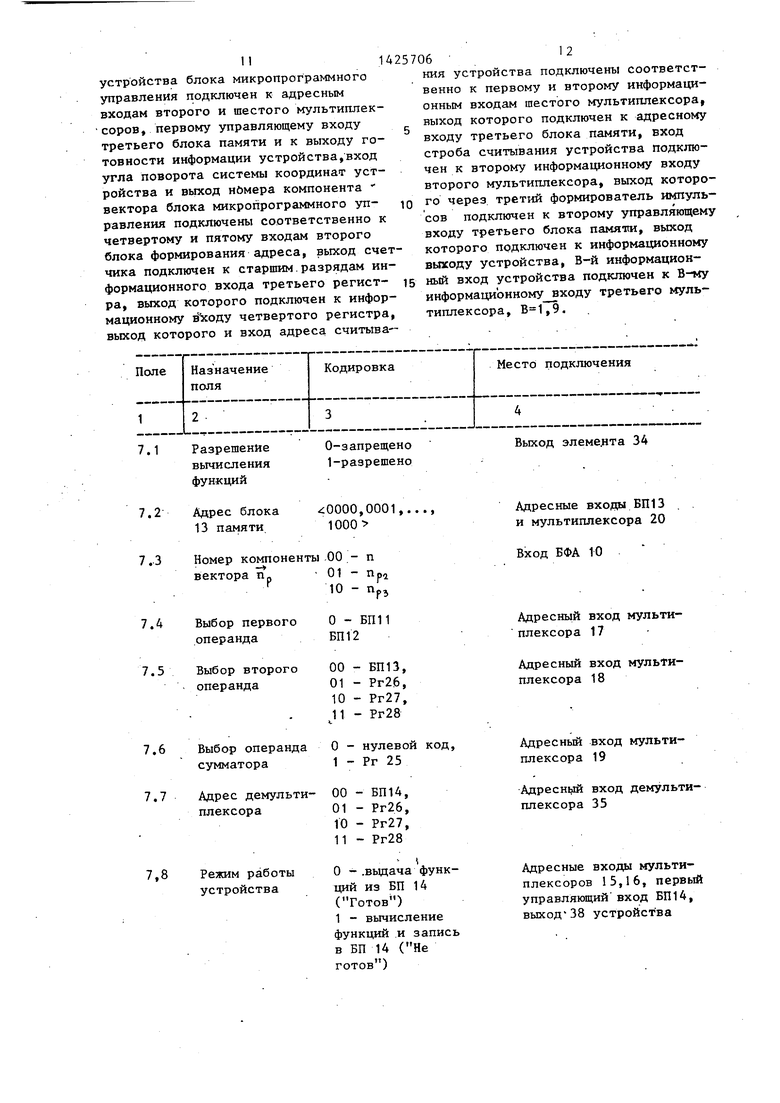

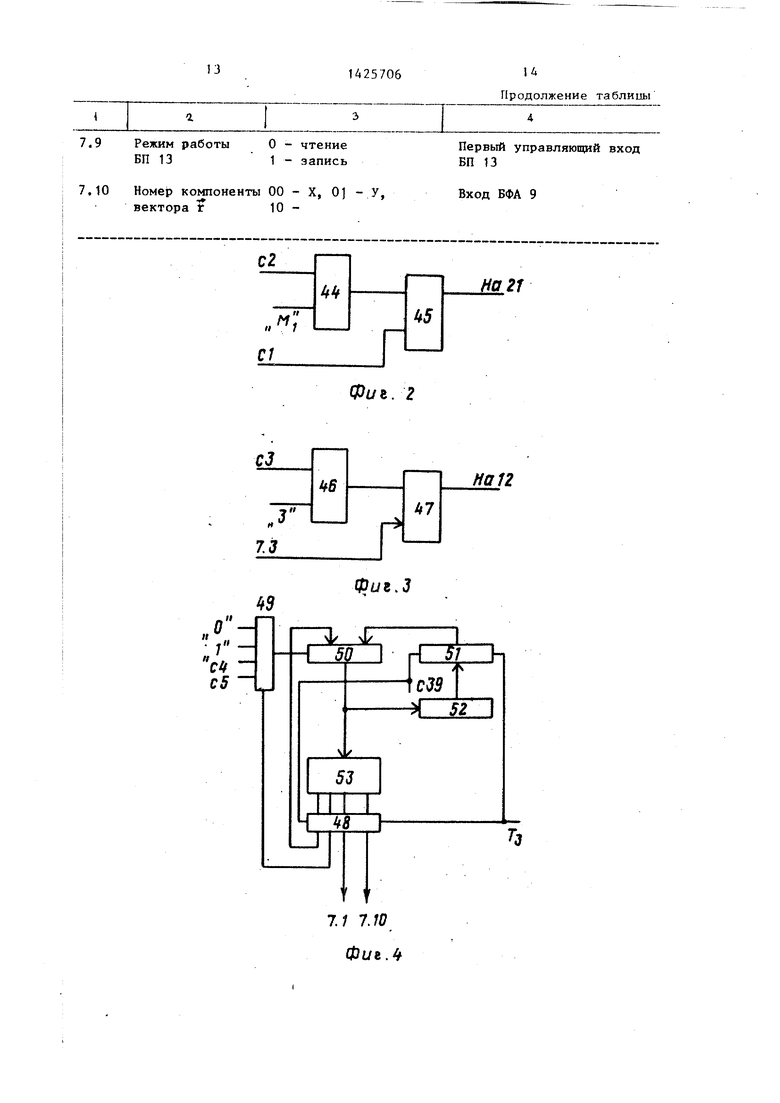

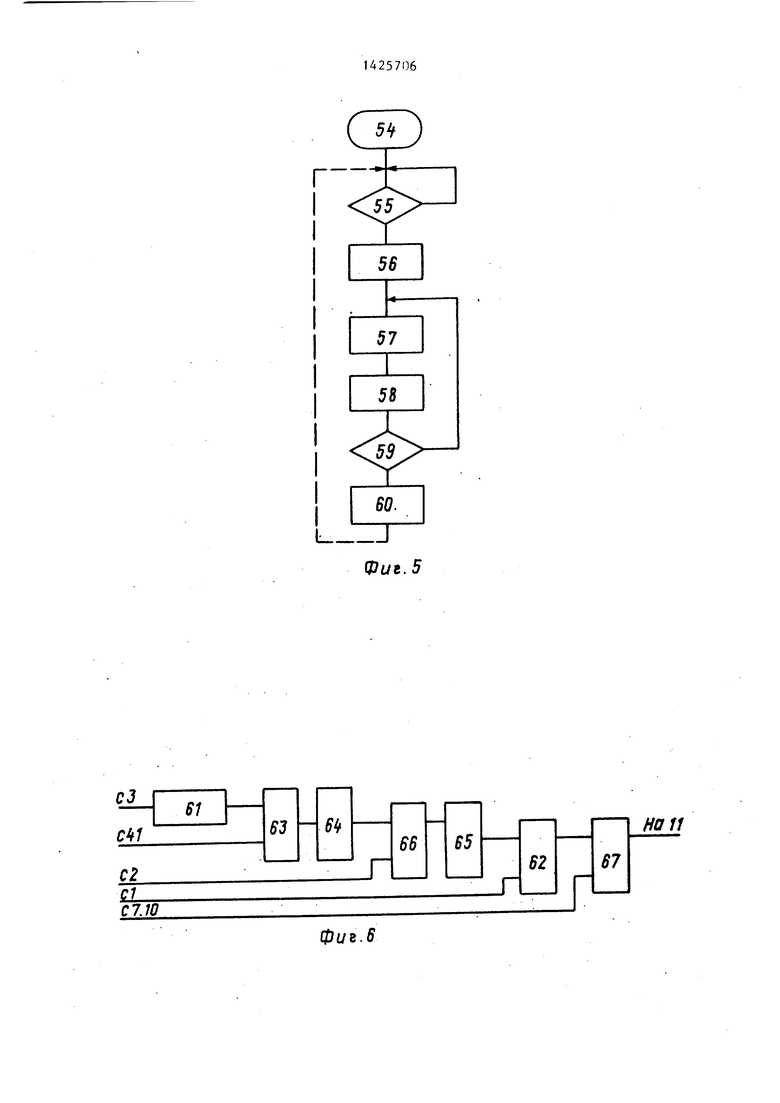

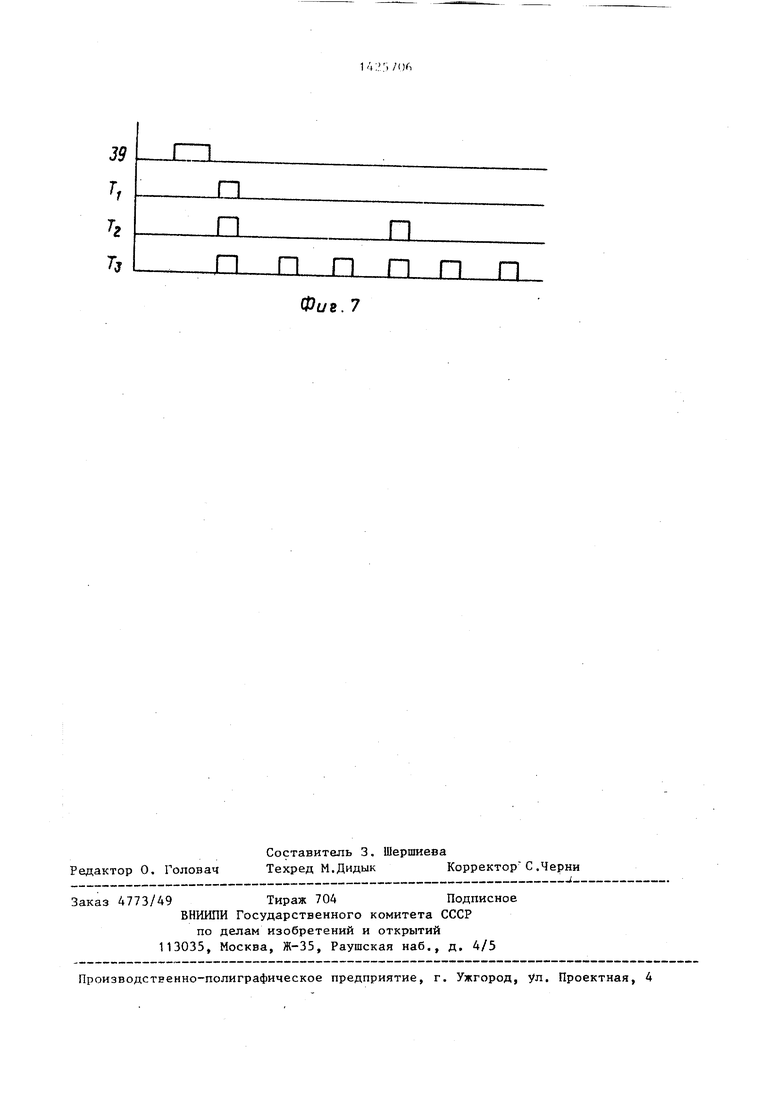

На фиг. 1 представлена функциональная схема устройства; на фиг.2-4 примеры реализации блоков формирования адреса; на фиг. 5 - блок-схема ал алгоритма работы устройства; на фиг.6 пример реализации блока микропрограммного управления; на фиг. 7 - пример временной диаграммы генератора тактовых импульсов.

Устройство содержит счетчик 1 по модулю М|, счетчик 2 по модулю Mj, счетчик 3 по модулю Mj, триггеры 4 и 5, генератор 6 тактовых импульсов, блок 7 микропрограммного управления (БМУ), БФА 8-10, блоки 11-14 памяти (БП), мультиплексоры 15-20, регистры 21-28, умножитель 29, сумматор 30, формирователи 31-33 импульсов, элемент И 34, демультиплексор 35, вход 36 строба считания, информаци- онньм выход 37, выход 38 готовности информации, вход 39 запуска, группа 40 информационных входов, вход 41 угла поворота системы координат,вход 42 нулевого кода и вход 43 адреса считывания.

БФА 8 содержит умножитель 44 и сумматор 45. БФА 10 содержит умножи- Iтель 46 и сумматор 47. I БМУ 7 содержит регистр 48 микроко манд, мультиплексоры 49 и 50, регист 5-1, узел 52 приращения и блок 53 па- |мяти микрокоманд. Кроме того, уст- ройство имеет блоки 54-60.

БФА 9 содержит блоки 61 и 62 памяти, вычитатель 63, узлы 64 и 65 сверки по модулю М и сумматоры 66 и 67.

Узел 52 может быть реализован на .базе сумматора, узлы 64 и 65 - на базе сумматора по модулю Н или ПЗУ,, .БФА 8 и 10 могут быть реализованы также на ПЗУ.,

I .

Первый и второй управляющие входы

блоков памяти, в частности, могут вы полнять функции входов соответственно записи-чтения и выборки блока памяти.

Выход Tj генератора 6 подключен к синхровходу триггера 5, выход которого подключен к входу первого логического условия БМУ 7 и через формирователь 32 к входам начальной установки счетчиков 1-3, выход Т генератора 6 подключен к первому входу элемента И 34, выход которого подключен к первому информационному входу мультиплексора 16 и к счетному входу счетчика 1, выход которого подключен к первым входам БФА 8 и 9, выходы ко- торых подключены соответственно к младшим разрядам информационного входа регистра 21 (старшие разряды информационного входа которого подключены к выходу счетчика 3) и к адресному входу блока 11 памяти, выход Tj генератора 6 подключен к синхровходу БМУ 7, синхровходам регистров 21-25, младшему разряду информационного входа демультиплексора 35 и через формирователь 33 - к второму управляющему входу блока 13 памяти, выход счетчика 2 подключен к вторым входам БФА 8 и 9, выход счетчика 3 подключен к первому входу БФА 10 и третьему входу БФА 9, четвертьй вход которого подключен к входу 41 устройства, В-й вход группы, 40 подключен к В-му информационному входу мультиплексора 20 (,9), выход которого подключен к информационному входу блока 13 памяти, выход которого подключен к первому информационному входу мультиплексора 18, второй, третий и четвертый информационные входы которого подключены соответственно к выходам регистров 26-28, информационные входы которых подключены к старшим разрядам второго, третьего и четвертого выходов демультиплексора 35, младшие разряды второго, третьего и четвертого выходов демультиплексора 35 подключены соответственно к синхровходам регистров 26-28, старпше разряды информационного входа демультиплексора 35 подключены к выходу регистра 25, вьпсоды блоков 11 и 12 памяти подключены соответственно к первому и второму информационному входам мультиплексора 17, выходы мультиплексоров 17 и 18 подключены соответственно к первому и второму информационным входам мультиплексора 17, выходы мультиплексоров 17 и 18

подключены соответственно к информационным входам регистров 23 и 24, выходы которых подключены к первому и второму входам умножителя 29, выход которого подключен к первому входу сумматора 30, второй вход которого подключен к выходу мультиплексора 19, первый и второй информационные входы которого подключены соответственно к выходу .регистра 25 и входу 42 нулевого кода устройства, выход переполнения счетчика 1 подключен к счетному входу счетчика 2, выход переполнения которого подключен к счетному входу счетчика 3, выход переполнения которого подключен к синхровходу триггера 4, выход которого подключен к входу второго логического услЪвия БМУ 7, выход регистра 21 подключен к информационному входу регистра 22, выход которого и вход 43 устройства подключены соответственно к первому и второму информационным входам мультиплексора 15, выход которого подключен к адресному входу блока 14 памяти,.вход 36 устройства подключен к второму информационному входу мультиплексора 16, выход которого через формирователь 31 подключен к второму управляющему входу блока 14 памяти, информационный вход и выход которого подключены соответственно к первому . выходу демультиплексора 35 и к выходу 37 устройства.

Пусть в основной системе координат (ОСК) задано множество единичных векторов Пр, Р О, М, -1, где

п

/Пр

pi t f i Чр5

/.Т символ

транспортирования.

В некоторой вращаюр;ейся системе координат (век) задано множество из N радиус-векторов , представляющих собо й радиус-вектора точек тела д вращения, жестко связанного с ВеК. Образующая тела вращения (например, цилиндра) содержит М, точек, количест во образующих по М) точек в каждой равно М, Таким образом, выполняется соотношение N М,М4.

Рассмотрим связь ОеК и ВеК. Повернем ОеК на угол вокруг оси OZ. Полу чившуюся систему коордийат обозначим пек - повернутая система координат.

50

Совокупность функций S pn , рассчитанных для ,Мз-1иК 0, N - 1 образуют матрицу Т функций размерности М х N, причем Р-я строка матрицы Т соответствует некоторому п.

Рассмотрим функциональное назначение блоков памяти. Блок 11 памяти предназначен для хранения N векторов . Его объем равен 3 N слов. Компоненты X, Y, Z вектора располагаются в трех последовательных ячейках памяти Блок 12 памяти предназначен для хране ния векторов Пр . Его объем :равен ЗМ слов.Компоненты Пр,располагаются в трех последовательных ячейках памяти.

Блок 13 памяти предназначен для

пек задает положение, относительно ко- запоминания матрицы А. Его объем раторого век совершает непрерьгоные колебания (т.е. повороты на небольшие

OZ пек).

повороты на углы вокруг осей ОХ , OY

Эти колебания описываются матрицей вращения А, связывающей ОеК и ВеК. Ось OZ век совпадает с осью симметри тела вращения, угол между соседними образующими равен & Cf .

В ряде специальных задач для каждого вектора Пр необходимо вычислить

... /

N.

функций срц таких, что

где

(1) (2)

X

Т

декартовы координаты К -и

точки в ВСК;

, -относительный номер К--и точки в подмножестве из Nn. точек, выбираемых для заданного Р, Кр является функцией от Р и К. Подмножество из N точек представляет собой совокупность из М-, образующих по М, точек в каждой, т.е, NP М, М. Пусть i - относительный номер образующей в подмножеств е, j - номер точки в образующей, j 0, N4 -1 i О, М -1, К .

Параметр К-рассчитывается по формуле

5

0

0

К,

ipM,

(3)

р ( J

(1рн- 9/йч1)„,(:4)

1рц- абсолютный номер первой образующей Р-го подмножества, рассчитанньй для f 0.

Совокупность функций S pn , рассчиI танных для ,Мз-1иК 0, N - 1 образуют матрицу Т функций размерности М х N, причем Р-я строка матрицы Т соответствует некоторому п.

Рассмотрим функциональное назначение блоков памяти. Блок 11 памяти предназначен для хранения N векторов . Его объем равен 3 N слов. Компо ; ненты X, Y, Z вектора располагаются в трех последовательных ячейках памяти. Блок 12 памяти предназначен для хранения векторов Пр . Его объем :равен ЗМ слов.Компоненты Пр,располагаются в трех последовательных ячейках памяти.

Блок 13 памяти предназначен для

вен 9 слов. Элементы матрицы А могут располагаться, например, по столбцам .

5U25706.6

Блок 14 памяти предназначен для единицу, что приводит к установке

запоминания результатов вычислений. в ноль (сигналом с выхода формироваЕго объем равен слов.теля 32) счетчики 1-3, на выходе БМУ

БФА 8 вычисляет значение К iM,+j, 7 - микрокоманда проверки ЛУА. ОчередБФА 10 вычисляет значение Ар Зр(7.3)

где (7.3) - состояние поля 7.3 БМУ 7, .

БФА 9 вычисляет значение А, ЗКр +

+ (7..10), где Кр рассчитывается в соответствии с (3) .

Блок 61 памяти Содержит значения 1рц для Р О, Mj-1 . Его объем Mj слов. Блок 62 памяти .содержит значения ЗКр. Его объем N слов.

Рассмотрим функциональное назначение полей микрокоманд. В формате микрокоманды (МК) имеются внутренние поля: ПрЛУ (проверка логических условий) и АЛ (адрес перехода). При ПрЛУ 00. осуществляется переход к следующей МК, при ПрЛУ 01 - безусловный переход по адресу, заданному в поле АЛ, при ПрЛУ 10 - условный переход в зависимости от состояния

ной синхроимпульс Tj (так как триггер 5 - в единице) вызывает переход . на первую микрокоманду блока 56. Прием новых значений матрицы А осуществ10 ляется последовательностью микрокоманд, поля которых имеют следующие значения: 7., 7.2 : адрес элемента матрицы, 7,3, 7.4, 7.5, 7.6, 7.7 - сюбые, 7., 7,, 7.10-- любое.

15 (В результате выполнения блока 56в БП 13 записаны новые значения элементов матрицы А. Следующая последовательность мидрокоманд осуществляет расчет вектора N (Р определяется содержи20 мым счетчика 3). Поля микрокоманд принимают следующие значения: 7., 7.2 адрес от О до 8, 7.3 :00, 01.10, 7., 7,, 7.6 iO,1, 7.,10,11, 7., 7., 7.10 триггера 5, при ПрЛУ 11 - условный 25 любое. Рассмотрим этот режим подробпереход в зависимости от состояния триггера 4. Внешние поля МК БМУ 7 рассмотрены в таблице.

Микропрограмма работы устройства составляется в соответствии с блок- схемой алгоритма (фиг. 4) и введенной кодировкой. Блоки алгоритма имеют следующий смысл: блок 54 - пуск устройства; блок 55 - проверка (ЛУА - сигнал логического условия готовности матрицы А на входах 40 группы устройства, подается с выхода триггера 5), блок 56 - прием матрицы А, блок 57 - расчет компонент вектора N.; блок 58 - расчет и запоминание -Орц для К О, N - 1, Р р+1, блок 59 - проверка (ЛУК - сигнал логического условия окончания расчета по всем Р с выхода триггера 4), блок 60 - задание режима выдачи значений функций из БП 14.

При поступлении сигнала ПУСК с входа 39 устройства осуществляется переход на начало блока 55, ITO показано (фиг. 4, пунктирная линия).

Устройствр работает следующим образом.

По импульсу ПУСК с входа 39 уст- ройства триггеры 4 и 5 устанавливаются в О, генератор 6 и БМУ 7 устанавливаются в начальное состояние. На выход генератора 6 поступают синхроимпульсы Т(, Та, Т. По синхроимпульсу T;i триггер 5 устанавливаетсл в

ной синхроимпульс Tj (так как триггер 5 - в единице) вызывает переход . на первую микрокоманду блока 56. Прием новых значений матрицы А осуществляется последовательностью микрокоманд, поля которых имеют следующие значения: 7., 7.2 : адрес элемента матрицы, 7,3, 7.4, 7.5, 7.6, 7.7 - сюбые, 7., 7,, 7.10-- любое.

(В результате выполнения блока 56в БП 13 записаны новые значения элементов матрицы А. Следующая последовательность мидрокоманд осуществляет расчет вектора N (Р определяется содержимым счетчика 3). Поля микрокоманд принимают следующие значения: 7., 7.2 адрес от О до 8, 7.3 :00, 01.10, 7., 7,, 7.6 iO,1, 7.,10,11, 7., 7., 7.10 нее на примере вычисления Np,. По синхроимпульсу Т в регистры 23 и 24 записываются соответственно .Пр, и а, , на выходе мультиплексора 19 - нулевой 0 код. По следующему синхроимпульсу TJ в регистрах 23 и 24 - a,j , в регистре 25 - п р,, на выходе мультиплексора 19 - п-, а„ . По следующему импульсу TJ в регистрах 23 и 24 - а,, , в регистре 25 - а,Пр, +

5

+ а, Hpj, регистр 25 подключен на

вход сумматора 30, и по очередному синхроимпульсу Т в регистр 25 запи сывается значение Np,,B регистры 23

0 И 24 - Пр, и а , на вьпсоде мультиплексора 19 - нулевой код и демульти- плексор 35 коммутирует на информационный вход и синхровход регистра 26 соответственно выход регистра 25 и

5 синхроимпульс Т.

По следующему синхроимпульсу Т в регистр 26 записывается значение N и демультиплексор 35 отключает входы регистра 26, что обеспечивает сохра0 нение информации, Np вычисляются аналогично. По окончании расчета NP устройство вычисляет Р-ю строку матрицы Т. Поля микрокоманд принима- ют следующие значения: 7.1 1, 7.2,

5 7.3 - любые, 7., 7.5 : 01,1 0,11 , 7.,1, 7., 7., 7., 7.10 00,01,10 .

Первая микрокоманда блока 58 поступает по синхроимпульсу Т}, синхрон 1425706 8

ному с Tj. При необходимости это ус- ли расчет для всех Р не окончен, т.е.

ловие легко обеспечивается введением холостых микрокоманд для пропуска такта. Установка поля 7.1 в единицу разрешает прохождение синхроимпульсов Т на счетный вход счетчика 1. Состояние счетчика 1 изменяется циклически от О до , импульс переполнения счетчика 1 поступает на счетный вход счетчика 2, состояние которого изменяется от О до М.-1.При этом поля 7.10 и 7.5 обеспечивают запись в регистры соответственно 23

счетчик 42 не переполнился, то очередная микрокоманда осуществляет пере- ход на начало блока 57 и процесс повторяется для следующего Р аналогично описанному. Если рассчитаны значения всех , М,-1, то импульс переполнения счетчика 3 устанавливает 10 в единицу триггер 4. Очередной синхроимпульс Т, приводит к выполнению микрокоманды, задающей режим вьщачи значений функций из БП 14. Поля микрокоманды, задающей режим вьодачи значений и 24 требуемых в данном такте комдр- 15 функций из БП 14. Поля микрокоманды нент векторов соответственно г, и Np, принимают следующие значени/i: 7.,

демультиплексор 35 коммутирует выход регистра 25 на информационный вход

ВП 14.-Вычисление величин с„цосуществляется аналогично вычислению ком- 20 значение, которое задает режим чтения понент вектора Np. Поэтому рассмотрим

Р подробнее вопрос записи информации

в БП 14.

На первом управляющем входе БП 14

информации, на адресном входе БП 14 - адрес с входа 43 устройства, на вход формирователя 31 поступают импульсы с входа 36 устройства. На выходе 38 установлено значение, задающее работу 25 устройства - логический О, что оз- БП 14 в режиме записи, мультиплексо- начает готовность информации к выда- ров 15 коммутирует на адресный вход че. Указанная микрокоманда выполняет- БП 14 содержимое регистра 22, мульти- ся циклически до поступления сигнала плексор 16 коммутирует на вхрд форми- ПУСК. В этом режиме вычисленные зна- рователя 3t синхроимпульсы с выхода 30 чения могут быть считаны в другие элемента И 34. Адрес записи в БП 14 устройства. При необходимости обнов- формируется на БФА В (младшие разряды) ления матрицы Т на входе 40 устрой- и на счетчике 3 (старшие разряды). ства подается новое значение матри- Регистры 21 и 22 обеспечивают соответ- цы А, а на входе 39 - сигнал ПУСК, ствие адреса записи и записываемого 35 пссле чего устройство работает ана- . значения, формирователь 31 обеспечи- логично описанному. вает задержку синхроимпульса, посту- | пающего на второй управляющий вход БП 14, необходимую для правильной записи информации.

Таким образом, осуществляется выФормула изобретения

40

Устройство для вычисления матрицы функций, содержащее два триггера, четыре регистра, умножитель, сумматор, первый мультиплексор, причем выход первого мультиплексора подключен

числение и записи с., для

Устройство для вычисления матрицы функций, содержащее два триггера, четыре регистра, умножитель, сумматор, первый мультиплексор, причем выход первого мультиплексора подключен

всех , М,.

Очередной синхроимпульс Т вызывает переполнение счетчика 2, импульс 45 к ;нформационному входу пёрвого репереполнения которого увеличивает на

единицу состояние счетчика 3 (при этом

счетчики 1 и 2 устанавливаются в ноль) .

Синхроимпульс т,, совпадающий с Т, операнда сумматора, выход которого

устанавливает поле 7.1 в ноль, что за-во подключен к информационному входу

прещает прохоадение синхроимпульсов - регистра, отличаюTj, на счетный вход счетчика 1 . При щ е е с я тем, что, с целью расширегистра, выход которого подключен к первому входу умножителя, выход которого подключен к входу первого

этом в регистры 23, 24 и 21 записаны соответственно операнды и адрес записи последнего результата рк кото- 55 рый записывается в БП 14 по сигналу с выхода формирователя 31, запущенного последним синхроимпульсом Tg, поступающим с выхода элемента И 34. Есния класса решаемых задач за счет возможности вычисления матрицы Т функций

рк

-I

Til Ar,

ср

,, где вектор

Гкр

необходимый для вычисления К-го элемента Р-й строки матрицы Т, выбирается по определенному, алгоритму как

ли расчет для всех Р не окончен, т.е.

счетчик 42 не переполнился, то очередная микрокоманда осуществляет пере- ход на начало блока 57 и процесс повторяется для следующего Р аналогично описанному. Если рассчитаны значения всех , М,-1, то импульс переполнения счетчика 3 устанавливает в единицу триггер 4. Очередной синхроимпульс Т, приводит к выполнению микинформации, на адресном входе БП 14 - адрес с входа 43 устройства, на вход формирователя 31 поступают импульсы с входа 36 устройства. На выходе 38 устройства - логический О, что оз- начает готовность информации к выда- че. Указанная микрокоманда выполняет- ся циклически до поступления сигнала ПУСК. В этом режиме вычисленные зна- чения могут быть считаны в другие устройства. При необходимости обнов- ления матрицы Т на входе 40 устрой- ства подается новое значение матри- цы А, а на входе 39 - сигнал ПУСК, пссле чего устройство работает ана- логично описанному. |

Формула изобретения

информации, на адресном входе БП 14 адрес с входа 43 устройства, на вход формирователя 31 поступают импульсы с входа 36 устройства. На выходе 38 25 устройства - логический О, что оз- начает готовность информации к выда- че. Указанная микрокоманда выполняет ся циклически до поступления сигнала ПУСК. В этом режиме вычисленные зна- 30 чения могут быть считаны в другие устройства. При необходимости обнов- ления матрицы Т на входе 40 устрой- ства подается новое значение матри- цы А, а на входе 39 - сигнал ПУСК, 35 пссле чего устройство работает ана- логично описанному. |

40

Устройство для вычисления матрицы функций, содержащее два триггера, четыре регистра, умножитель, сумматор, первый мультиплексор, причем выход первого мультиплексора подключен

45 к ;нформационному входу пёрвого реоперанда сумматора, выход которого

гистра, выход которого подключен к первому входу умножителя, выход которого подключен к входу первого

ния класса решаемых задач за счет возможности вычисления матрицы Т фун

рк

-I

Til Ar,

ср

,, где вектор

Гкр

димый для вычисления К-го элеР-й строки матрицы Т, выбираетопределенному, алгоритму как

функция Р и к, в него введены три счетчика, генератор тактовых импульсов, блок микропрограммного управления, три блока формирования адреса, четыре блока памяти, пять мультиплексоров, четыре регистра,три формиро- : вателя т-тулъсов, элемент И и демуль- i типлексор, причем вход запуска уст- I ройства подключен к входам установки в О первого и второго триггеров, входам начальной установки генератора тактовых импульсов и блока микро- ; программного управления, первый выход I генератора тактовых импульсов под- I кпючен к синхровходу второго тригге- ; ра, выход которого подключен к входу :первого логического условия блока I микропрограммного управления и через ; первый, формирователь импульсов к вхо- ;дам начальной установки счетчиков с первого по третий, -информационные ;входы первого и второго триггеров : подключены к входу логической едини1цы ; уст ройства, выход переполнения перво- го счетчика подключен к синхровходу ;перйого триггера, выход которого под- Iключен к входу второго логического I условия блока микропрограммного управ |ления, второй выход генератора такто- вых импульсов подключен к первому входу элемента И, выход которого под- I ключен к первому информационному вход I второго мультиплексора и к cчeтнo ry входу второго счетчика, выход которог Iподключен к первым входам первого и JBTOporo блоков формирования адреса, 1выходы которых подключены соответст- венно к младшим разрядам информацион- ного входа третьего регистра и к ад- ipecHOMy входу первого блока памяти, выход переполнения второго счетчика подключен к счетному входу третьего счетчика, выход которого подключен к вторьи входам первого и второго бло ков формирования адреса, выход пере- полнения третьего счетчика подключен к счетному входу первого счетчика, выход которого подклю сен к третьему входу второго блока формирования ад- реса и к первому входу третьего блока формирования адреса, третий выход генератора тактовых импульсов подключен к синхровходу. блока микропрограммного управления, синхровходам реги- стров с первого по пятый, к младшему разряду информационного входа демуль- типлексора и через второй формирователь имйульсов к второму управ ляющему входу второго блока памяти, выход разрешения вычисления функций блока микропрограммного управления подключен к второму входу злемен та И, вьпсод адреса блока памяти блока микропрограммного управления подключен к адресному входу третьего мультиплексора и к адресному входу второго блока памяти, первый управляющий и информационный входы которого подключены соответственно к выходу режима работы блока иащтк блока микропрограммного управления и к выходу третьего мультиплексора, выход второго блока памяти и выходы шестого, седьмого и восьмого регистров подключены соответственно к информационным входам с первого по четвертый четвертого мультиплексора, адресньй вход и выход которого подключен соответственно к выходу выбора первого операнда блока микропрограммного управленкя и информационному входу пятого регистра, выход которого подключен к второму входу умножителя, выход второго регистра подключен к первому информационному входу пятого мультиплексора и к старшим разрядам информационного входа демультиплексора, старшие разряды выходов с первого до,четвертый которого подключены соответственно к информационному входу третьего блока памяти и к информационным входам шестого, седьмого и восьмого регистров, синх- ровходы которых подключены к младшему разряду соответственно второго, третьего и четвертого выходов демультиплексора, адресньй вход которого подключен к выходу адреса демультиплексора блока микропрограммного зтаравления, выход выбора операнда сумматора и в вход нулевого кода устройства подключены соответственно к адресному и второму информационному входам пятого мультиплексора, выход которого подключен к второму входу сумматора, выходы первого и четвертого блок ов памяти и выход второго операнда блока микропрограммного управления подключены соответственно к первому и второму информационным входам и к адресному входу первого мультиплексора,выход номера компонента вектора блока микропрограммного управления подключен к второму входу третьего блока формирования адреса, выход которого подключен к адресному входу четвертого блока памяти, выход режима работы

устройства блока микропрограммного управления подключен к адресньм входам второго и шестого мультиплек- соров, первому управляющему входу третьего блока памяти и к выходу готовности информации устройства,вход угла поворота системы координат устройства и выход нймера компонента - вектора блока микропрограммного уп- равления подключены соответственно к четвертому и пятому входам второго блока формирования адреса, выход счетчика подключен к старшим.разрядам информационного входа третьего регист- ра, выход которого подключен к информационному выходу четвертого регистра, выход которого и вход адреса считыва-.2 .3

.4 .5

вычисления функций

Адрес блока 13 памяти

1-разрешено

-сОООО,0001,..., 1000

Номер компоненты ,00 - п

вектора п

Р

01 10

Пра

Пр,

Выбор первого операнда

Выбор второго операнда

О - БП11 БП12

00 01 10 11

БП13, Рг26, Рг27, Рг28

.6 .7

,8

Выбор операнда сумматора

Адрес демульти- плексора

Режим работы устройства

0- нулевой код,

1- Рг 25

00 01 10

11

БП14, Рг26, Рг27, Рг28

0- .вьщача функций из БП 14 (Готов)

1- вычисление функций .и запись в БП 14 (Не готов)

кия устройства подключены соответственно к первому и второму информационным входам шестого мультиплексора, выход которого подключен к адресному входу третьего блока памяти, вход строба считывания устройства подключен к второму информационному входу второго мультиплексора, выход которого через третий формирователь импульсов подключен к второму управляющему входу третьего блока памячш, выход которого подключен к информационному выходу устройства, В-й информационный вход устройства подключен к В-му информационному входу третьего мультиплексора, ,9,

Адрес ные входы БП13 и мультиплексора 20

Вход БФА 10

Пра

Пр,

Адресный вход мультиплексора 17

Адресный вход мультиплексора 18

код,

Адресный вход мультиплексора 19

Адресный вход демульти- плексора 35

Адресные входы мультиплексоров 15,16, первый управляющий вход БП14, выход 38 устройства

п

1425706

Первый управляющий вход БП 13

Вход БФА 9

Фи е. 7

Фиъ.З

Г

Фиг. 6

Фиг. 7

Авторы

Даты

1988-09-23—Публикация

1987-03-23—Подача