1

Изобретение относится к автоматике и вычислительной технике и может быть, в частности, использовано для распределения заданий в многомашинных и многопроцессорных системах, в том числе в вычислительных сетях.

Цель изобретения - повышение надежности функционирования за счет повышения вероятности обслуживания запросов.

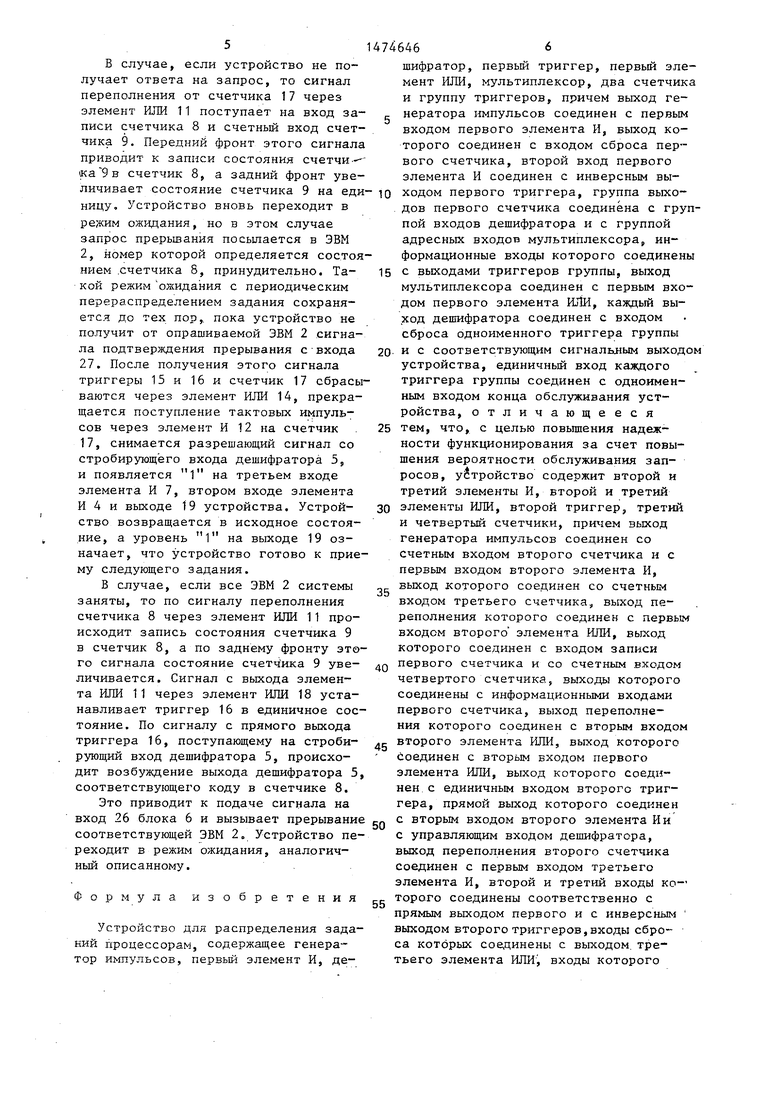

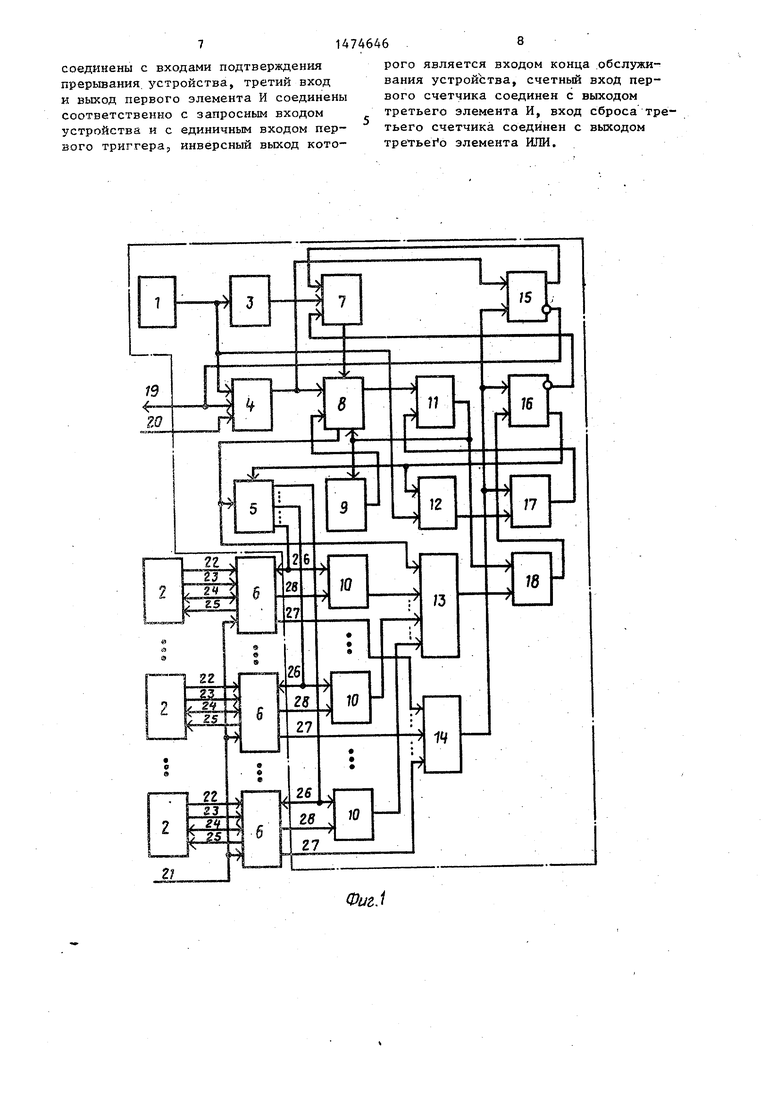

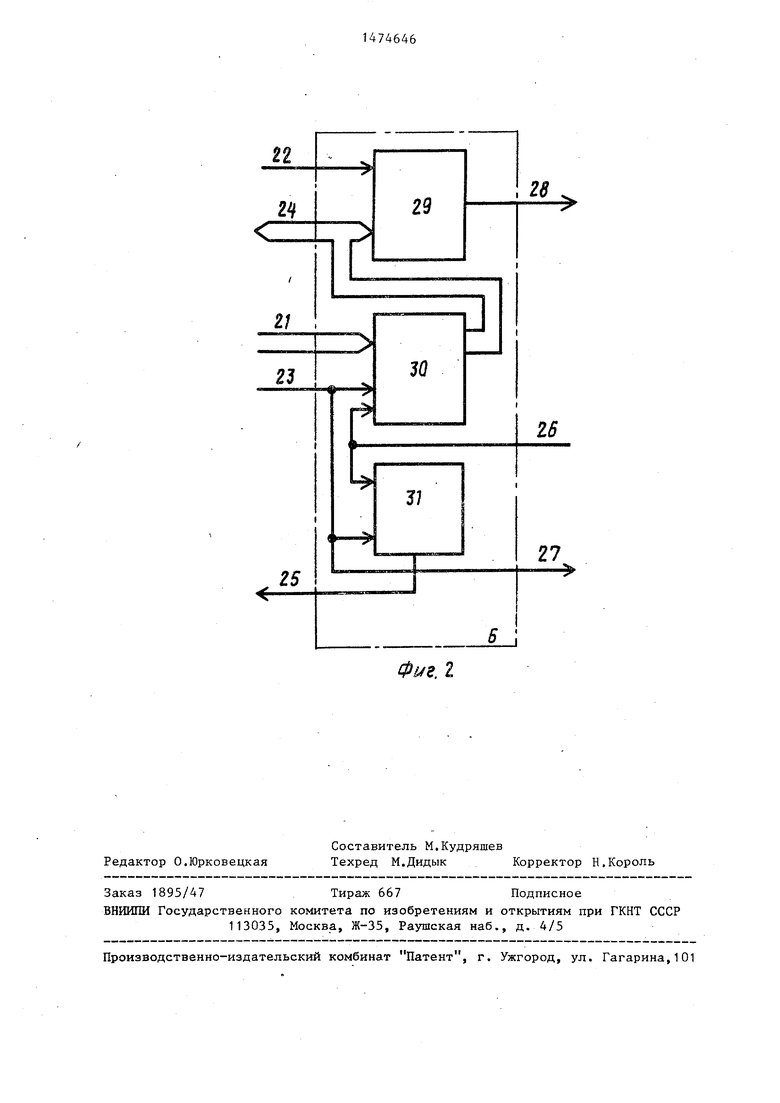

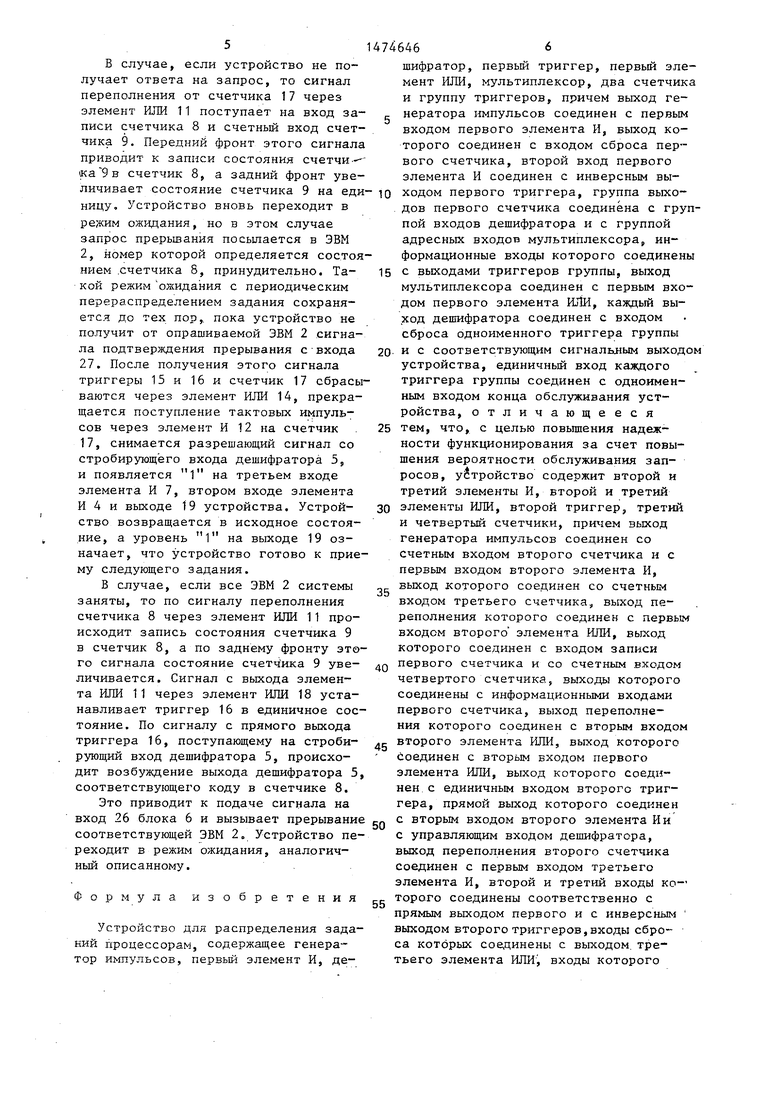

На фиг. 1 представлена функциональная схема устройства; на фиг.2 - функциональная схема блока подключения .

На схеме (фиг. 1) обозначены генератор 1 импульсов, ЭВМ 2, счетчик 3, элемент И 4, дешифратор 5, блоки

6 подключения, элемент И 7, счетчики 8 и 9, триггеры 10, элемент ИЛИ 11, элемент И 12, мультиплексор 13, элемент ИЛИ 14, триггеры 15 и 16, счетчик 17, элемент ИЛИ 18, выход 19 конца обслуживания устройства, запросный вход 20 устройства, вход 21 блоков 6, выходы 22 и 23 ЭВМ 2, магистраль 24 ЭВМ 2, вход 25 ЭВМ 2, сигнальные входы 26, входы 27 подтверждения прерывания устройства и входы 28 конца обслуживания устройства. Каждый блок 6 в соответствии (фиг. 2) содержит дешифратор 29, буферный регистр 30 и триггер 31.

Работа блока 6 подключения (фиг,2) состоит в том, что при поступлении

4 vl

Јг,

зэ

сигнала на вход 26 происходят запись кода с шины 21 в буферный регистр 30, установка триггера 31 в единичное состояние и посылка запроса прерывания на выход 25. По сигналу подтверждения прерывания с входа 23 блока 6 содержимое регистра 30 выдается на магистраль 24 ЭВМ и триггер 31 обнуляется. На выходе 27 появляется сигнал подтверждения прерывания При завершении обслуживания заданий, распределенных в ЭВМ, последняя выставляет на магистрали 24 адрес устройства и сигнал сопровождения на вход 22. При этом возбуждается выход 28 дешифратора 29, подключенный к входу установки в 1 триггера 10.

Устройство работает следующим образом.

В исходном состоянии (при включении питания) триггеры 15 и 16 и счетчики 3, 8, 9 и 17 сброшены в О.

Устройство распределяет задания на свободную ЭВМ 2, соответствующий триггер 10 которой находится в состоянии 1. Если все процессоры заняты, то происходит их загрузка в режиме прерывания в порядке очереди, определяемой счетчиком 9, содержимое которого увеличивается после каждого распределения задания в занятую ЭВМ или при перераспределении задания , если ЭВМ не отвечае т сигналом подтверждения прерывания в течение времени, определяемого счетчиком 17. Загрузка заданий в ЭВМ 2 производится в этом случае в режиме прерывания.

Для поиска свободных ЭВМ используется счетчик 8. В результате такого алгоритма гарантируется распределе- лне заданий и обеспечивается равномерность загрузки всех ЭВМ системы.

При поступлении задания на вход 21 и сигнала запроса на вход 20 устройства на третьем входе элемента И 4 устанавливается 1, что разрешает прохождение тактовых импульсов от генератора 1 на выход элемента И 4. Первый тактовый импульс, прошедший через элемент И 4, сбрасывает счетчик 8 и устанавливает триггер 15 в единичное состояние. Это приводит к снятию сигнала конца распределения задания с выхода 19 устройства и появлению низкого уровня на втором входе элемента И 4, запрешающего дальнейшее прохождение тактовых импульсов на его выход. Этим достигается

0

5

0

5

0

5

0

5

0

5

синхронизация начала работы устройства и нечувствительность устройства к появлению очередного сигнала на входе 20 запроса до окончания цикла работы устройства„ Одновременно появляется 1 на первом входе элемента И 7, поступающая с прямого выхода триггера 15 и разрешающая прохождение тактовых импульсов от счетчика 3 через элемент И 7 на счетный вход счетчика 8.

Состояние счетчика 8 определяет адрес триггера 10, выход которого через мультиплексор 13 и элемент ИЛИ 18 подключается на вход установки в 1 триггера 16. Если соответствующая ЭВМ не занята, то сигналом с выхода элемента ИЛИ 18 происходит установка триггера 16 в 1.

По сигналу с прямого выхода триггера 16, поступающему на стробирую- щий вход дешифратора 5, происходит возбуждение соответствующего выхода дешифратора 5 в соответствии с кодом в счетчике 8, Сигнал с возбужденного выхода дешифратора 5 поступает в ЭВМ 2 (вход 26 блока 6), вызывая ее прерывание для приема задания с шины 21, а также производит сброс триггера 10 (логический О в триггере соответствует занятости ЭВМ). Если соответствующая ЭВМ 2 занята, то на выходе элемента ИЛИ 18 сигнал не формируется, и при поступлении следующего тактового импульса от счетчика 3 состояние счетчика 8 увеличивается на 1 и происходит проверка занятости следующей ЭВМ.

После установки триггера 16 в единичное состояние сигнал с его прямого выхода поступает на вход элемента И 12, разрешая прохождение тактовых импульсов от генератора 1 на счетный вход счетчика 17, а низкий уровень с инверсного выхода запрещает прохождение тактовых импульсов от счетчика 3 через элемент И 7 на счетный вход счетчика 8. Устройство переходит в режим ожидания ответа. Сигналом ответа от ЭВМ 2 служит сигнал подтверждения прерывания на входе 27 устройства. Если на вход элемента ИЛИ 14 поступает сигнал подтверждения прерывания с входа 27, то на выходе элемента ИЛИ 14 возбуждается сигнал, сбрасывающий триггеры 15 и 16 и счетчик 17.

В случае, если устройство не получает ответа на запрос, то сигнал переполнения от счетчика 17 через элемент ИЛИ 11 поступает на вход записи счетчика 8 и счетный вход счетчика 9. Передний фронт этого сигнала приводит к записи состояния счетчи- «а 9 в счетчик 8, а задний фронт увешифратор, первый триггер, первый элемент ИЛИ, мультиплексор, два счетчика и группу триггеров, причем выход генератора импульсов соединен с первым входом первого элемента И, выход которого соединен с входом сброса первого счетчика, второй вход первого элемента И соединен с инверсным вы

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения заданий процессорам | 1985 |

|

SU1278848A1 |

| Устройство для подключения источников информации к общей магистрали | 1989 |

|

SU1679498A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1317438A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ ОТКАЗОВ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1996 |

|

RU2099777C1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1987 |

|

SU1472913A1 |

| Устройство для обслуживания запросов | 1988 |

|

SU1571588A1 |

| Станция локальной сети | 1987 |

|

SU1478221A1 |

| Устройство для отладки микропроцессорных систем | 1989 |

|

SU1672455A1 |

| Устройство для сопряжения магистрали ЭВМ с магистралью внешних устройств | 1984 |

|

SU1246105A1 |

| Устройство для обслуживания запросов | 1978 |

|

SU728128A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для распределения заданий в многопроцессорных системах и в вычислительных сетях. Цель изобретения - повышение надежности функционирования путем повышения вероятности обслуживания запросов. Устройство содержит генератор импульсов, четыре счетчика, три элемента И, дешифратор, два триггера, три элемента ИЛИ,мультиплексор, группу триггеров. Устройство работает в автоматическом режиме. При приеме задания устройство осуществляет поиск свободных процессоров и распределяет задание в ближайший свободный процессор, ожидая от него ответ о возможности обслуживания. Если ответ не получен, задание перераспределяется в другой процессор принудительно. В случае, если все процессоры заняты, задание распределяется принудительно, но так же, как и в предыдущем случае, устройство ожидает ответа о возможности обслуживания. 2 ил.

личивает состояние счетчика 9 на еди- ю ходом первого триггера, группа выхоницу. Устройство вновь переходит в режим ожидания, но в этом случае запрос прерывания посылается в ЭВМ 2, номер которой определяется состоянием счетчика 8, принудительно. Такой режим ожидания с периодическим перераспределением задания сохраняется до тех пор, пока устройство не получит от опрашиваемой ЭВМ 2 сигнала подтверждения прерывания с входа 27. После получения этого сигнала триггеры 15 и 16 и счетчик 17 сбрасываются через элемент ИЛИ 14, прекращается поступление тактовых импульсов через элемент И 12 на счетчик 17, снимается разрешающий сигнал со стробирующёго входа дешифратора 5, и появляется 1 на третьем входе элемента И 7, втором входе элемента И 4 и выходе 19 устройства. Устройство возвращается в исходное состояние, а уровень 1 на выходе 19 означает, что устройство готово к приему следующего задания.

В случае, если все ЭВМ 2 системы заняты, то по сигналу переполнения счетчика 8 через элемент ИЛИ 11 происходит запись состояния счетчика 9 в счетчик 8, а по заднему фронту этого сигнала состояние счетчика 9 увеличивается. Сигнал с выхода элемента ИЛИ 11 через элемент ИЛИ 18 устанавливает триггер 16 в единичное состояние. По сигналу с прямого выхода триггера 16, поступающему на строби- рующий вход дешифратора 5, происходит возбуждение выхода дешифратора 5, соответствующего коду в счетчике 8.

Это приводит к подаче сигнала на вход 26 блока 6 и вызывает прерывание соответствующей ЭВМ 2. Устройство переходит в режим ожидания, аналогичный описанному.

Формула изобретения

прямым выходом первого и с инверсным Устройство для распределения зада- выходом второго триггеров,входы сброса которых соединены с выходом третьего элемента ИЛИ входы которого

ний процессорам, содержащее генератор импульсов, первый элемент И, де

дов первого счетчика соединена с группой входов дешифратора и с группой адресных входов мультиплексора, информационные входы которого соединены с выходами триггеров группы, выход мультиплексора соединен с первым входом первого элемента ИЛИ, каждый выход дешифратора соединен с входом сброса одноименного триггера группы

и с соответствующим сигнальным выходом устройства, единичный вход каждого триггера группы соединен с одноименным входом конца обслуживания устройства, отличающееся тем, что, с целью повышения надежности функционирования за счет повышения вероятности обслуживания запросов, устройство содержит второй и третий элементы И, второй и третий элементы ИЛИ, второй триггер, третий и четвертый счетчики, причем выход генератора импульсов соединен со счетным входом второго счетчика и с первым входом второго элемента И, выход которого соединен со счетным входом третьего счетчика, выход переполнения которого соединен с первым входом второго элемента ИЛИ, выход которого соединен с входом записи первого счетчика и со счетным входом четвертого счетчика, выходы которого соединены с информационными входами первого счетчика, выход переполнения которого соединен с вторым входом

второго элемента ИЛИ, выход которого соединен с вторым входом первого элемента ИЛИ, выход которого соединен с единичным входом второго триггера, прямой выход которого соединен с вторым входом второго элемента Ии с управляющим входом дешифратора, выход переполнения второго счетчика соединен с первым входом третьего элемента И, второй и третий входы ко-

торого соединены соответственно с

соединены с входами подтверждения прерывания устройства, третий вход и выход первого элемента И соединены соответственно с запросным входом устройства ч с единичным входом первого триггера, инверсный выход которого является входом конца обслуживания устройства, счетный вход первого счетчика соединен с выходом третьего элемента И, вход сброса третьего счетчика соединен с выходом третьего элемента ИЛИ.

Фе/е. 2

| Устройство для распределения задач между процессорами | 1981 |

|

SU982005A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1278848A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-04-23—Публикация

1987-07-06—Подача