1

Изобретение относится к импульсной технике и может быть использовано для индикации моментов окончания параллельных переходных процессов.

Цель изобретения - повышение надежности Г-триггера путем сокращения числа используемых элементов (введение резистора и МОП-транзистора р-ти па позволяет заменить элемент ИЛИ-НЕ выходным инвертором, что дает экономию оборудования).

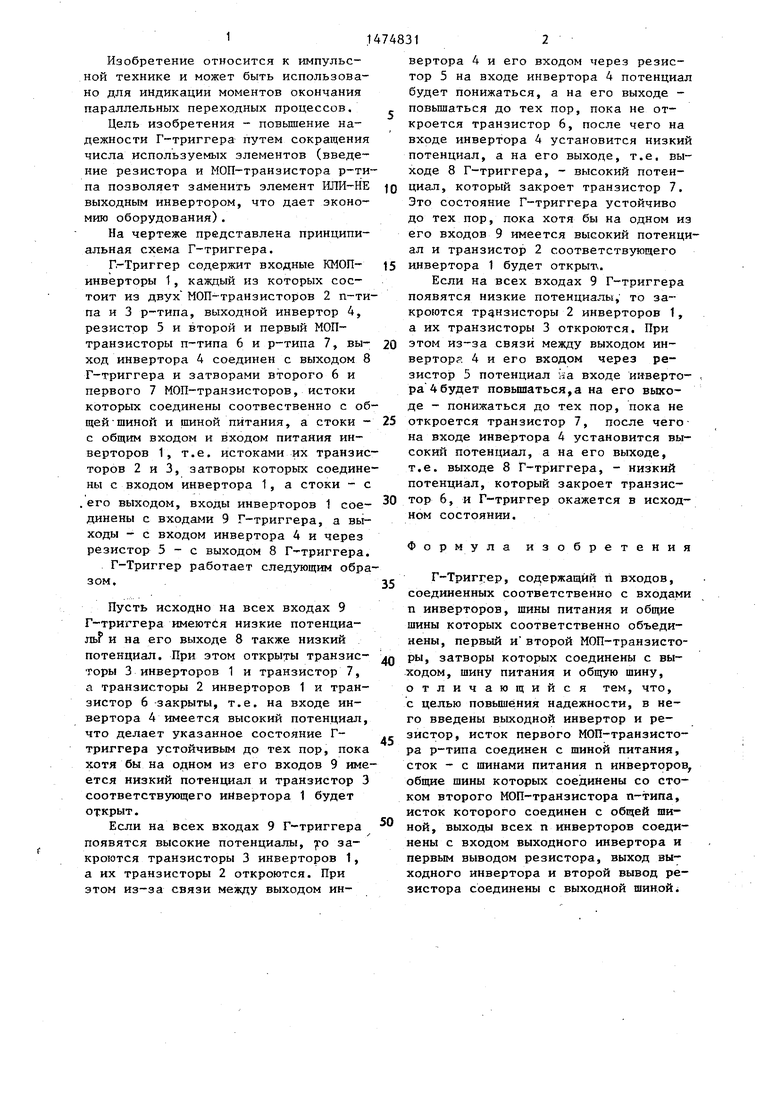

На чертеже представлена принципиальная схема Г-триггера.

Г-Триггер содержит входные КМОП- инверторы 1, каждый из которых состоит из двух МОП-транзисторов 2 п-ти па и 3 р-типа, выходной инвертор 4, резистор 5 и второй и первый МОП- транзисторы п-типа 6 и р-типа 7, выход инвертора 4 соединен с выходом 8 Г-триггера и затворами второго 6 и первого 7 МОП-транзисторов, истоки

1

20 этом из-за связи между выходом инвертор 4 и его входом через резистор 5 потенциал ia входе инвертора 4 будет повышаться,а на его выходе - понижаться до тех пор, пока не

которых соединены соотвественно с общей шиной и шиной питания, а стоки - 25 откроется транзистор 7, после чего с общим входом и входом питания ин- на входе инвертора 4 установится вы- верторов 1, т.е. истоками их транзис- сокий потенциал, а на его выходе, торов 2 и 3, затворы которых соедине- т.е. выходе 8 Г-триггера, - низкий ны с входом инвертора 1, а стоки - с

30

.его выходом, входы инверторов 1 соединены с входами 9 Г-триггера, а выходы - с входом инвертора 4 и через резистор 5 - с выходом 8 Г-триггера.

Г-Триггер работает следующим образом.

Пусть исходно на всех входах 9 Г-триггера имеются низкие потенциа- льР и на его выходе 8 также низкий потенциал. При этом открыты транзисторы 3 инверторов 1 и транзистор 7, а транзисторы 2 инверторов 1 и транзистор 6 закрыты, т.е. на входе инвертора 4 имеется высокий потенциал, что делает указанное состояние Г- триггера устойчивым до тех пор, пока хотя бы на одном из его входов 9 имеется низкий потенциал и транзистор 3 соответствующего инвертора 1 будет открыт.

Если на всех входах 9 Г-триггера

s

появятся высокие потенциалы, то закроются транзисторы 3 инверторов 1, а их транзисторы 2 откроются. При этом из-за связи между выходом инпотенциал, который закроет транзистор 6, и Г-триггер окажется в исходном состоянии.

35

40

45

50

Формула изобретения

Г-Триггер, содержащий п входов, соединенных соответственно с входами п инверторов, шины питания и общие шины которых соответственно объединены, первый и второй МОП-транзисторы, затворы которых соединены с выходом, шину питания и общую шину, отличающийся тем, что, с целью повышения надежности, в него введены выходной инвертор и резистор, исток первого МОП-транзистора р-типа соединен с шиной питания, сток - с шинами питания п инверторов, общие шины которых соединены со стоком второго МОП-транзистора п-типа, исток которого соединен с общей шиной, выходы всех п инверторов соединены с входом выходного инвертора и первым выводом резистора, выход выходного инвертора и второй вывод резистора соединены с выходной шиной.

4748312

вертора 4 и его входом через резистор 5 на входе инвертора 4 потенциал будет понижаться, а на его выходе - - повышаться до тех пор, пока не откроется транзистор 6, после чего на входе инвертора 4 установится низкий потенциал, а на его выходе, т.е. выходе 8 Г-триггера, - высокий потен10 циал, который закроет транзистор 7. Это состояние Г-триггера устойчиво до тех пор, пока хотя бы на одном из его входов 9 имеется высокий потенциал и транзистор 2 соответствующего

15 инвертора 1 будет открыт,.

Если на всех входах 9 Г-триггера появятся низкие потенциалы, то закроются транзисторы 2 инверторов 1, а их транзисторы 3 откроются. При

20 этом из-за связи между выходом инвертор 4 и его входом через резистор 5 потенциал ia входе инвертора 4 будет повышаться,а на его выходе - понижаться до тех пор, пока не

25 откроется транзистор 7, после чего на входе инвертора 4 установится вы- сокий потенциал, а на его выходе, т.е. выходе 8 Г-триггера, - низкий

откроется транзистор 7, после чего на входе инвертора 4 установится вы- сокий потенциал, а на его выходе, т.е. выходе 8 Г-триггера, - низкий

потенциал, который закроет транзистор 6, и Г-триггер окажется в исходном состоянии.

5

0

5

0

Формула изобретения

Г-Триггер, содержащий п входов, соединенных соответственно с входами п инверторов, шины питания и общие шины которых соответственно объединены, первый и второй МОП-транзисторы, затворы которых соединены с выходом, шину питания и общую шину, отличающийся тем, что, с целью повышения надежности, в него введены выходной инвертор и резистор, исток первого МОП-транзистора р-типа соединен с шиной питания, сток - с шинами питания п инверторов, общие шины которых соединены со стоком второго МОП-транзистора п-типа, исток которого соединен с общей шиной, выходы всех п инверторов соединены с входом выходного инвертора и первым выводом резистора, выход выходного инвертора и второй вывод резистора соединены с выходной шиной.

| название | год | авторы | номер документа |

|---|---|---|---|

| Г-триггер | 1987 |

|

SU1562964A1 |

| Г-триггер | 1986 |

|

SU1370731A1 |

| Г-триггер | 1986 |

|

SU1372597A1 |

| Г-триггер | 1987 |

|

SU1443137A1 |

| ЛОГИЧЕСКОЕ КОНВЕЙЕРНОЕ УСТРОЙСТВО | 2000 |

|

RU2175811C1 |

| УСТРОЙСТВО ЭЛЕКТРОННОГО ГИСТЕРЕЗИСА | 2012 |

|

RU2486668C1 |

| Г-ТРИГГЕР | 2007 |

|

RU2371842C2 |

| СТАТИЧЕСКАЯ ЗАПОМИНАЮЩАЯ ЯЧЕЙКА С ДВУМЯ АДРЕСНЫМИ ВХОДАМИ | 2011 |

|

RU2470390C1 |

| Параллельный асинхронный регистр | 1988 |

|

SU1624530A1 |

| Триггерное устройство | 1984 |

|

SU1228221A1 |

Изобретение относится к импульсной технике и может быть использовано для индикации моментов окончания параллельных переходных процессов.Цель изобретения - повышение надежности путем сокращения числа используемых транзисторов и их связей. Г-триггер содержит входов 9, (N+1) КМОП-инверторов 1 и 4, резистор 5, P-транзистор 7, N-транзистор 6, выход 8. Устройство переключается в альтернативное состояние при равенстве (альтернативном предыдущему) лог. уровней на всех входах 9. Работа Г-триггера в этом режиме описана в материалах изобретения. 1 ил.

| Г-Триггер | 1986 |

|

SU1359887A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство СССР по заявке 4049931/24-21, 07.04.86 | |||

| Автоматное управление асинхронными процессами в ЭВМ и дискретных системах | |||

| /Под ред | |||

| В.И.Варшавского | |||

| М.: Наука, 1986, с.79, рис.4.2. | |||

Авторы

Даты

1989-04-23—Публикация

1987-07-06—Подача