со to ел

Изобретение относится к импульсной технике и может быть использовано для индикации элементов окончания переходньк процессов, в цифровых ком бинаторных и триггерных структурах. Целью изобретения является повышение надежности и снижение нагрузки на входные шины, достигаемое сокращением числа используемых актив- ных элементов.

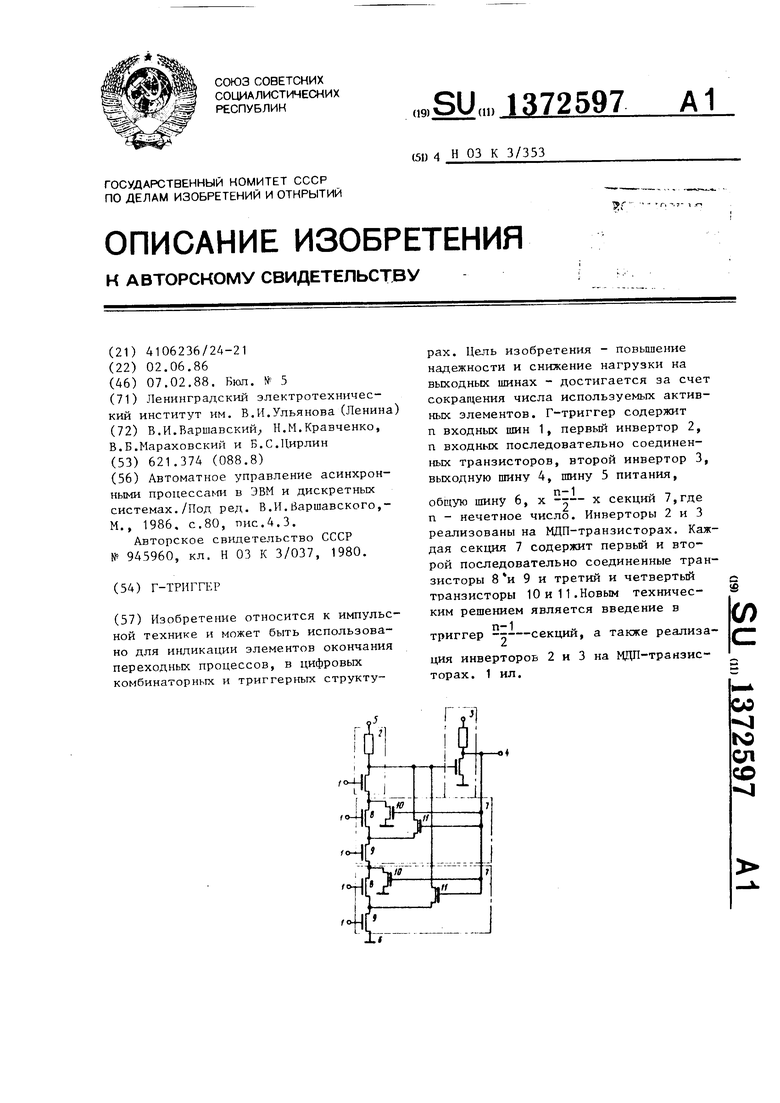

На чертеже представлена электрическая принципиальная схема Г-триг- гера.

Устройство содержит п входных шин 1, первый инвертор 2, п входных последовательно соединенных транзисторов, второй инвертор 3, выходную шину 4, шину 5 питания, общую шину 6,

--- секций 7 (п - нечетное число), а инверторы 2 и 3 реализованы на ЩПзисторы 8 и 9 секций 7 и инвертора 2 Тогда на затвор транзистора инвертор 3 поступает высокий потенциал, откры ваюпу й этот транзистор, и на вькод- ной шине 4 будет низкий потенциал, который, поступая на затворы транзисторов 10 и 11, закрывает их. Вслед ствие этого на затворе транзистора инвертора 3 высокий потенциал, откры вающий этот транзистор, сохраняется до тех пор, пока закрыт хотя бы один из транзисторов 8 и 9 и транзистор инвертора 2, т.е. низкий потенциял на выходной шине 4 сохраняется до тех пор, пока хотя бы на одной из ег шин 1 присутствует низкий потенциал. Только после того, как на всех шинах 1 появится высокий потенциал, откры- ваю1 Щй транзисторы 8 и 9 и транзистор инвертора 2, на затворе транзисто ра инвертора 3 появится низкий потен циал, закрывающий этот транзистор, и на выходной шине 4 появится высотранзисторах, каждая секция 7 содержит первый 8 и второй 9 последовательно соединенные транзисторы, затворы 25 кий потенциал, который откроет тран- которых являются первым и вторым вхо- зисторы 10 и 11. В результате низкий дами секции 7, третий и четвертый транзисторы 10 и 11, затворы которых являются третьим входом секции 7.

30

Стоки первого и третьего транзисторов 8 и 10 являются первым выходом секции 7. Исток третьего транзистора 10 соединен с общей шиной 6, сток четвертого транзистора 11 является четвертым входом секции 7, а исток соединен со средней точкой соединения первого 8 и второго 9 транзисторов. Исток второго хранзистора 9 является вторым выходом секции 7. питания первого инвертора 2 соединены соответственно с шиной 5 питания и с первым выходом первой секции 7. Второй выход последней секции 7 соединен с общей шиной 6, второй выход остальных секций 7 соединен с первым выходом следующей секции 7. Третьи входы сак- ций 7 соединеннг с выходной шиной 4 и с выходом второго инвертора 3, вход которого соединен с выходом первого инвертора 2 и с четвертым входом каждой секции 7.Первый и второй входы секций 7 соединены с соответствующими п-1 входными шинами 1. Первая входная щина 1 соединена с входом первого инвертора 2.

Г-триггер работает следуюп(им образом.

Пусть на входных шинах 1 имеется низкий потенциал, закрызакжщй тран40

потенциал на затворе транзистора инв ртора 3 сохраняется до тех пор, пока открыт хотя бы один из транзисторов 8 и 9 и транзистор инвертора 2, т.е высокий потенциал на выходной шине 1 сохраняется до тех пор, пока хотя бы на одной из его шин 1 присутствует высокий потенциал.

35 Только после того, как на всех входных шинах 1 появится низкий потенциал, закрывающий транзисторы 8 и 9 и транзистор инвертора 2, на зат воре транзистора инвертора 3 появится высокий потенциал, открывающий этот транзистор, и на выходной шине 4 появится низкий потенциал, который закроет транзисторы 10 и 11, возвращая тем самым Г -триггер в исходное состояние.

Формула изобретения

Г-триггер, содержащий п входных 50 шин, первый инвертор, второй инвертор, выходную шину, шину питания, общую шину, отличаюшийся тем, что, с целью повышения надежности и снижения нагрузки на входные

55п-Г

ши1{ы в него введены секции

(п - нечетное число), а инверторы реализованы на МДП-транзисторах, каждая секция содержит первый и вто45

зисторы 8 и 9 секций 7 и инвертора 2. Тогда на затвор транзистора инвертора 3 поступает высокий потенциал, откры- ваюпу й этот транзистор, и на вькод- ной шине 4 будет низкий потенциал, который, поступая на затворы транзисторов 10 и 11, закрывает их. Вследствие этого на затворе транзистора инвертора 3 высокий потенциал, открывающий этот транзистор, сохраняется до тех пор, пока закрыт хотя бы один из транзисторов 8 и 9 и транзистор инвертора 2, т.е. низкий потенциял на выходной шине 4 сохраняется до тех пор, пока хотя бы на одной из его шин 1 присутствует низкий потенциал. Только после того, как на всех шинах 1 появится высокий потенциал, откры- ваю1 Щй транзисторы 8 и 9 и транзистор инвертора 2, на затворе транзистора инвертора 3 появится низкий потенциал, закрывающий этот транзистор, и на выходной шине 4 появится высокий потенциал, который откроет тран- зисторы 10 и 11. В результате низкий

кий потенциал, который откроет тран- зисторы 10 и 11. В результате низкий

потенциал на затворе транзистора инвертора 3 сохраняется до тех пор, пока открыт хотя бы один из транзисторов 8 и 9 и транзистор инвертора 2, т.е. высокий потенциал на выходной шине 1 сохраняется до тех пор, пока хотя бы на одной из его шин 1 присутствует высокий потенциал.

Только после того, как на всех входных шинах 1 появится низкий потенциал, закрывающий транзисторы 8 и 9 и транзистор инвертора 2, на затворе транзистора инвертора 3 появится высокий потенциал, открывающий этот транзистор, и на выходной шине 4 появится низкий потенциал, который закроет транзисторы 10 и 11, возвращая тем самым Г -триггер в исходное состояние.

Формула изобретения

Г-триггер, содержащий п входных шин, первый инвертор, второй инвертор, выходную шину, шину питания, общую шину, отличаюшийся тем, что, с целью повышения надежности и снижения нагрузки на входные

п-Г

ши1{ы в него введены секции

(п - нечетное число), а инверторы реализованы на МДП-транзисторах, каждая секция содержит первый и вто

рои последовательно соединенные транзисторы, затворы которых являются первыми и вторыми входами секции, третий и четвертьп транзисторы, за- творы которых являются третьим входом секции, стоки первого и третьего транзисторов являются первым выходом секции, исток третьего транзистора соединен с общей шиной, сток четвертого транзистора является четвертым входом секции, а исток соединен со средней точкой соединения первого и второго транзисторов,исток второго транзистора является вторым вьтодом секции, исток ключевого транзистора первого инвертора соединен с первым выходом первой секции, второй выход последней секции соединен с общей шиной, вторые выходы остальных секций соединены с первым выходом следующей секции, третьи входы секций соединены с выходной шиной и выходом второго инвертора, вход которого соединен с выходом первого инветора и с четвертыми входами каждой секции, первый и второй входы секций соединены с соответствую1цими п-1 входными шинами, первая входная шина Соединена с входом первого инвертора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1987 |

|

SU1474738A1 |

| Выходное устройство на МДП-транзисторах | 1988 |

|

SU1598159A1 |

| Формирователь импульсов | 1981 |

|

SU1003348A1 |

| Формирователь импульсов | 1981 |

|

SU991507A1 |

| Формирователь импульсов на МДП-транзисторах | 1985 |

|

SU1569973A1 |

| Формирователь импульсов | 1985 |

|

SU1309278A1 |

| Формирователь выходных сигналов для запоминающего устройства на кмдп-транзисторах | 1978 |

|

SU767835A1 |

| Аналоговый переключатель | 1986 |

|

SU1385288A1 |

| УПРАВЛЯЕМАЯ ЛИНИЯ ЗАДЕРЖКИ | 1990 |

|

RU2012999C1 |

| Формирователь импульсов | 1983 |

|

SU1166279A1 |

Изобретение относится к импульсной технике и может быть использовано для индикации элементов окончания переходных процессов, в цифровых комбинаторных и триггерных структурах. Цель изобретения - повышение надежности и снижение нагрузки на выходных шинах - достигается за счет сокращения числа используемых активных элементов. Г-триггер содержит п входных шин 1, первый инвертор 2, п входньк последовательно соединенных транзисторов, второй инвертор 3, выходную шину 4, шину 5 питания, общую шину 6, X --- X секций 7,где п - нечетное число. Инверторы 2 и 3 реализованы на МДП-транзисторах. Каждая секция 7 содержит первый и второй последовательно соединенные транзисторы 8 и 9 и третий и четвертый транзисторы 10 и 11.Новым техническим решением является введение в триггерсекций, а также реализация инверторов 2 и 3 на МДП-транзисторах. 1 ил. с t О)

| Автоматное управление асинхронными процессами в ЭВМ и дискретных системах./Под ред | |||

| В.И.Варшавского,- М., 1986, с.80, пис.4.3 | |||

| Г-триггер | 1980 |

|

SU945960A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-02-07—Публикация

1986-06-02—Подача