J

Изобретение относится к вычислительной технике и может быть использовано для построения управляющих вычислительных систем с автоматическим присвоением адресов абонентов (периферийных устройств).

Цель изобретения - сокращение аппаратурных затрат и расширение класса решаемых задач путем автоматического присвоения адресов абонентов.

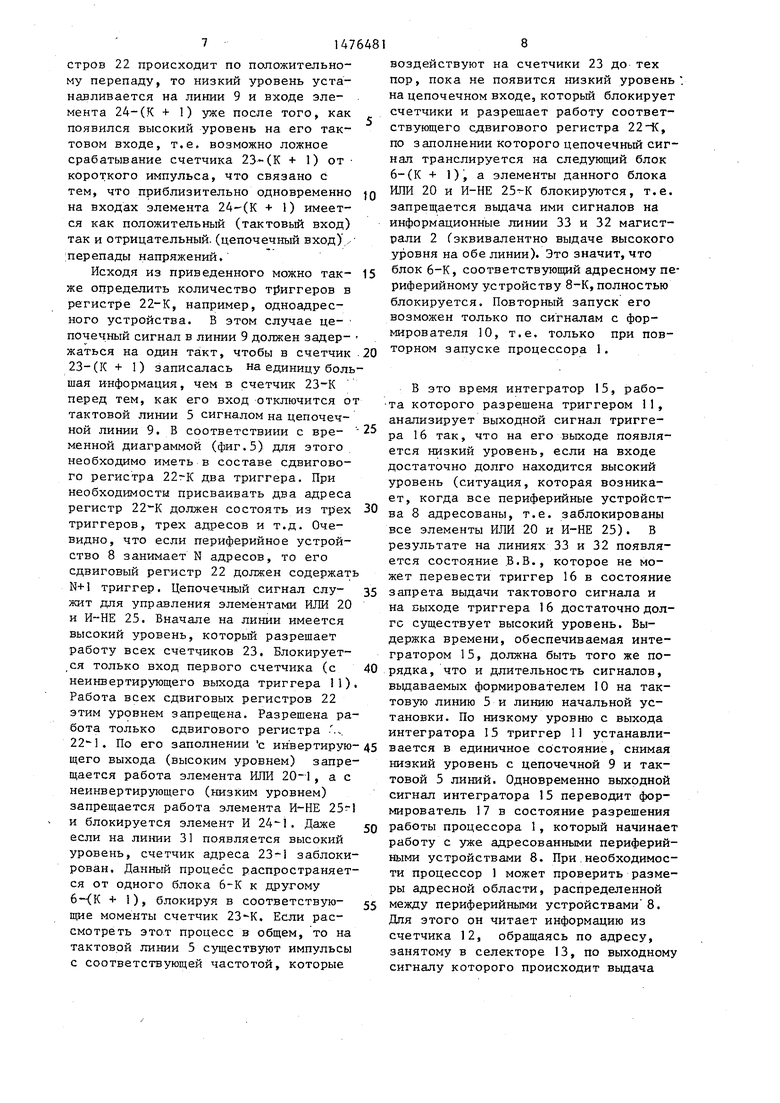

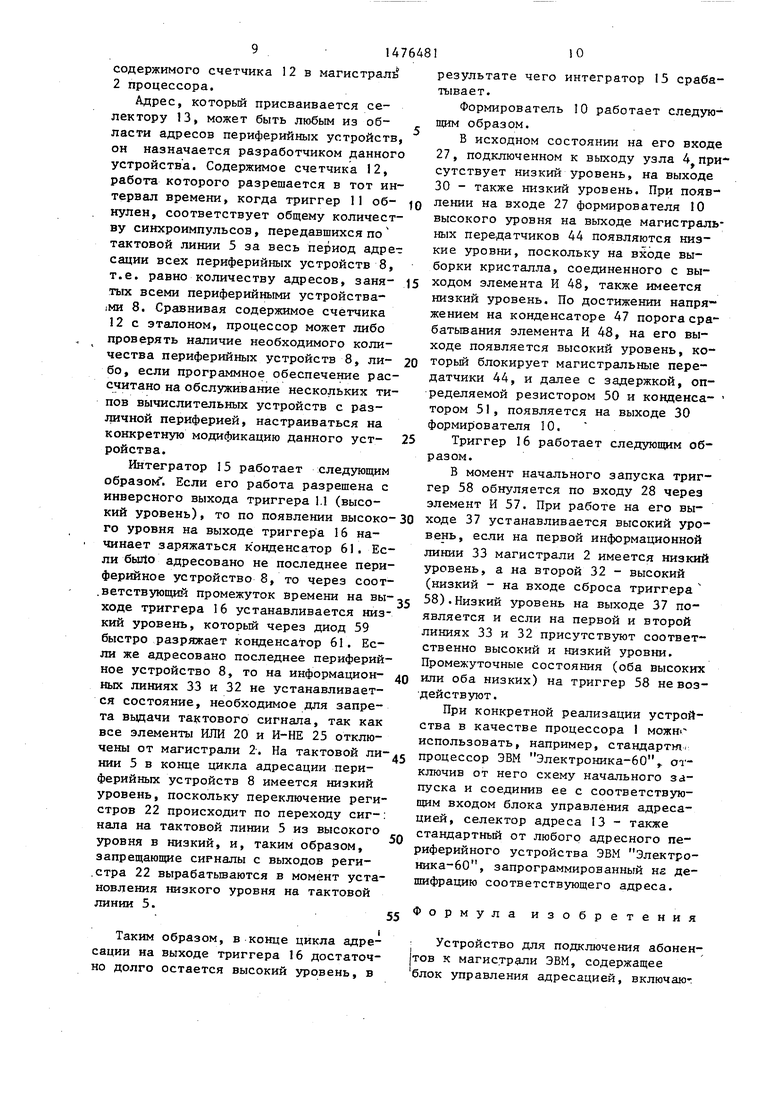

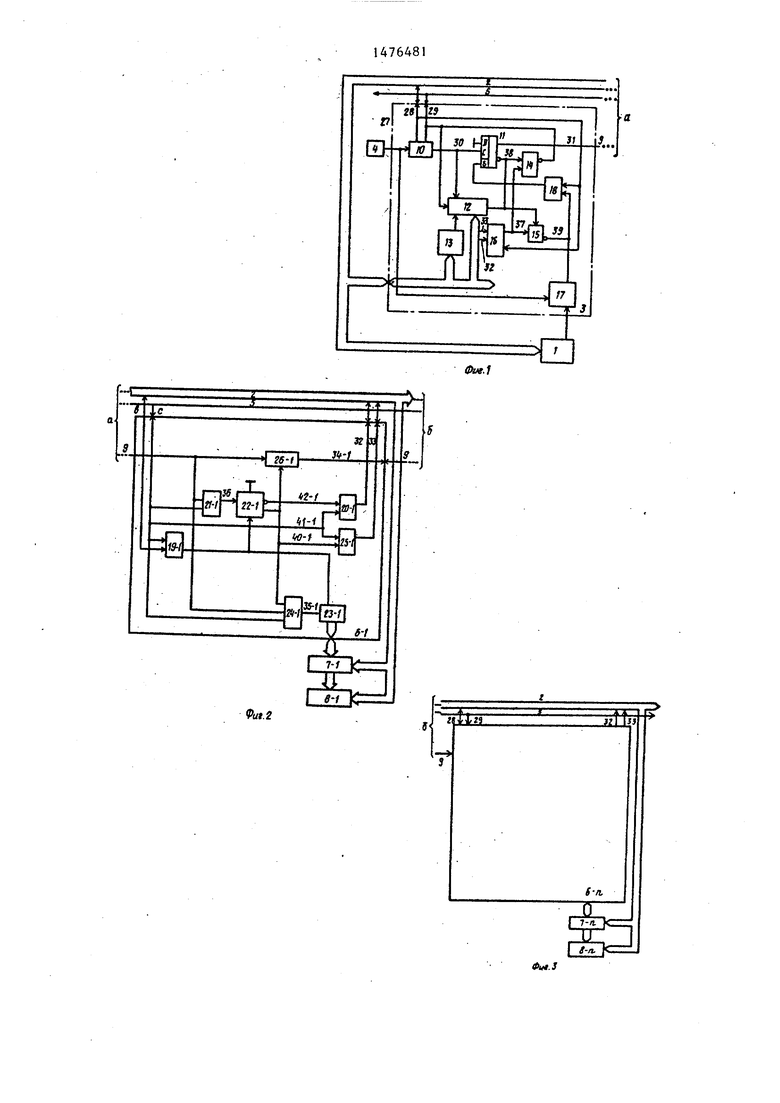

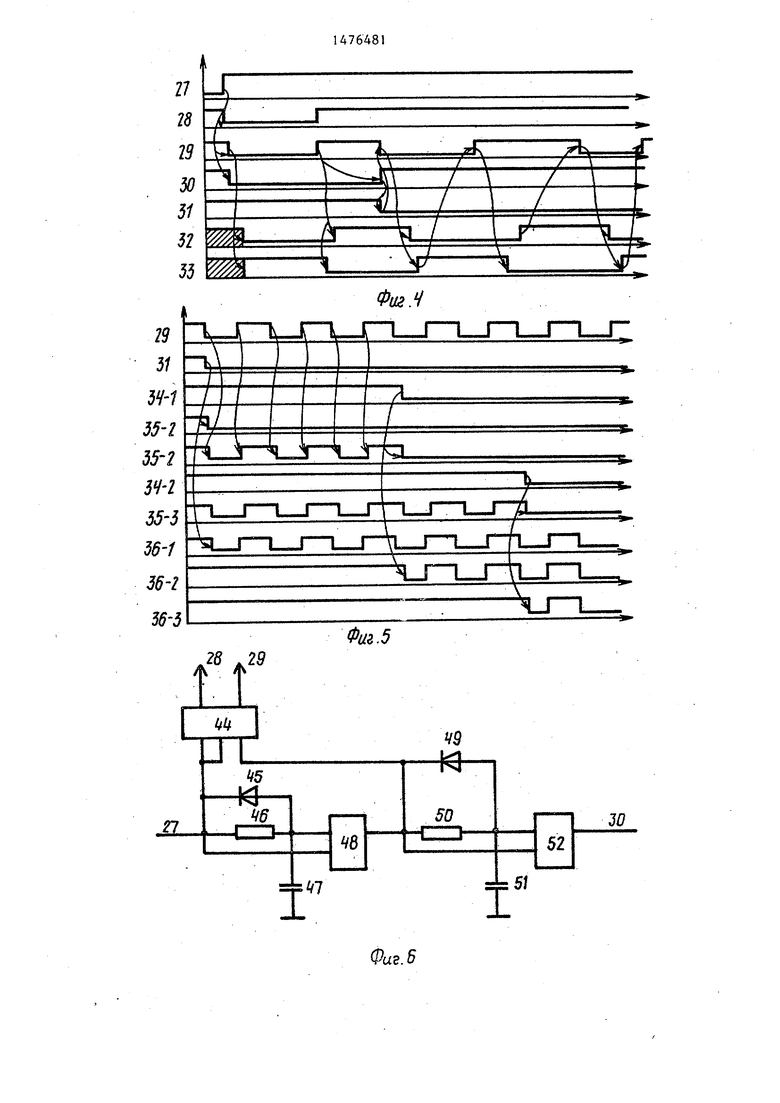

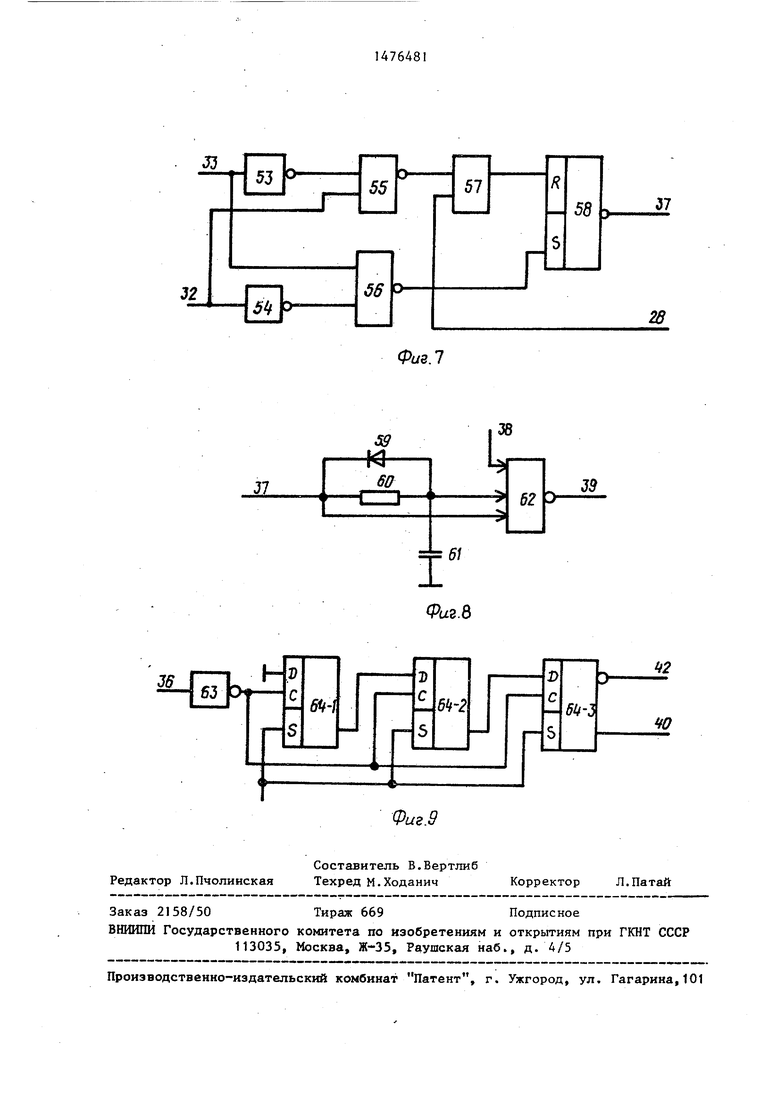

На фиг.1 - 3 приведена блок-схема устройства; на фиг. 4 - временная, диаграмма начального запуска и генерации сигналов на тактовой линии; на фиг.5 - временная диаграмма процесса присвоения адресаj на фиг.6 - схема формирователя импульсов; на фиг.7 - схема триггера управления; на фиг.8 схема интегратора; на фиг.9 - схема сдвигового регистра.

Устройство содержит процессор I, к которому подключена магистраль 2, и блок 3 управления адресации, к которому подключен узел 4 начального запуска и через тактовую линию 5 блоки 6 присвоения адреса, подключенные выходами к селекторам 7 адреса. Селекторы 7 адреса подключены к соответствующим периферийным устройствам (абонентам) 8. Опросные (цепочечные) входы и выходы блоков 3 и 6 соединены с помощью линии 9. В состав блока 3 управления адресацией входит формирователь 10 импульсов, подключенный к триггеру 11 опроса и счетчику 12, селектор 13 адреса устройства, эле-- мент И-НЕ 14, интегратор 15, узел 16

эо

управления, формирователь 17 импульса пуска и элемент И 18.

В состав каждого блока 6 присвоения адреса входят три элемента ИЛИ 19-21, подключенные к сдвиговому регистру 22, счетчик 23 адреса, элемент И 24, элемент И-НЕ 25 и передатчик (транслятор) 26.

На чертежах показаны линии 27-43 связи между элементами устройства.

Формирователь 10 импульсов сброса (фиг.6) содержит магистральный передатчик 44, первый элемент задержки, состоящей из диода 45, резистора 46 и конденсатора 47, элемент И 48, второй элемент задержки, состоящий из диода 49, резистора 50 и конденсатора 51, и элемент И 52.

Триггер 16 управления (фиг.7) имеет два элемента НЕ 53 и 54, элементы И-НЕ 55 и 56, элемент И 57 и RS-триг- гер 58.

Интегратор 16 (фиг.8) содержит диод 59, резистор 60, конденсатор 61 и элемент И-НЕ 62.

Сдвиговый регистр 22 (фиг.9) состоит из элемента НЕ 63 и триггеров 64.1-64.К. Устройство работает следующим образом.

При включении питания на схеме 4 появляется высокий уровень. Этот сигнал запускает формирователь 10, который выдает отрицательные импульсы одновременно на тактовую линию 5(29) и линию 28 начальной установки. Эти сигналы воздействуют на элементы ИЛИ 19 всех блоков 6, на выходах которых появляются низкие уровни, устанавливающие в состояние 1 все триггеры сдвиговых регистров 22 и обнуляют все счетчики 23.

При этом на инвертирующих выходах всех регистров 22 устанавливаются низкие уровни, а на неинвертирующих - высокие уровни. Высокий уровень с неинвертирующего выхода запрещает работу передатчиков 26 и разрешает работу элементов И-НЕ 25 и элементов И 24. Сигнал с инвертирующего выхода открывает элементы ИЛИ 20 и они выдают низкий уровень на вторую информационную линию 32. В блоке 3 в это время триггер 11 устанавливается в единичное состояние выходным сигналом элемента И 18 по низкому уровню на линии 28 по этому же сигналу обнуляется триггер 16. Кроме того,

0

5

0

5

0

5

0

5

счетчик 12 обнуляется выходным сигналом формирователя 10, поступающими на линию 29. Длительность импульсов, выдаваемых формирователем 10, должна обеспечивать надежное приведение всех схем блоков 6 в исходное состояние. Практически это,время должно быть не меньше времени распространения сигнала по магистрали до последнего блока 6, что для магистрали длиной 100 м, учитывая, что задержка сигналов равна 10 нс/м, составляет 1 мкс. По окончании необходимого промежутка времени формирователь 10 снимает сигналы с магистрали 2 и тактовой линии 5 (линии 28 и 29).

На выходах всех элементов И-НЕ 25 появляется низкий уровень, а на выходах элементов ИЛИ 20 - высокий. Эти сигналы также начинают распространяться по магистрали 2, поэтому для более надежной работы устройства не- ,обходимо положительный перепад, кото- рый поступает с формирователя 10 по линии 30 на вход триггера 11 после окончаний выдачи установочных сигналов, задержать примерно на 1 мкс. Все магистральные линии совместно с передатчиками образуют схему ВОДНОЕ ИЛИ, т.е. высокий уровень по этой линии появляется только тогда, когда все передатчики, соединенные с ней, установлены в состояние, выдачи высокого уровня.

Таким образом, процесс начальной установки заканчивается состоянием, когда все передатчики 26 закрыты, элементы ИЛИ 20, И-НЕ 25 и 24 открыты, на тактовой линии 5 - высокий уровень, на линии 9 - высокий уровень, триггер 11 находится в единичном состоянии, счетчик 12 обнулен. Начало процесса адресации периферийных устройств 8 инициируется положительным перепадом, поступающим на триггер 11 с формирователя 10 с соответствующей задержкой (относительно снятия сигналов с тактовой 29 и установочной 28 линий магистрали 2). При этом триггер 11 обнуляется и открывает высоким уровнем с инверсного выхода элемент И-НЕ 14, а также разрешает работу интегратора 15 и счетчика 12. С неинвертирующего выхода триггера 11 на линию 9 выдается низкий уровень. Блоки 3 и 6 начинают вырабатывать импульсы на тактовую линию 5.

В процессе генерации тактовых импульсов принимают участие элементы И-НЕ 14, триггер 16, элементы Й-НЕ 25 и ИЛИ 20, При этом вначале на входы элемента И-НЕ 14 с выходов триггера 16 и триггера 11 поступает разрешающие сигналы(с высоким уровнем), что приводит к появлению на линии 29 сигнала низкого уровня, который рас-, пространяясь по линии 5, запрещает работу ранее открытых элементов И-НЕ 25, разрешая работу элементов ИЛИ 20. После того, как сигнал с линии 5 открывает элемент ИЛИ 20 (он ближе . всех), на линии 32 устанавливается низкий уровень. Элемент И-НЕ 25-1 закрывается , однако на линии 33 имеется низкий уровень до тех пор, пока не закроется последний элемент И-НЕ 25-п.

Таким образом, на первой информационной линии 33 магистрали 2 устаПосле обнуления триггера 11 сигнал по линии 31 низким уровнем поступает на вход первого блока 6rl и закрывает элемент И 24 1 так, что на входе счетчика 23-1 устанавливается

30

35

навливается высокий уровень, а на линии 32 - низкий (только после того, 25 низкий уровень, по которому состоя- как тактовый сигнал достигнет послед- ние счетчика 23-1 не изменяется (он

реагирует на положительный перепад). Содержимое счетчика остается нулевым, поскольку сигнал на линии 31 имеет низкий уровень на протяжении всего цикла адресации перифё рийных устройств 8. Счетчики 23-2- 23-п воспринимают тактовые импульсы, поскольку элементы И 24 2-24-п открыты. Одновременно происходит сдвиг нулевой информации в регистре 22-1- так как элемент ИЛИ открыт низким уровнем на линии 31. В то же t время элементы ИЛИ 21-2-21-п закрыты затем, когда сигнал достигает послед- 4о высокими уровнями, поскольку трансля- него блока 6-n, H.B. которого Обратно Т°РЫ 26 закрыты. Сдвиг информации в

регистре 22 должен производиться по отрицательному перепаду на его входе, что обеспечивает режим работы схем - адресации с повышенной помехоустойчивостью. Если это условие соблюдено, то информация на выходе соответствующего регистра 22 -К появляется, когда на тактовой линии 5 устанавливается низкий уровень, закрывающий элемент И 24 - (К + 1), т.е. сигнал, поступающий низким уровнем по линиям 9 после переключения последнего триггера сдвигового регистра 22-К лишь подтверждает состояние элемента И 24 и

него из блоков 6-п). По состоянию В.Н. (первая буква означает уровень напряжения на первой информационной линии 33 магистрали 2 (высокий), а вторая - на второй информационной линии 32 (низкий) триггер 16 переходит в состояние запрета работы элемента И-НЕ 14, что приводит к появлению высокого уровня на линии 5, который, распространяясь, закрывает элемент ИЛИ 20 и разрешает работу- элементов И-НЕ 25. При этом сначала устанавливается состояние Н.Н., а

исходному. Состояние Н.В. первой 33 и второй 32 информационных линий передачи переводит триггер 16 в состояние разрешения работы элемента И-НЕ 14 с выдачей на линию 5 низкого уровня. Это приводит сначала к появлению состояния Н.Н., а затем В.Н., которое переводит триггер 15 в состояние запрета работы элемента И-НЕ 14.

Так происходит выработка последовательности импульсов на тактовой линии 5, причем частота следования этих импульсов определяется параметрами самого устройства, такими, как длина магистрали 2 и быстродействие элементной базы, на которой оно построе но. Очевидно, что частота импульсов автоматически поддерживается на

50

55

закрывает этот элемент до следующего цикла адресации периферийных устройств 8, инициируемого из узла 4. Если же переключение триггеров регисимально высоком уровне и изменяется с изменением, например длины магистрали 2. С другой стороны тактовые сигналы воспринимаются всеми блоками

6, так как в формировании их принимает участие самый удаленный блок 6. В устройстве квитирование осуществляется по двум фронтам тактового

0 импульса, причем нет необходимости в установке на магистраль специаль- ных заглушек, формирующих временную диаграмму, что также является одним i из факторов, обеспечивающих достиже5 ние относительной конструктивной простоты предлагаемого устройства.

Теперь рассмотрим собственно процесс присвоения адресов периферийным устройствам (фиг.5).

После обнуления триггера 11 сигнал по линии 31 низким уровнем поступает на вход первого блока 6rl и закрывает элемент И 24 1 так, что на входе счетчика 23-1 устанавливается

5 низкий уровень, по которому состоя- ние счетчика 23-1 не изменяется (он

30

4о

35

4о

45

50

регистре 22 должен производиться по отрицательному перепаду на его входе что обеспечивает режим работы схем - адресации с повышенной помехоустойчивостью. Если это условие соблюдено то информация на выходе соответствующего регистра 22 -К появляется, когда на тактовой линии 5 устанавливается низкий уровень, закрывающий элемент И 24 - (К + 1), т.е. сигнал, поступающий низким уровнем по линиям 9 после переключения последнего триггера сдвигового регистра 22-К лишь подтверждает состояние элемента И 24 и

5

закрывает этот элемент до следующего цикла адресации периферийных устройств 8, инициируемого из узла 4. Если же переключение триггеров реги71476

стров 22 происходит по положительному перепаду, то низкий уровень устанавливается на линии 9 и входе элемента 24-(К + 1) уже после того, как появился высокий уровень на его тактовом входе, т.е. возможно ложное срабатывание счетчика 23-(К + 1) от короткого импульса, что связано с тем, что приблизительно одновременно на входах элемента 24-(К + 1) имеется как положительный (тактовый вход) так и отрицательный, (цепочечный вход) перепады напряжений.

Исходя из приведенного можно так- же определить количество триггеров в регистре 22-К, например, одноадресного устройства. В этом случае це- почечный сигнал в линии 9 должен задер- жаться на один такт, чтобы в счетчик 23-(К + 1) записалась на единицу большая информация, чем в счетчик 23-К перед тем, как его вход отключится от тактовой линии 5 сигналом на цепочечной линии 9. В соответствиии с вре- менной диаграммой (фиг.5) для этого необходимо иметь в составе сдвигового регистра 22-К два триггера. При необходимости присваивать два адреса регистр должен состоять из трех триггеров, трех адресов и т.д. Очевидно, что если периферийное устройство 8 занимает N адресов, то его сдвиговый регистр 22 должен содержать N+1 триггер. Цепочечный сигнал слу- жит для управления элементами ИЛИ 20 и И-НЕ 25. Вначале на линии имеется высокий уровень, который разрешает работу всех счетчиков 23. Блокирует- ,ся только вход первого счетчика (с неинвертирующего выхода триггера 11). Работа всех сдвиговых регистров 22 этим уровнем запрещена. Разрешена работа только сдвигового регистра Л 22-1. По его заполнении с инвертирующего выхода (высоким уровнем) запрещается работа элемента ИЛИ 20-1, а с неинвертирующего (низким уровнем) запрещается работа элемента И-НЕ и блокируется элемент И 24-1. Даже если на линии 31 появляется высокий уровень, счетчик адреса 23-1 заблокирован. Данный процесс распространяется от одного блока 6-К к другому 6(К + 1), блокируя в соответствую- щие моменты счетчик 23-К. Если рассмотреть этот процесс в общем, то на тактовой линии 5 существуют импульсы с соответствующей частотой, которые

8

воздействуют на счетчики 23 до тех пор, пока не появится низкий уровень на цепочечном входе, который блокирует счетчики и разрешает работу соответствующего сдвигового регистра , по заполнении которого цепочечный сигнал транслируется на следующий блок 6-(К + 1), а элементы данного блока ИЛИ 20 и И-НЕ 25-К блокируются, т.е. запрещается выдача ими сигналов на информационные линии 33 и 32 магистрали 2 (эквивалентно выдаче высокого уровня на обе линии). Это значит, что блок 6-К, соответствующий адресному периферийному устройству 8-К, полностью блокируется. Повторный запуск его возможен только по сигналам с формирователя 10, т.е. только при повторном запуске процессора 1.

В это время интегратор 15, работа которого разрешена триггером 11, анализирует выходной сигнал триггера 16 так, что на его выходе появляется низкий уровень, если на входе достаточно долго находится высокий уровень (ситуация, которая возникает, когда все периферийные устройства 8 адресованы, т.е. заблокированы все элементы ИЛИ 20 и И-НЕ 25). В результате на линиях 33 и 32 появляется состояние В.В., которое не может перевести триггер 16 в состояние запрета выдачи тактового сигнала и на выходе триггера 16 достаточно долге существует высокий уровень. Выдержка времени, обеспечиваемая интегратором 15, должна быть того же порядка, что и длительность сигналов, выдаваемых формирователем 10 на тактовую линию 5 и линию начальной установки. По низкому уровню с выхода интегратора 15 триггер И устанавливается в единичное состояние, снимая низкий уровень с цепочечной 9 и тактовой 5 линий. Одновременно выходной сигнал интегратора 15 переводит формирователь 17 в состояние разрешения работы процессора 1, который начинае работу с уже адресованными периферийными устройствами 8. При необходимости процессор 1 может проверить размеры адресной области, распределенной между периферийными устройствами 8. Для этого он читает информацию из счетчика 12, обращаясь по адресу, занятому в селекторе 13, по выходном сигналу которого происходит выдача

содержимого счетчика 12 в магистрали 2 процессора.

Адрес, который присваивается селектору 13, может быть любым из области адресов периферийных устройств, он назначается разработчиком данного устройства. Содержимое счетчика 12, работа которого разрешается в тот интервал времени, когда триггер 11 об- нулей, соответствует общему количеству синхроимпульсов, передавшихся по ч тактовой линии 5 за весь период адре-г сации всех периферийных устройств 8, т.е. равно количеству адресов, заня- тых всеми периферийными устройства- |Ми 8. Сравнивая содержимое счетчика 12 с эталоном, процессор может либо проверять наличие необходимого количества периферийных устройств 8, ли- бо, если программное обеспечение рассчитано на обслуживание нескольких типов вычислительных устройств с различной периферией, настраиваться на конкретную модификацию данного уст- ройства.

Интегратор 15 работает следующим образом. Если его работа разрешена с инверсного выхода триггера 11 (высорезультате чего интегратор 15 срабатывает.

Формирователь 10 работает следующим образом.

В исходном состоянии на его входе 27, подключенном к выходу узла 4tприсутствует низкий уровень, на выходе 30 - также низкий уровень. При появлении на входе 27 формирователя 10 высокого уровня на выходе магистральных передатчиков 44 появляются низкие уровни, поскольку на входе выборки кристалла, соединенного с выходом элемента И 48, также имеется низкий уровень. По достижении напря жением на конденсаторе 47 порога срабатывания элемента И 48, на его выходе появляется высокий уровень, который блокирует магистральные передатчики 44, и далее с задержкой, определяемой резистором 50 и конденса- тором 51, появляется на выходе 30 формирователя 10.

Триггер 16 работает следующим образом.

В момент начального запуска триггер 58 обнуляется по входу 28 через элемент И 57. При работе на его вы

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для подключения абонентов к магистрали ЭВМ | 1987 |

|

SU1444795A1 |

| УСТРОЙСТВО ДЛЯ СИНТЕЗА РЕЧЕВЫХ СИГНАЛОВ | 1991 |

|

RU2020608C1 |

| Устройство управления доступом к системной магистрали в двухпроцессорной системе | 1987 |

|

SU1456966A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ ПО ДВУХПРОВОДНОЙ ЛИНИИ СВЯЗИ | 1991 |

|

RU2023310C1 |

| Оптикоэлектронный координатор для автоматического вождения мобильных агрегатов | 1986 |

|

SU1378086A1 |

| Многоканальное устройство для сбора данных | 1983 |

|

SU1095163A1 |

| Устройство для приема и передачи информации | 1986 |

|

SU1378076A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

Изобретение относится к вычислительной технике и позволяет производить автоматическое аппаратное присвоение адресов периферийным устройствам. Устройство позволяет минимизировать аппаратные затраты на адресацию, повысить быстродействие и помехоустойчивость адресации, присваивать периферийным устройствам индивидуальную область адресов. Это обеспечивается тем, что в устройство, содержащее блок управления адресацией, включающий в себя триггеры опроса и управления, формирователь импульсов, счетчик и элемент И, и N блоков присвоения адреса, каждый из которых состоит из элемента ИЛИ, счетчика адреса, регистра сдвига, элемента И и передатчика, введены в блок управления адресацией селектор адреса, формирователь импульса пучка, элемент И и интегратор, а в каждый блок присвоения адреса - два элемента ИЛИ и элемент И-НЕ. 9 ил.

кий уровень), то по появлении высоко-30 ходе 37 устанавливается высокий урого уровня на выходе триггера 16 начинает заряжаться конденсатор 61. Если было адресовано не последнее периферийное устройство 8, то через соответствующий промежуток времени на 58).Низкий уровень на выходе 37 походе триггера 16 устанавливается низкий уровень, который через диод 59 быстро разряжает конденсатор 61. Если же адресовано последнее периферийное устройство 8, то на информационных линиях 33 и 32 не устанавливается состояние, необходимое для запрета выдачи тактового сигнала, так как все элементы ИЛИ 20 и И-НЕ 25 отклюявляется и если на первой и второй линиях 33 и 32 присутствуют соответственно высокий и низкий уровни. Промежуточные состояния (оба высоких 40 или оба низких) на триггер 58 не воздействуют.

При конкретной реализации устройства в качестве процессора 1 можн использовать, например, стандартт

чены от магистрали 2. На тактовой процессор ЭВМ Электроника-60,. отнии 5 в конце цикла адресации периферийных устройств 8 имеется низкий уровень, поскольку переключение регистров 22 происходит по переходу сигнала на тактовой линии 5 из высокого уровня в низкий, и, таким образом, запрещающие сигналы с выходов регистра 22 вырабатываются в момент установления низкого уровня на тактовой линии 5.

Таким образом, в конце цикла адресации на выходе триггера 16 достаточно долго остается высокий уровень, в

50

55

ключив от него схему начального запуска и соединив ее с соответствующим входом блока управления адресацией, селектор адреса 13 - также стандартный от любого адресного периферийного устройства ЭВМ Электроника-60, запрограммированный на дешифрацию соответствующего адреса.

Формула изобретения

Устройство для подключения абонен тов к магистрали ЭВМ, содержащее блок управления адресацией, включаю

вень, если на первой информационной линии 33 магистрали 2 имеется низкий уровень, а на второй 32 - высокий (низкий - на входе сброса триггера v

является и если на первой и второй линиях 33 и 32 присутствуют соответственно высокий и низкий уровни. Промежуточные состояния (оба высоких или оба низких) на триггер 58 не воздействуют.

При конкретной реализации устройства в качестве процессора 1 можн использовать, например, стандартт

ключив от него схему начального запуска и соединив ее с соответствующим входом блока управления адресацией, селектор адреса 13 - также стандартный от любого адресного периферийного устройства ЭВМ Электроника-60, запрограммированный на дешифрацию соответствующего адреса.

Формула изобретения

Устройство для подключения абонентов к магистрали ЭВМ, содержащее блок управления адресацией, включаю

щий формирователь импульсов, счет- . чик, триггер управления, элемент И и триггер опроса, соединенный синхро- входом с выходом расширенного импульса формирователя импульсов, и п блоков присвоения адресса, каждый из которых включает сдвиговый регистр, передатчик, счетчик адреса, первый элемент ИЛИ и элемент И, выходом соединенный со счетным входом счетчика адреса, первым входом - с первым входом первого элемента ИЛИ и тактовым входом блока присвоения адреса, а вторым входом - с входом опроса блока присвоения адреса и информационным входом передатчика, причем тактовый выход блока управления адресацией соединен с тактовыми входами блоков присвоения адреса, а выход опроса - с входом опроса первого блока присвоения адреса, выход опроса i-го блока присвоения адреса (i 2.п) соединен с выходом опроса (i-l)-ro блока присвоения адреса, в блоке управления адресацией выход серии импульсов формирователяvимпульсов является тактовым выходом блока, а вход пуска является входом запуска . устройства, отличающееся тем, что, с целью сокращения аппара- 1 турных затрат устройства, в блоке управления адресацией введены формирователь импульса пуска, селектор адреса, элемент И-НЕ и интегратор, а в каждый блок присвоения адреса - второй и третий элементы ИЛИ и элемент И-НЕ, причем разрешающий и информационный входы блока управления адресацией являются соответствующими входами устройства для подключения к разрешающему выходу процессора и информационной шине магистрали, а выход начальной установки блока управления адресацией соединен с входами начальной установки блоков присвоения адреса, выходы которых являются выходами устройства для подключения к адресным входам соответствующих абонентов, первый и второй выходы состояния блоков присвоения адресов соединены соответственно с первой и второй линиями информационной шины магистрали, причем в блоке управления адресацией пусковой вход формирователя импульса пуска соединен с входом запуска уст- ройства, а вход разрешения - с входом разрешения блока управления адресацией, выход начальной установки фор

0

5

0

5

0

5

0

5

мирователя импульса соединен с выходом начальной установки блока управления адресацией, входом сброса триггера управления и первым входом , элемента И, второй вход которого подключен к выходам формирователя импульса пуска и интегратора, а выход - к входу установки триггера опроса, соединенного прямым выходом с выходом опроса блока управления адресацией, а инверсным - с разрешающим входом интегратора и первым входом элемента И-НЕ, информационный вход триггера соединен с шиной нулевого потенциала блока управления адресацией, выход триггера управления подключен к пусковому входу интегратора и второму входу элемента И-НЕ, выход которого и выход серии импульсов формирователя импульсов соединен с тактовым выходом блока управления адресацией и входом сброса счетчика, разрешающим и счетным входами соединенного соответственно с выходом селектора адреса и выходом расширенного импульса формирователя импульсов, а выходом - к разрешающему входу интегратора и первому входу элемента И-НЕ, информационный вход счетчика, вход селектора адреса и установочные входы триггера управления соединены с информационным входом блока управления адресацией, причем в каждом блоке присвоения адресов второй вход первого элемента ИЛИ соединен с входом начальной установки блока присвоения адресов, а выход - с входами сброса сдвигового регистра и счетчика адреса, выходом соединенного с информационным выходом блока присвоения адресов, выходы элемента И-НЕ и второго элемента ИЛИ являются соответственно первым и вторым выходами состояния блока присвоения адресов, первые входы соединены с тактовым входом блока присвоения адреса, а вторые входы - соответственно с прямым и инверсным выходами регистра сдвига, тактовым входом подключенного к выходу третьего элемента ИЛИ, первый и второй входы которого подключены соответственно к тактовому входу и входу опроса блока присвоения адресов, третий вход элемента И соединен с прямым выходом регистра сдвига и управляющим входом передатчика, выход которого соединен с выходом опроса блока присвоения адресов .

oo

t

sD p- T

I

27

28 Л9

И

Фиг.5

Фиг.6

я

53

32

36

55

57

Фиг. 7

Фиг.8

| Селектор адреса кассеты ввода-вывода | 1984 |

|

SU1226439A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для подключения абонентов к магистрали электронной вычислительной машины | 1984 |

|

SU1238096A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-04-30—Публикация

1987-05-14—Подача