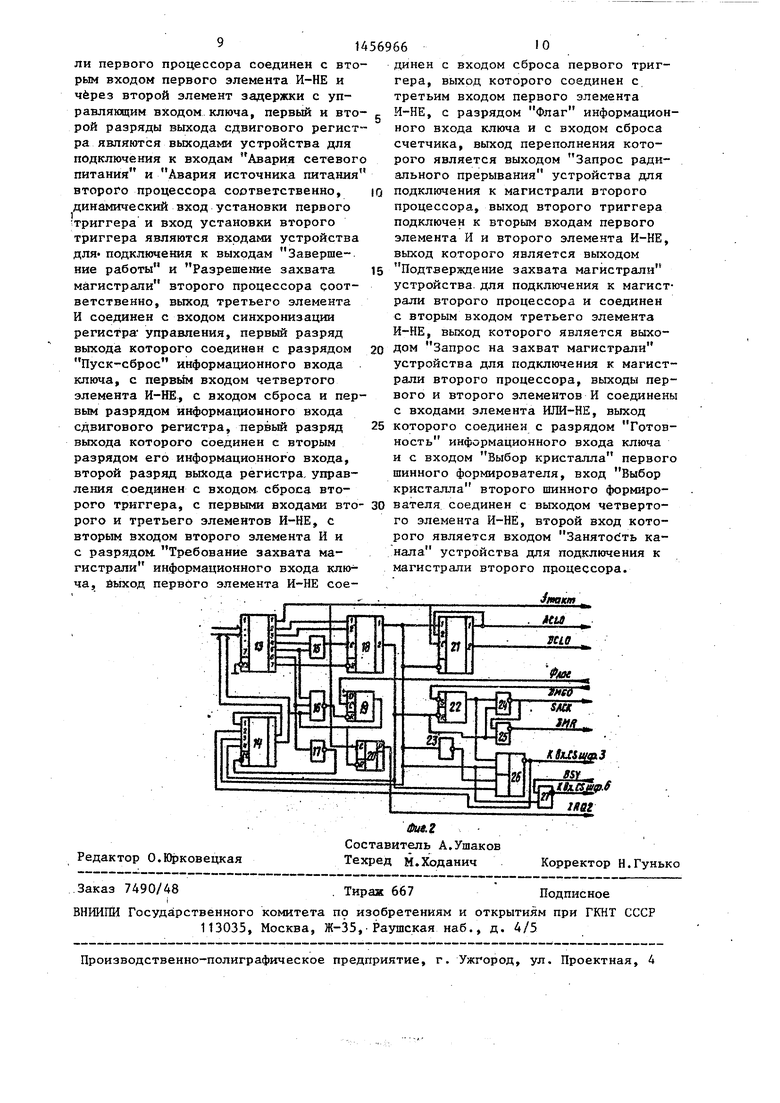

рователь 13, ключ 14, вьтолненный на шинном формирователе, элемент И 15, элемент И-НЕ 16, элемент НЕ 17, регистр 18 управления, триггер 19, счетчик 20, сдвиговый регистр 21, триггер 22, элемент НЕ 23, элементы И-НЕ 24 и 25, два элемента И и элемент ИЛИ-НЕ, выполненные в виде элемента 2Й-ИЛИ-НЕ 26, и элемент И--НЕ27. .Устройство работает следукнцим образом.

Центральный процессор 1 при включении питания по магистрали 2 (в состав которой входят шины адреса данных и управлякщих сигналов) вьфа- батывает сигнал начальной установки, который поступает через шинный формирователь 13 на вход сброса регистра 18 управления и устанавливает его в исходное состояние. Сигналом низкого уровня с выходов первого и второго разрядов регистра 18 управления устанавливаются в исходное состояние сдвговый регистр 21 и триггер 22. Сдвиговый регистр 21 приводит в исходное состояние периферийньй процессор 5. Шинные формирователи 3 и 6 закрыты. Процедура обмена данными по магистралям 2 и 11 соответствует процедуре обмена по магистрали Элект- роника-60.

Для контроля состояния процессора 5 и схемы заЬсвата магистрали в устростве 4 процессор 1 выставляет сигнал

0

5

0

5

0

5

26. На втором входе второго элемен- /та И элемента 2Й-ИЛИ-НЕ 26 - высокий уровень напряжения, который поступает с,выхода второго разряда регистра 18 управления. На выходе элемента 2И-И11И-НЕ 26 - низкий уровень напряжения , который открывает первый шинный формирователь 3 и как сигнал Готовность поступает на соответст- вукяций разряд ключа 14.

Наличие сигнала Готовность на выходе ключа 14 свидетельствует о завершении процедуры захвата магистрали со стороны центрального процессора 1.

При получении сигнала Готовность центральный процессор 1 по магистрали 2 через открытый первый шинный формирователь 3 и магистраль 11 производит загрузку программного обеспечения, необходимого для функционирования периферийного процессора 5, в блок 7 оперативной памяти.

Блок 7 оперативной памяти предназначен для хранения программ теста включения периферийного процессора 5, опроса датчиков, вьщачи управляющих воздействий к исполнительным устройствам, для формирования файлов данных для передачи в центральный процессор 1, для хранения файлов данных, получаемых от центрального процессора 1,;Для передачи их к исполнительным устройствам, аварийного выключения технологического оборудования.

По окончании записи данных в блок 7 оперативной памяти центральный процессор снимает Требование захвата магистрали и выставляет сигнал Пуск на запуск периферийного .процессора 5. На выходах первого и второго разрядов регистра 18 управ- ления - высокий и низкий уровни соответственно.

Сдвиговый регистр 21 служит для формирования процедуры начального пуска периферийного процессора 5, триггер 22, элемент НЕ 23, элементы И-НЕ 24 и 25 и элемент 2И-ИЛИ-НЕ 26 служат для формирования сигналов захвата магистрали 11 центральным процессором 1 при работающем пери- ферийном процессоре 5.

Запуск периферийного процессора 5 производится следующим образом.

При поступлении на вход синхронизации сдвигового регистра 21 поло- жительного- фронта синхрочастоты в первый разряд сдвигового регистра 21 с выхода первого разряда регистра 18 управления записывается высокий урозахватывает внешнюю магистраль 11 следующим образом.

Центральный процессор 1 записывает во второй разряд регистра 18 управления сигнал высокого уровня, что является сигналом Требование захвата магистрали центральным процессором 1. Триггер 22 установлен в нулевое состояние, на выходе элемента И-НЕ 25 - высокий уровень, на вьпсоде элемента 2И-ИЛИ-НЕ 26 - высокий уровень, первый шинный формирователь 3 закрыт.

При поступлении на вход элемента И-НЕ 25 вусокого уровня на его выходе - низкий уровень. Выход элемента И-НЕ 25 соединен с входом Запрос на захват магистрали (DMR) периферийного процессора 5, выход элемента И-НЕ 24 соединен с входом Подтверждение захвата магистрали $АСК ) процессора 5, вход установки тригге- ра 22 соединен с выходом Разрешение на захват магистрали (DMGO) процес- . сора 5.

При поступлении на вход DMR периферийного процессора 5 сигнала низкого уровня периферийный процессор 5 выставляет сигнал DMGO низкого уров-

| название | год | авторы | номер документа |

|---|---|---|---|

| Распределенная система управления | 1989 |

|

SU1732345A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1987 |

|

SU1432580A1 |

| Процессор для мультипроцессорной системы | 1988 |

|

SU1541626A1 |

| Устройство для сопряжения процессоров в однородной вычислительной системе | 1984 |

|

SU1273940A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕГЕНЕРАЦИЕЙ В ПОЛУПРОВОДНИКОВОМ ДИНАМИЧЕСКОМ ЗАПОМИНАЮЩЕМ УСТРОЙСТВЕ | 1994 |

|

RU2040808C1 |

| ДИСПЛЕЙ | 1990 |

|

RU2015536C1 |

| УСТРОЙСТВО ДЛЯ СБОРА, ОБРАБОТКИ И ПАКЕТНОЙ ПЕРЕДАЧИ РЕЗУЛЬТАТОВ ИЗМЕРЕНИЯ ПАРАМЕТРОВ ФИЗИЧЕСКОЙ СРЕДЫ | 1994 |

|

RU2080653C1 |

| АДАПТИВНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2477882C2 |

| УСТРОЙСТВО ДЛЯ СБОРА, ОБРАБОТКИ И ПАКЕТНОЙ ПЕРЕДАЧИ РЕЗУЛЬТАТОВ ИЗМЕРЕНИЯ ПАРАМЕТРОВ ФИЗИЧЕСКОЙ СРЕДЫ | 1994 |

|

RU2079881C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

Изобретение относится к вычислительной технике и позволяет повысить надежность вычислительной системы за счет перераспределения функций управления при отказе одного из процессоров. Периферийный процессор 5 служит для опроса датчиков, подготовки данных для передачи в центральный процессор 1, выдачи управляющих воздействий к исполнительным устройствам. Периферийный процессор 5 по окончании определенного участка про- граммы записывает данные в блок 7 .оперативной памяти и выставляет сиг-- нал Флаг,по получении которого центрапьньй процессор 1 захватывает внешнюю магистраль 11 и производит обмен данными. Работоспособность процессоров контролируется с помощью счетчиков времени. В случае откааа периферийного процессора 5 централь- ньй процессор 1 блокирует периферийный процессор 5 и производит опрос датчиков и выдачу управляющих воздействий на исполнительные устройства. В случае отказа центрального процессора 1 периферийный процессор 5 производит аврийное выключение технологического оборудования. 2 ил. S (Л с:

вень. При поступлении на вход синхро- зо и по входу установки устанавливанизации следующего положительногоет триггер 22 в единичное состояние. фронта синхрочастоты во второй раз- На выходе элемента И-НЕ 24 форми|ряд сдвигового регистра 21 записыва-руется сигнал SACK низкого уровня.

ется высокий уровень с выхода первого разряда сдвигового регистра 21. Вы- Лоды первого и второго разрядов сдвигового регистра 21 соединены с входами Авария сетевого питания (ACLO) и Авария источника питания (DCLO) периферийного процессора 5. Последовательная выдача сигналов ACLO и DCLO высоким уровнем приводит к запуску.периферийного процессора 5. При поступлении на вход сброса сдвигового регистра 21 низкого уров-) ня, т.е. выдаче сигнала Сброс от центрального процессора 1, сдвиговый регистр 21- обнуляется.

При поступлении на входы ACLO и DCLO сигналов низкого уровня периферийный процессор 5 устанавливается в исходное состояние.

Центральный процессор 1 может захватить магистраль 11 как при неработающем, так и работающем периферийном процессоре 5. ,

При работающем периферийном процессоре 5 центральный процессор t

35

45

Появление сигнала SACK сообщает периферийному процессору 5 о захвате магистрали 11 центральным процессором 1. На выходе элемента 2И-ИЛИ-НЕ 26 - низкий уровень, поступающий ка сигнал Готовность на соответствую Q .щий вход ключа t4, первьш шинный фор Емирователь 3 открыт.

Появление сигнала Готовность на выходе ключа 14 свидетельствует о завершении процедуры захвата магистрали 11 со стороны центрального процессора 1 и возможности обмена данными между центральным процессором 1 и устройствами, подключенными к магистрали 11 через открытый шинный формирователь 3.

Периферийный процессор 5 может захватить внешнюю магистраль 11 выдачей сигнала Занятость канала (BSY), которьй поступает высоким 55 уровнем на второй вход элемента И-НЕ 27, выход которого соединен с входом Выбор кристалла второго шинного формирователя 6. Периферийный процессор 5 может захватить ма50

гистраль 11 при отсутствии сигналов ВЖ и SACK. Кроме того, при сбросе периферийного процессора 5 возможность захвата магистрали периферийным процессором 5 блокируется вьща- чей сигнала низкого уровня с выхода первого разряда регистра 18 управления, поступающего на первый вход третьего элемента И-НЕ 27..

Периферийный процессор 5 при снятии сигналов DMK и SACK выставляет сигнал BSY, открывает второй шинный формирователь 6 и считывает с блока 7 оперативной паз4яти данные, необходимые для вьшолнения очередного участка программы.

Периферийный процессор 5 работае по тактам, временные хар актеристики которых определяются кодом уставки, периодически заносимой периферийным процессором 5 в таймер 8.

В случае успешного прохождения определенного участка программы периферийный процессор 5 записывает в регистр 9 адреса зарйнее выбранный код. Этот код, преобразованный дешифратором 10 адреса в импульс поло жительной полярности, поступает на динамический вход установки триггера 19 и устанавливает его в единичное состояние. Сигнал высокого уровня с выхода триггера 19 поступает как сигнал Флаг на соответствующий вход ключа 1А. Центральный процессор 1 считывает по магистрали 2 сигнал Флаг. Выдача сигнала Флаг от периферийного процессора 5 свидетельствует об успешном оконопределенного участка програм- о оперативной памяти.

Центральш проц полученшле данные, з раль 11 и записывае тивной памяти дашм равляющих воздейств

мы.

Сброс сигнала Флаг производится при вьщаче сигналов Выбор устройст- ва и Вывод от центрального процессора 1 высоким уровнем. На первый и второй входы элемента И-НЕ 16 поступают сигналы Выбор устройства и ; Вьюод, и если триггер 19 установлен в единичное состояние, то на всех трех входах элемента Й-НЕ 16 - высокий уровень,на его Ъыходе - низки уровень и триггер 19 по входу сброса устанавливается в нулевое состояние, т.е. сбрасывается сигнал Флаг.

При получении сигнала Флаг от периферийного процессора 5 и необходимости обмена данными с блоком 7 оперативной памяти центральный .процессор 1 производит захват магистра

5

ли 11 и обмен данными с блоком 7 оперативной памяти. По окончании обмена данными центральный процессор 1 снимает сигнал. Требование захвата магистрали приводит схему захвата магистрали (триггер 22, элементыИ-НЕ 24 и 25) в исходное состояние.

В блоке 7 оперативной памяти хранятся программы опроса датчиков, обработки данных, вьщачи управляющих воздействий и т.д. Для опроса датчиков периферийный процессор 5 считавает соответствующую программу с блока 7 оперативной памяти и по магистрали 11 записывает в регистр 9 адреса код , адреса датчика. Этот код, преобразо- ванный дешифратором 10 адреса, через блок 12 согласования поступает к датчикам.

Блок 12 согласования предназначен для согласования уровней сигналов, поступающих по магистрали 11 к датчит, кам и исполнительным устройствам и 5 обратно, и сигналов, поступакшщх с выхода дешифратора 10 адреса.

о состоянии датчиков списываются периферийным процессором 5 и записываются в блок 7 оперативной памяти. По окончании опроса датчиков периферийный процессор 5 обрабатывает полученные данные, производит формирование файла данных для последукнцей передачи в центральный процессор 1 и выставляет сигнал Флаг. При получении этого сигнала центральный процессор 1 захватывает магистраль 11 и считывает данные, подготовленные периферийным процессором 5 в блоке 7

0

0

5

о оперативной памяти.

5

Центральш процессор 1, обработав полученшле данные, захватывает магист-. раль 11 и записывает в блок 7 оперативной памяти дашме для выдачи управляющих воздействий. ,

По окончании записи данных цент- ралышм процессором 1 периферийный процессор 5 считывает с блока 7 опег- ративной памяти дашше ввдачи управ- ляняцих воздействий, обрабатывает их и, адресуя при помощи регистра 9 адреса и дешифратора 10 адреса исполнительные устройства, выдает по магистрали 11 к .исполнительным устрой- jcTsaM необходимые команды.

Затем цикл опроса датчиков, подготовки данных, вычисление .управляющих воздействий и,их вьщачи к исполнительным устройствам повторяется.

О

Центральный процессор 1 контролирует работоспособность периферийного процессора 5 с помощью собственного счетчика времени. -Если периферийный процессор 5 не выставляет сигнал Флаг за определенное время, то центральный процессор 1 захватывает магис1;раль 11 и при наличии сигнала

Формула изобретени

Устройство управления доступом к .системной магистрали в двухпроце сорной системе, содержащее два двунаправленных шинных формировате блок управления доступом и блок оп ративной памяти, вход-выход обмена

Готовность от периферийного процес- ю которого соединен через системную

сора 5 производит перезапуск выполнявшейся задачи.

Готов-. неис

При отсутствии сигнала ность, что свидетельствует о правности периферийного процессора 5, центральный процессор 1 выдает , сигнал Сброс записью низкого уровня в первый разряд регистра 18 управления и захватывает магистраль 11, так как на входах второго элемента И элемента 2И-ИЛИ-НЕ 26 - вы- сокий уровень.

При отказе периферийного процессора 5 центральный процессор 1 принимает на себя функции опроса датчиков и вьщачи управляющих воздействий к исполнительным устройствам, так как процедуры обмена по системной магистрали 2 и магистрали 11 оди наковы.

Периферийный процессор 5 контролирует работоспособность центрального процессора 1 при помощи счетчика 20,. который запускается при установке сигнала Флаг от периферийного процессора 5. Счетчик 20 приводится в состояние при сбросе сигнала Флаг центральным процессором 1, т.-е. установке триггера 19 в нулевое состояние. Емкость счетчика 20 устанавливается на максимально допустимое время ответа центральным процессором 1 ,на сигнал Флаг.

Если центральный процессор 1 за определенное время не сбросит сигнал Флаг в устройстве А управления, то счетчик 20 переполняется и импульс переполнения отрицательной полярности поступает на вход Запрос радиального прерывания периферийного цессора 5. По получении этого прерывания периферийный процессор 5 пе реходит на вьтолнение программы аварийного выключения технологического оборудования с выдачей сообщения об отказе процессора на пульт оператора

Формула изобретения

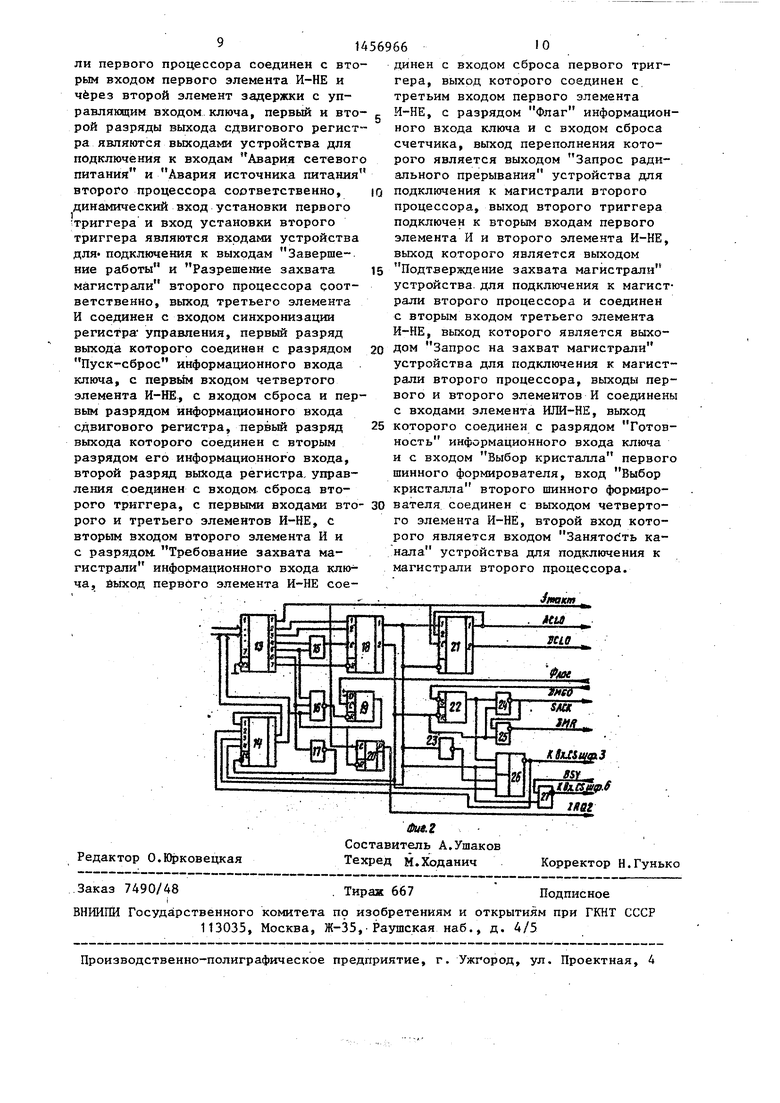

Устройство управления доступом к .системной магистрали в двухпроцессорной системе, содержащее два двунаправленных шинных формирователя, блок управления доступом и блок оперативной памяти, вход-выход обмена

магистраль с первыми информационными входами-выходами первого и второго двунаправленных шинных формирователей, вторые информационные входы- выходы которых являются первым и вторым входами-выходами устройства соответственно для подключения магистралей первого и второго процессоров, причем блок управления доступом содержит регистр управления, два триггера, три элемента И и два элемента НЕ, выход первого разряда регистра управления соединен с первым входом первого элемента И и через первый элемент НЕ с первым входом второго элемента И, отличающееся тем, что, с целью повышения надежности системы за счет перераспределения функций управления при отказах процессора, в блок управления досту

пом введены сдвиговый регистр, четыре элемента И-НЕ, элемент ИЛИ-НЕ, счетчик и ключ, выходы с первого по чет- вертый разрядов которого являются

выходами Флаг, Готовность, Пуск- сброс и Требование захвата магистрали устройства для подключения к магистрали первого процессора, вход тактирования устройства для подключения к магистрали первого процессора соединен со счетчным входом счетчика, с входом тактирования сдвигово- го регистра и является выходом тактирования устройства для подключения

к магистрали второго процессора, входы Пуск-сброс, Захват внешней магистрали, Вывод и Начальная установка устройства для подключения к магистрали первого процессора соединены с первым и вторым разрядами информационного входа регистра управления, с первым входом третьего элемента И и с входом сброса регистра управления соответственно, вход Выбор устройства устройства для подключения к магистрали первого процессора соединен с первыми входами третьего элемента И и первого элемента. И-НЕ, вход Ввод устройства для подключения к магистраMtO

XSxJSt 3

SSY Xlf.tSjye.f

| Патент США № 4547845, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

| Патент США № 4495567, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

| . | |||

Авторы

Даты

1989-02-07—Публикация

1987-03-09—Подача