4

4

со ел

Изобретение относится к области вычислительной техники и может быть использовано в вычислительных системах для прогрпммного присвоения абонентам (периферийным устройствам) логических адресов.

Целью изобретения является расширение класса решаемых задач устройства за счет обеспечения возможности оперативного программного присвоения адресов.

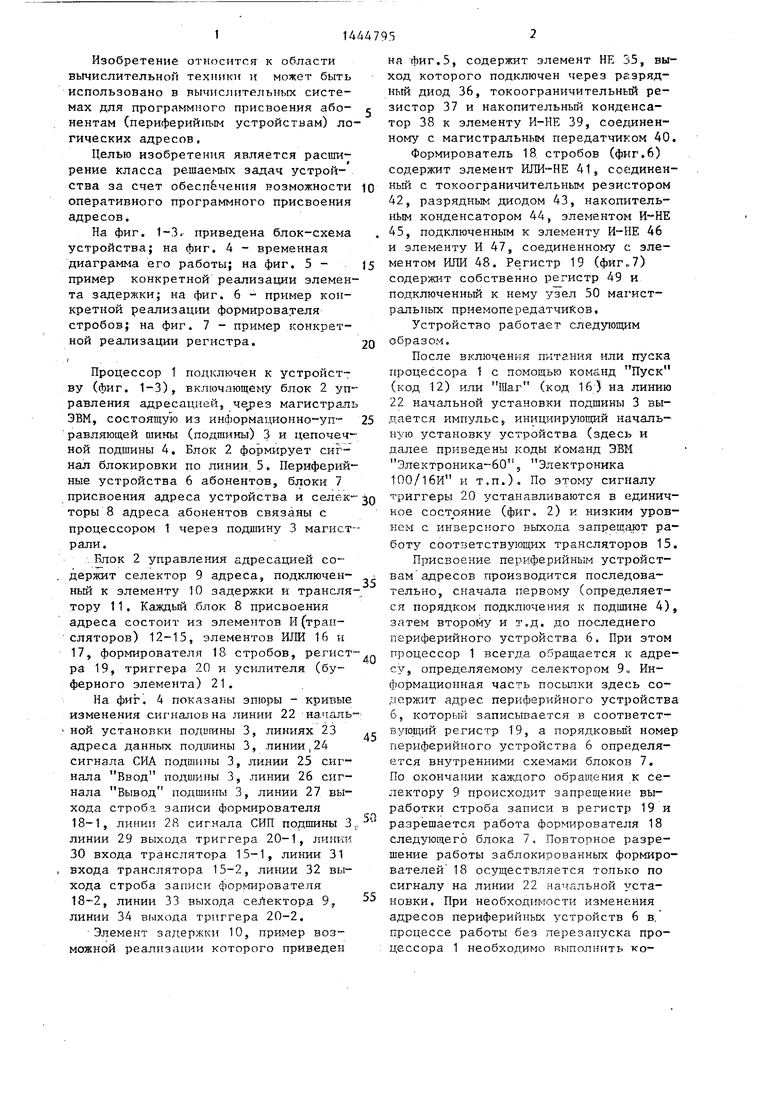

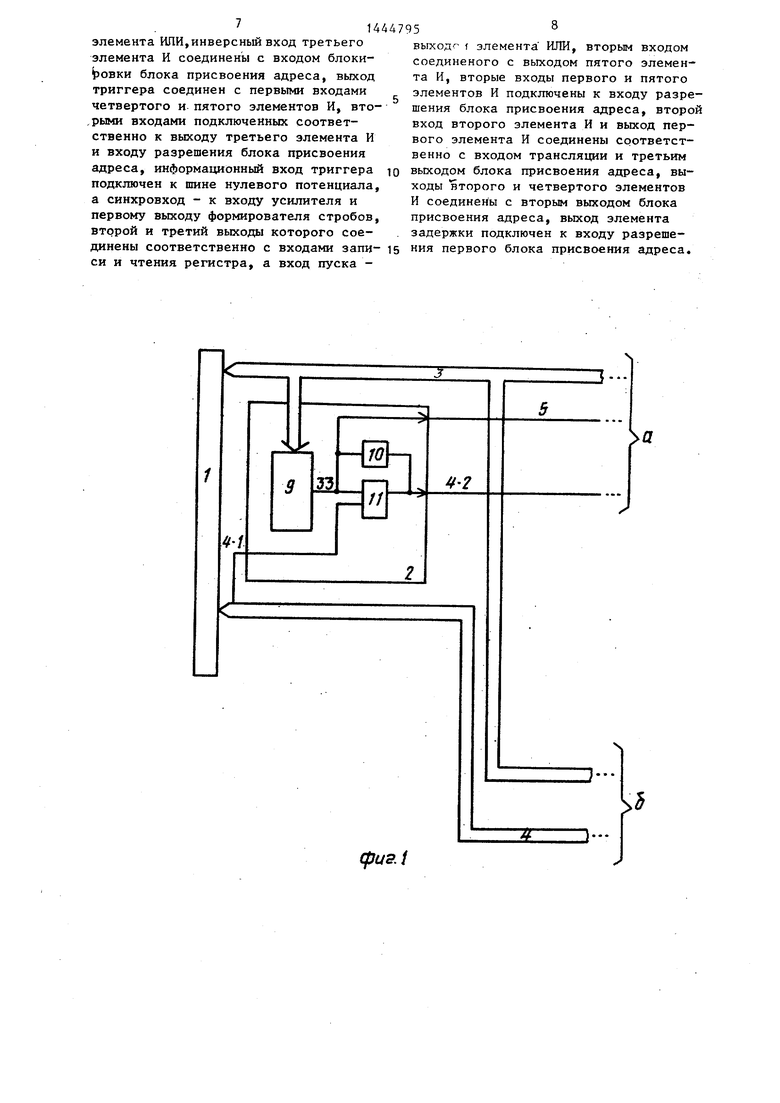

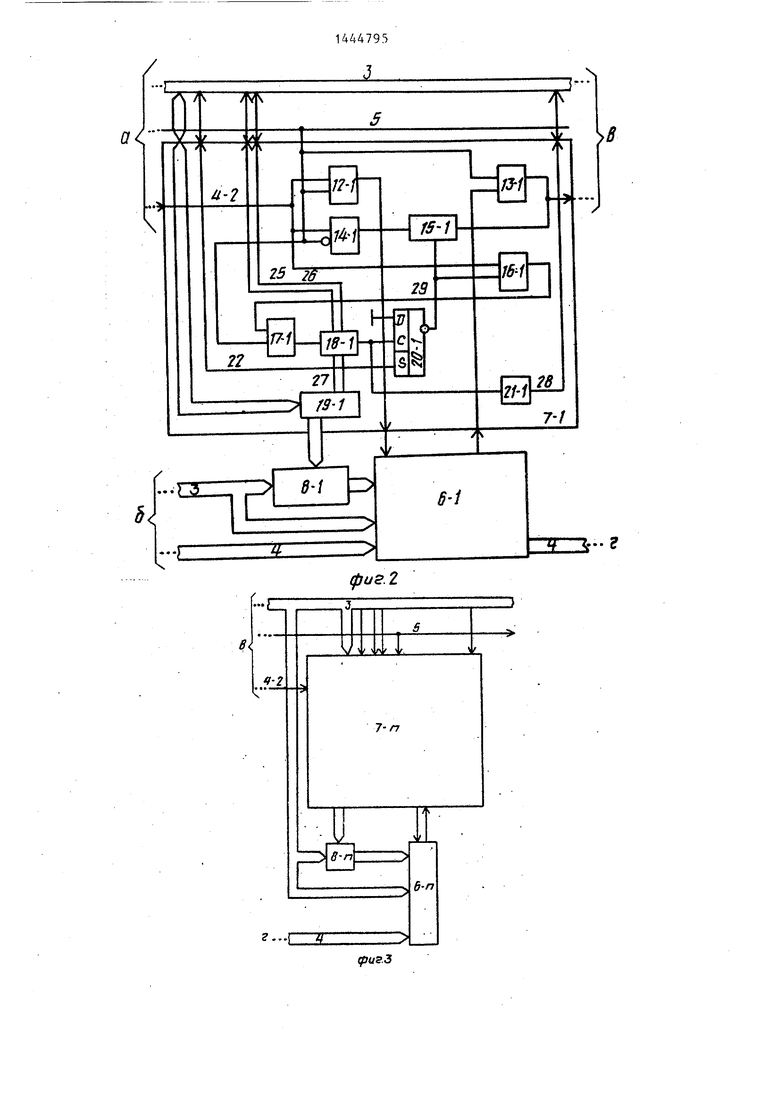

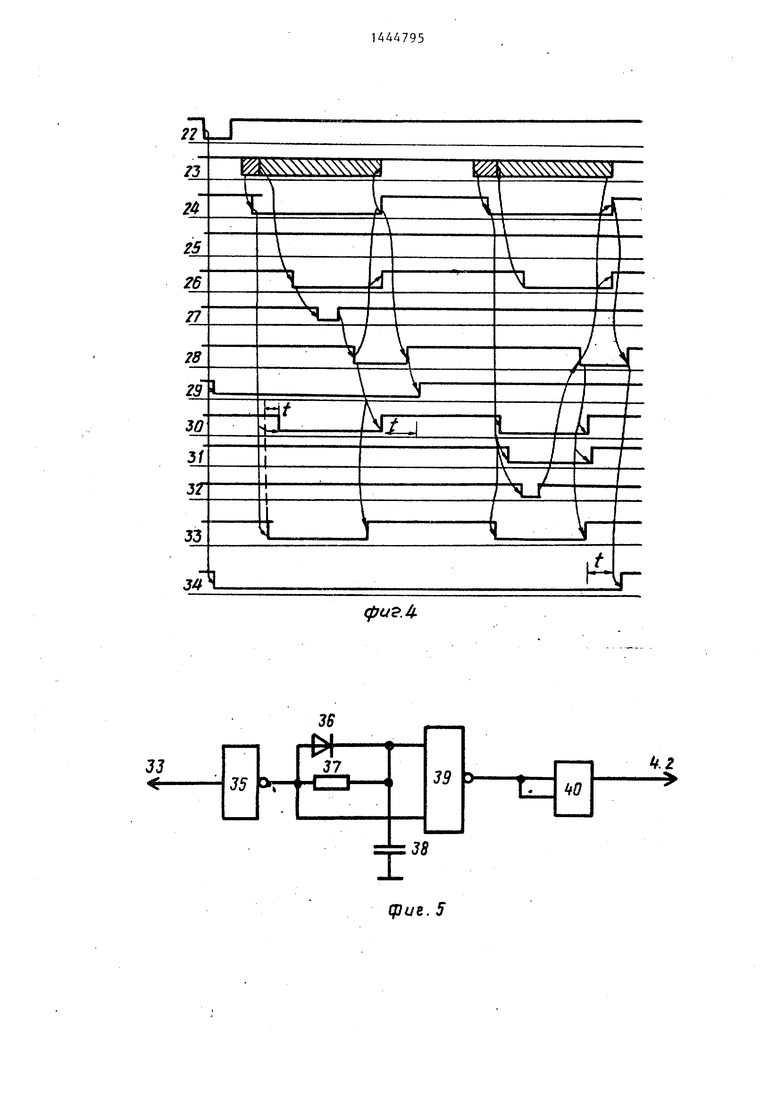

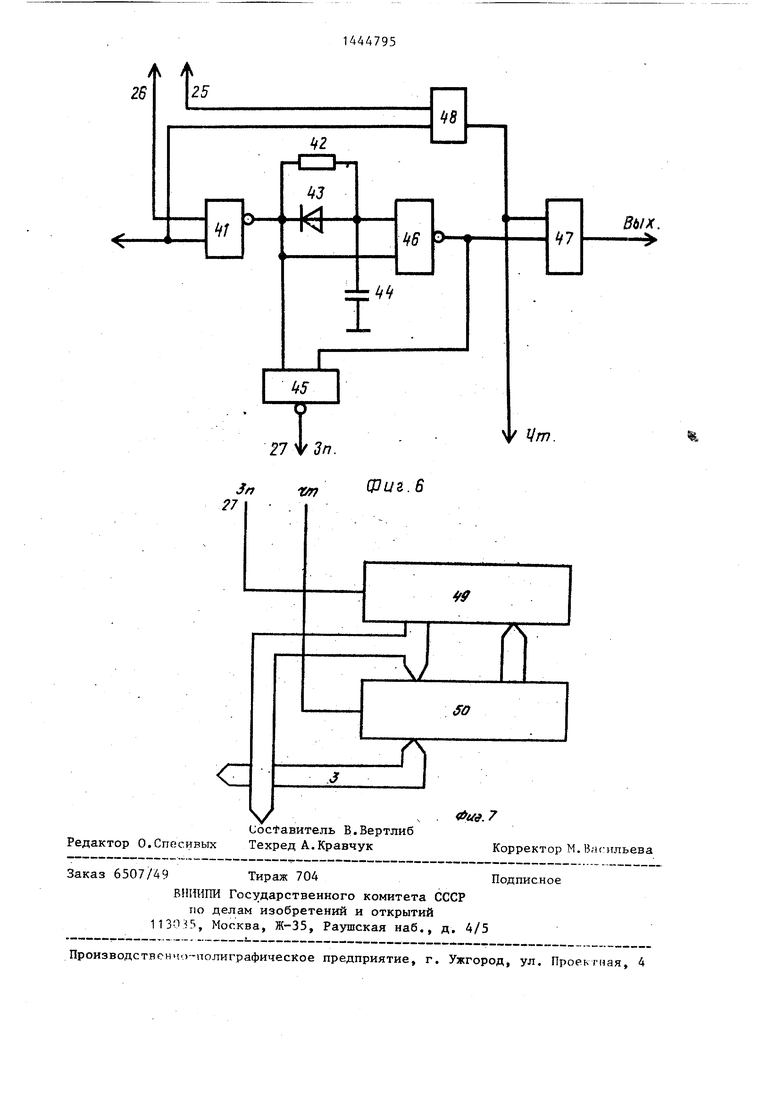

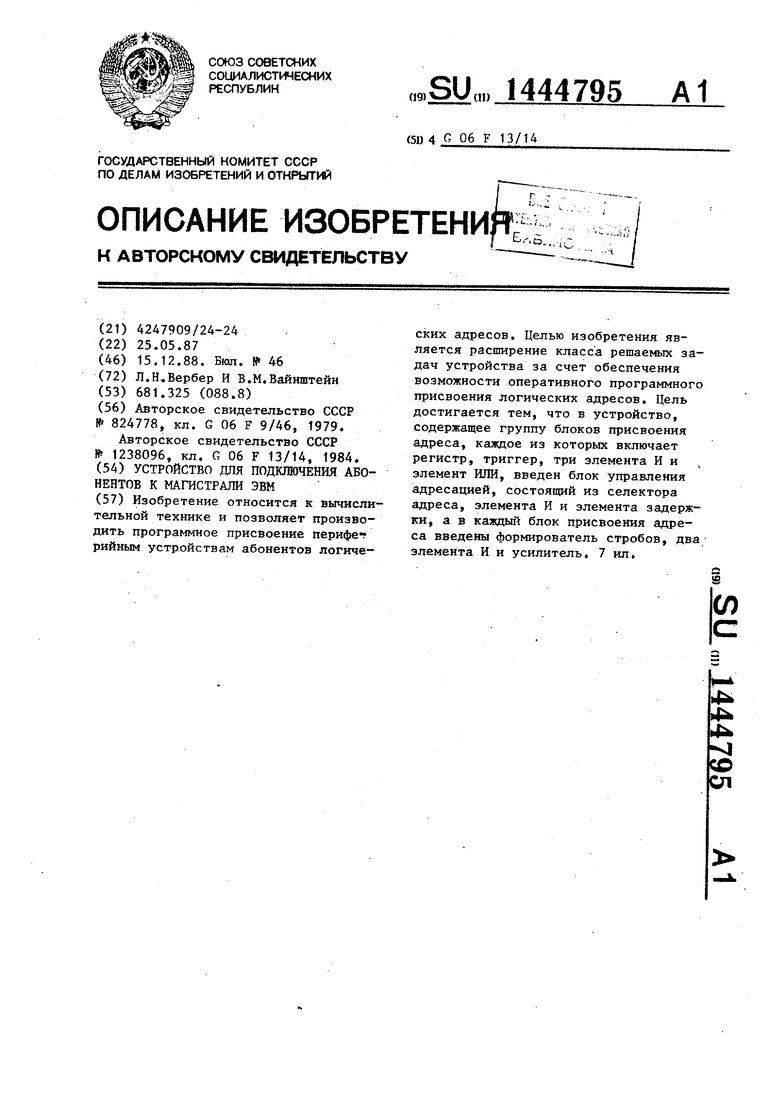

На фиг. 1-3- приведена блок-схема устройства; на фиг, 4 - временная диаграмма его работы; на фиг. 5 - пример конкретной реализации элемента задержки; на фиг, 6 - пример конкретной реализации формирователя стробов; на фиг, 7 - пример конкретной реализации регистра, ( .

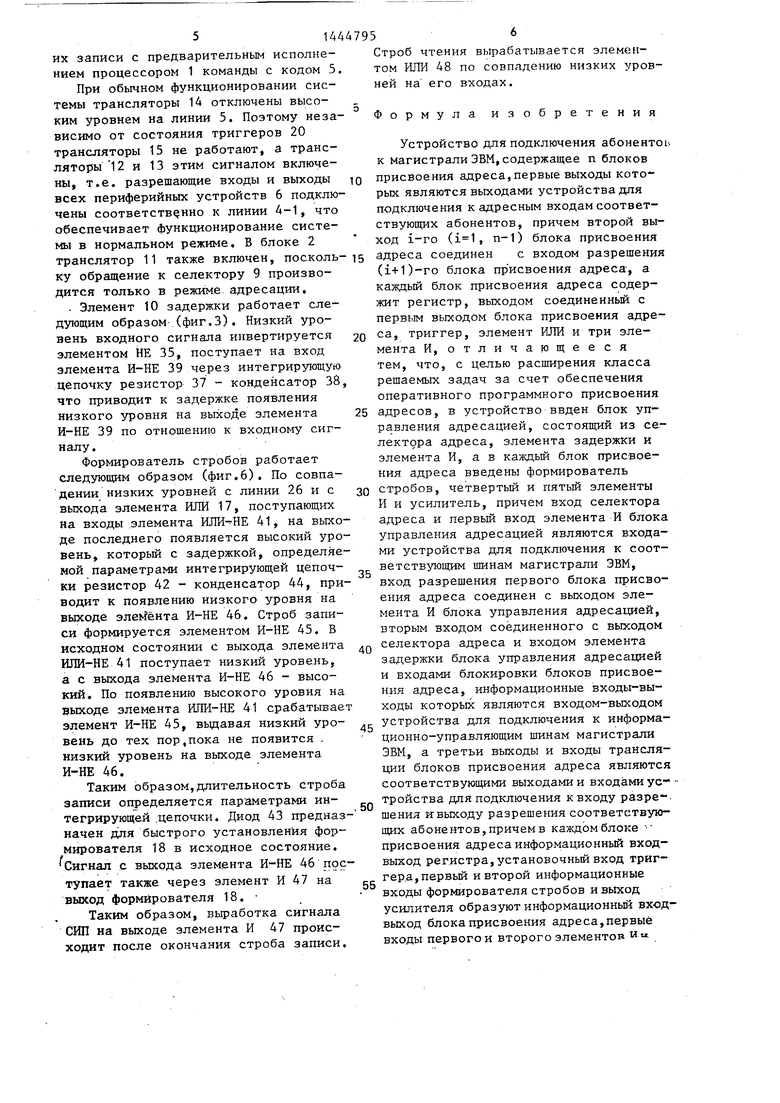

Процессор 1 подключен к устройству (фиг, 1-3), включающему блок 2 управления адресацией, чедзез магистраль ЭВМ, состоящую из информационно-управляющей шинь5 (подшины) 3 и цепочечной подшины 4. Блок 2 формирует сиг™ нал блокировки по линии 5. Периферийные устройства 6 абонентов, блоки 7 присвоения адреса устройства и селекторы 8 адреса абонентов связаны с процессором 1 через подшину 3 магист рали,

,, Блок 2 управления адресацией содержит селектор 9 адреса, подключенный к элементу 10 задержки и транслятору 11, Каждьм блок 8 присвоения адреса состоит из элементов И (трансляторов) 12-15, элементов ИЛИ 16 н 17, формирователя 18 стробов, регистра 19, триггера 20 и усилителя (буферного элемента) 21,

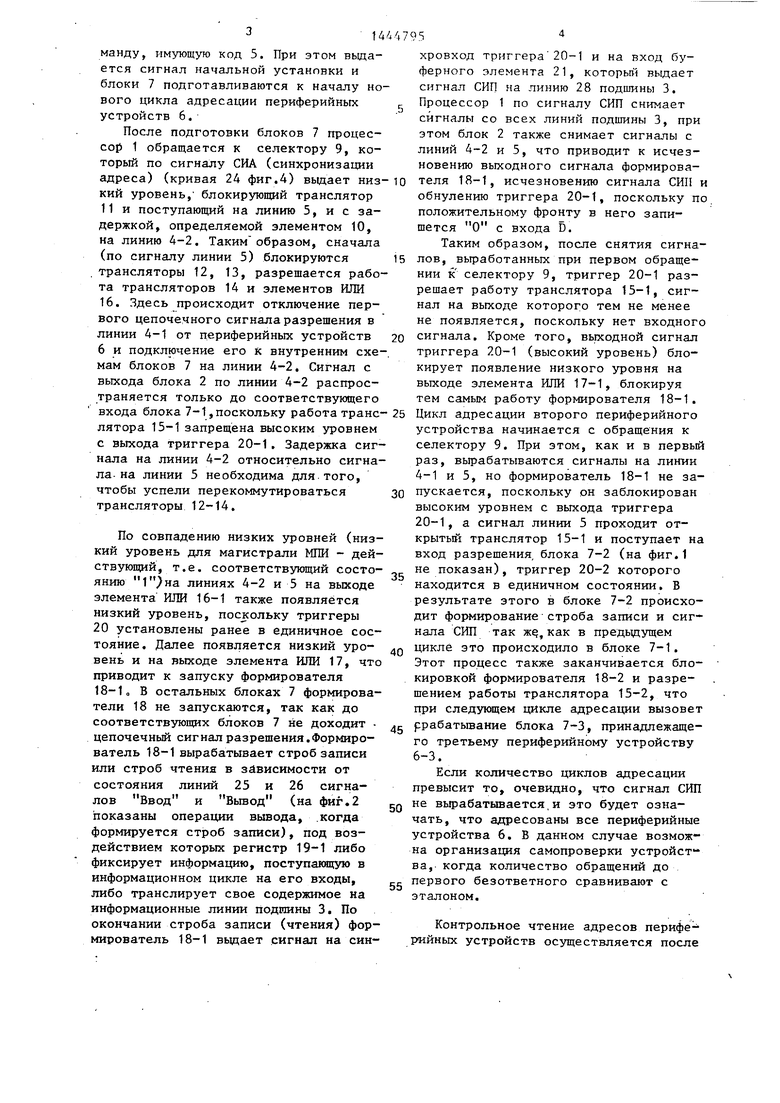

На фиг, 4 показаны эпюры - кривые изменения сигналов на линии 22 напаль

ной установки подигины 3, линиях 23 адреса данных подшины 3, линии,24 сигнала СНА подшины 3, линии 25 сигнала Ввод подшины 3, линии 26 сигнала Вывод подшины 3, линии 27 выхода строба записи формирователя 18-1, линии 28 сигнала СИП подшины 3 линии 29 выхода триггера 20-1, лингш 30 входа транслятора 15-1, линии 31 входа транслятора 15-2, линии 32 выхода строба записи формирователя 18-2, линии 33 выхода селектора 9, линии 34 выхода триггера 20-2,

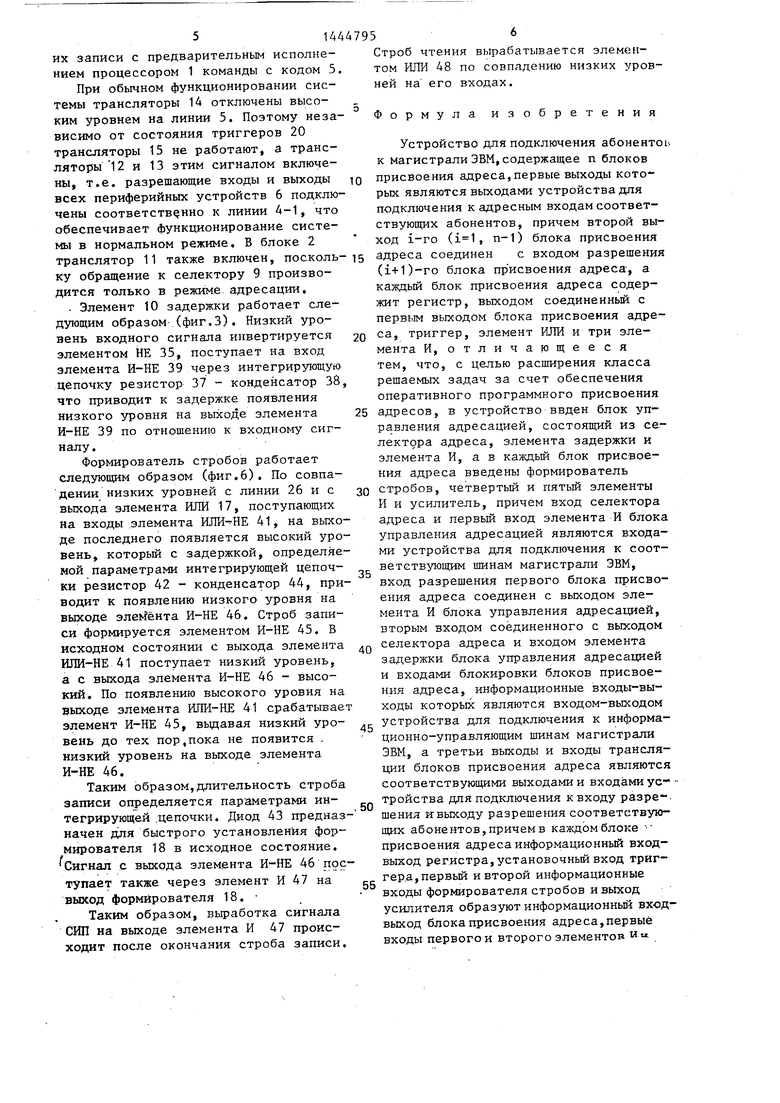

Элемент задержки 10, пример возможной реализации которого приведен

0

5

0

5

0

5

0

5

0

5

на фиг,5, содержит элемент НЕ 55, выход которого подключен через разрядный диод 36, токоограничительный резистор 37 и накопительный конд€ нса- тор 38 к элементу И-НЕ 39, соединенному с магистральным передатчиком 40.

Формирователь 18 стробов (фиг.6) содержит элемент 41, соединенный с токоограничительным резистором 42, разрядньм диодом 43, накопитель- HbiM конденсатором 44, элементом И-НЕ 45, подключенным к элементу И-НЕ 46 и элементу И 47, соединенному с элементом ИЛИ 48, Регистр 19 (фиг,.7) содержат собственно регистр 49 и подключенный к нему узел 50 магистральных приемопередатчиков.

Устройство работает следующим образом.

После включения питания или пуска процессора 1 с помощью команд Пуск (код 12) или Шаг (код 16) на линию 22 начальной установки подшины 3 выдается импульс, инициирующий начальную установку устройства (здесь и далее приведены коды команд ЭВМ Электроника--60, Электроника 100/1бИ и т.п.). По этому сигналу триггеры 20 устанавливаются в единичное состояние (фиг, 2) и низким уровнем с инверсного выхода запрещгшт работу соответствующих трансляторов 15.

Присвоение периферийным устройствам адресов производится последовательно, сначала первому (определяется порядком подключения к подшине 4), затем второму и т.д. до последнего периферийного устройства 6. При этом процессор 1 всегда обращается к адресу, определяемому селектором 9,. Информационная часть посылки здесь содержит адрес периферийного устройства б, который записывается в соответствующий регистр 19, а порядковьш номер периферийного устройства 6 определяется внутренними схемами блоков 7. По окончании каждого обращения к селектору 9 происходит запрещение выработки строба записи в регистр 19 и разрешается работа формирователя 18 следующего блока 7. Повторное разрешение работы заблокированных формирователей 18 осуществляется только по сигналу на линии 22 начальной установки. При необходимости изменения адресов периферийньк устройств 6 в. процессе работы без nepesanycKci процессора 1 необходимо выполнить ко314

манду, имующую код 5. При этом выдается сигнал начальной установки и блоки 7 подготавливаются к началу нового цикла адресации периферийных устройств 6.

После подготовки блоков 7 процес- сор 1 обращается к селектору 9, который по сигналу СИЛ (синхронизации адреса) (кривая 24 фиг.4) вьщает низкий уровень, блокирующий транслятор 11 и поступающий на линию 5, и с задержкой, определяемой элементом 10, на линию 4-2. Таким образом, сначала (по сигналу линии 5) блокируются трансляторы 12, 13, разрешается работа трансляторов 14 и элементов ИЛИ 16. Здесь происходит отключение первого цепочечного сигнала разрешения в линии 4-1 от периферийных устройств 6 и подключение его к внутренним схемам блоков 7 на линии 4-2. Сигнал с выхода блока 2 по линии 4-2 распространяется только до соответствующего входа блока 7-1, поскольку работа транслятора 15-1 запрещена высоким уровнем с выхода триггера 20-1. Задержка сигнала на линии 4-2 относительно сигнала, на линии 5 необходима для того, чтобы успели перекоммутироваться трансляторы 12-14.

По совпадению низких уровней (низкий уровень для магистрали МПИ - действующий, т.е. соответствующий состоянию линиях 4-2 и 5 на выходе элемента ИЛИ 16-1 также появляется низкий уровень, поскольку триггеры 20 установлены ранее в единичное состояние. Далее появляется низкий уровень и на выходе элемента ИЛИ 17, что приводит к запуску формирователя 18-1 о В остальных блоках 7 формирователи 18 не запускаются, так как до соответствующих блоков 7 не доходит цепочечный сигнал разрешения.Формирователь 18-1 вырабатывает строб записи или строб чтения в зависимости от состояния линий 25 и 26 сигналов Ввод и Вывод (на фиг.2 показаны операции вывода, .когда формируется строб записи), под воздействием которых регистр 19-1 либо фиксирует информацию, поступакяцую в информационном цикле на его входы, либо транслирует свое содержимое на информационные линии подгаины 3. По окончании строба записи (чтения) формирователь 18-1 вьщает сигнал на син795

хровход триггера 20-1 и на вход буферного элемента 21, который выдает сигнал СИП на линию 28 подшины 3. Процессор 1 по сигналу СИП снимает сигналы со всех линий подцтны 3, при этом блок 2 также снимает сигналы с линий 4-2 и 5, что приводит к исчезновению выходного сигнала формирова0 теля 18-1, исчезновению сигнала СИП и обнулению триггера 20-1, поскольку по положительному фронту в него запишется О с входа D.

Таким образом, после снятия сигна5 лов, выработанных при первом обращении к селектору 9, триггер 20-1 разрешает работу транслятора 15-1, сигнал на выходе которого тем не менее не появляется, поскольку нет входного

0 сигнала. Кроме того, вьрсодной сигнал триггера 20-1 (высокий уровень) блокирует появление низкого уровня на выходе элемента ИЛИ 17-1, блокируя тем самым работу формирователя 18-1.

5 Цикл адресации второго периферийного устройства начинается с обращения к селектору 9. При этом, как и в первый раз, вырабатываются сигналы на линии 4-1 и 5, но формирователь 18-1 не за0 пускается, поскольку он заблокирован высоким зфовнем с выхода триггера 20-1, а сигнал линии 5 проходит открытый транслятор 15-1 и поступает на вход разрешения, блока 7-2 (на фиг.1 не показан), триггер 20-2 которого находится в единичном состоянии. В результате этого в блоке 7-2 происходит формирование строба записи и сигнала СИП так ж,как в предьщущем

Q цикле это происходило в блоке 7-1. Этот процесс также заканчивается блокировкой формирователя 18-2 и разрешением работы транслятора 15-2, что при следующем цикле адресации вызовет

g ррабатьшание блока 7-3, принадлежащего третьему периферийному устройству 6-3.

Если количество циклов адресации превысит то, очевидно, что сигнал СИП

g не вырабатывается,и это будет означать, что адресованы все периферийные устройства 6. В данном случае возможна организация самопроверки устройства, когда количество обращений до

5

первого безответного сравнивают с эталоном.

Контрольное чтение адресов перифе- рийных устройств осуществляется после

их записи с предварительным исполнением процессором 1 команды с кодом 5.

При обычном функционировании системы трансляторы 14 отключены высоким уровнем на линии 5. Поэтому независимо от состояния триггеров 20 трансляторы 15 не работают, а трансляторы 12 и 13 этим сигналом включены, т.е. разрешающие входы и выходы всех периферийных устройств 6 подключены соответственно к линии 4-1, что обеспечивает функционирование системы в нормальном режиме. В блоке 2 транслятор 11 также включен, поскольку обращение к селектору 9 производится только в режиме адресации.

. Элемент 10 задержки работает следующим образом (фиг.3). Низкий уровень входного сигнала инвертируется элементом НЕ 35, поступает на вход элемента И-НЕ 39 через интегрирующую цепочку резистор 37 - конденсатор 38 Что приводит к задержке появления низкого уровня на выходе элемента И-НЕ 39 по отношению к входному сигналу.

Формирователь стробов работает следующим образом (фиг.6). По совпадении низких уровней с линии 26 и с выхода элемента ИЛИ 17, поступающих на входы элемента 41, на выходе последнего появляется высокий уровень, который с задержкой, определяемой параметрами интегрирующей цепочки резистор 42 - конденсатор 44, приводит к появлению низкого уровня на выходе И-НЕ 46. Строб записи формируется элементом И-НЕ 45. В исходном состоянии с выхода элемента ИЛИ-НЕ 41 поступает низкий уровень, а с выхода элемента И-НЕ 46 - высокий. По появлению высокого уровня на выходе элемента И1Ш-НЕ 41 срабатывает элемент И-НЕ 45, вьщавая низкий уро- вень до тех пор,пока не появится . низкий уровень на выходе элемента И-НЕ 46.

Таким образом,длительность строба записи определяется параметрами интегрирующей депочки. Диод 43 предназначен для быстрого установления формирователя 18 в исходное состояние. Сигнал с выхода элемента И-НЕ 46 поступает также через элемент И 47 на выход формирователя 18.

Таким образом, выработка сигнала СИП на выходе элемента И 47 происходит после окончания строба записи.

5

о д

е

5

Строб чтения вырабатывается элементом ИЛИ 48 по совпадению низких уровней на его входах.

Формула изобретения

Устройство для подключения абоненто -. к магистрали ЭВМ, содержащее и блоков присвоения адреса, первые выходы которых являются выходами устройства д,пя подключения к адресным входам соответствующих абонентов, причем второй выход i-ro (, п-1) блока присвоения адреса соединен с входом разрешения (i+1)-ro блока пр исвоения адреса, а каждый блок присвоения адреса содержит регистр, выходом соединенньй с первым выходом блока присвоения адреса, триггер, элемент ИЛИ и три элемента И, отличающееся тем, что, с целью расширения класса рещаемых задач за счет обеспечения оперативного программного присвоения адресов, в устройство ввден блок управления адресацией, состоящий из се- лект9ра адреса, элемента задержки и элемента И, а в каждый блок присвоения адреса введены формирователь стробов, четвертьш и пятый элементы И и усилитель, причем вход селектора адреса и первый вход элемента И блока управления адресацией являются входами устройства для подключения к соответствующим шинам магистрали ЭВМ, вход разрешения первого блока присвоения адреса соединен с выходом элемента И блока управления адресагсией, вторым входом соединенного с выходом селектора адреса и входом элемента задержки блока управления адресацией и входами блокировки блоков присвоения адреса, информационные входы-выходы KOTOpbiic являются входом-выходом устройства для подключения к информационно-управляющим щинам магистрали ЭВМ, а третьи выходы и входы трансляции блоков присвоения адреса являются соответствующими выходами и входами ус-- тройства для подключения к входу разре-. шения н выходу разрешения соответствующих абонентов, причем в каждом блоке присвоения адреса информационный вход- выход регистра, установочный вход триг- гер.а,первьй и второй информационные входы формирователя стробов и выход усилителя образуют информационны) вход- выход блока присвоения адреса,первые входы первого и второго элементов и«

элемента ИЛИ, инверсный вход третьего элемента И соединены с входом блоки- зовки блока присвоения адреса, выход триггера соединен с первыми входами четвертого и пятого элементов И, вто- ,рыми входами подключенных соответственно к выходу третьего элемента И и входу разрешения блока присвоения адреса, информационный вход триггера подключен к шине нулевого потенциала, а синхровход - к входу усилителя и первому выходу формирователя стробов, второй и третий выходы которого сое

выходг- f элемента ИЛИ, вторым входом соединеного с выходом пятого элемента И, вторые входы первого и пятого элементов И подключены к входу раэре- шения блока присвоения адреса, второй вход второго элемента И и выход первого элемента И соединены соответственно с входом трансляции и третьим выходом блока присвоения адреса, выходы второго и четвертого элементов И соединены с вторым выходом блока присвоения адреса, выход элемента задержки подключен к входу разреше

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для подключения абонентов к магистрали ЭВМ | 1987 |

|

SU1476481A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Устройство для сопряжения процессора с памятью | 1987 |

|

SU1481779A1 |

| Устройство для отладки программ | 1986 |

|

SU1319038A1 |

| Устройство адресации памяти | 1989 |

|

SU1689956A1 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1615730A2 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1990 |

|

SU1734099A1 |

| Устройство для сопряжения ведущей и ведомой ЭВМ | 1989 |

|

SU1679493A1 |

| Логический анализатор | 1988 |

|

SU1654822A1 |

Изобретение относится к вычислительной технике и позволяет производить программное присвоение перифе рийным устройствам абонентов логических адресов. Целью изобретения является расширение класса решаемых задач устройства за счет обеспечения возможности оперативного программного присвоения логических адресов. Цель достигается тем, что в устройство, содержащее группу блоков присвоения адреса, каждое из которых включает регистр, триггер, три элемента И и элемент ИЛИ, введен блок управления адресацией, состоящий из селектора адреса, элемента И и элемента задержки, а в казвдый блок присвоения адреса введены формирователь стробов, два элемента И и усилитель. 7 ил.

динены соответственно с входами запи- 15 ия первого блока присвоения адреса, си и чтения регистра, а вход пуска п -®п

зЫ

J

Т...

а

2

cpasj

/

1444795 J

ОС

i

f

V V

2

//i

t-С

5

с

f7

/7/

/ЙГ-/

7

Q

...ГЗ.

r

5-/

8-n

y

7

W

/J-f

fS 1

23

b-f

CH

Ж 7-/

s-i

4

/г2

Л

(fJus. 5

26

L

;

27Vdn.

Jn tm

ifB

-i

7

Вь{)(.

-

f Цт.

фцг.В

L Л

/

| Авторское свидетельство СССР № 824778, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для подключения абонентов к магистрали электронной вычислительной машины | 1984 |

|

SU1238096A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-12-15—Публикация

1987-05-25—Подача