1

i

Изобретение относится к измерительной технике и может быть использовано при анализе и регистрации характеристик электрических сигналов в специализированных цифровых вычислительных устройствах.

Цель изобретения - уменьшение динамической погрешности и времени преобразования.

На фиг. 1 приведена структурная схема аналого-цифрового преобразователя ( на фиг. 2 и 3 - временные диаграммы, поясняющие его работу; на фиг. 4 - электрическая принципиальная схема блока выбора и фиксации номера последовательности; на фиг. 5- электрическая принципиальная схема анализатора импульсной последователъности( на фиг. 6 - электрическая принципиальная схема формирователя кода, для визуального контроля.

Аналого-цифровой преобразователь содержит М усилителей 1, М устройств 2 выборки-хранения, М компараторов 3, блок 4 выбора и фиксации номера последовательности, коммутатор 5, генератор 6, распределитель 7 импульсов, анализатор 8 импульсной последовательности, регистр 9, формирователь 10 кода для визуального контроля, преобразователь 11 код - аналог, источник 12 опорного напряжения, блок 13 сравнения и формирователь 14 импульсов.

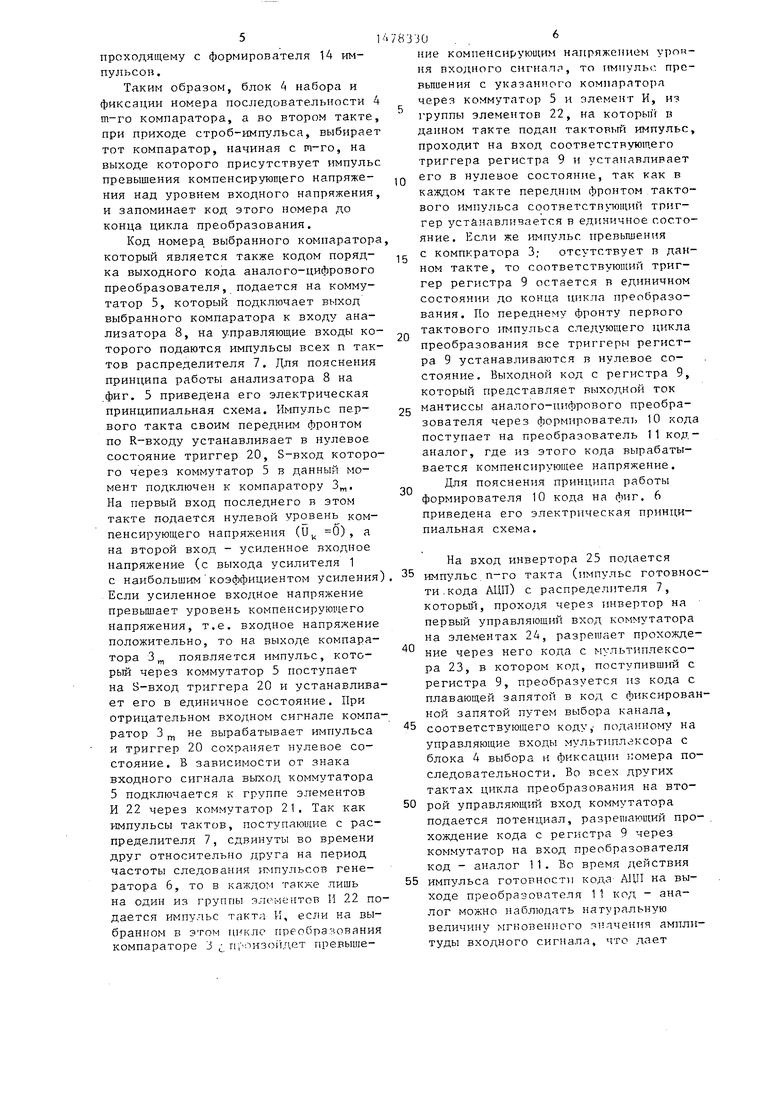

Блок выбора и фиксации номера импульсной последовательности (фиг. 4) содержит триггеры 15, коммутатор 16 на элементах 2И-ИЛИ-НЕ и инверторе, приоритетный шифратор 17 на элементах И-НЕ, триггеры 18, шифратор 19.

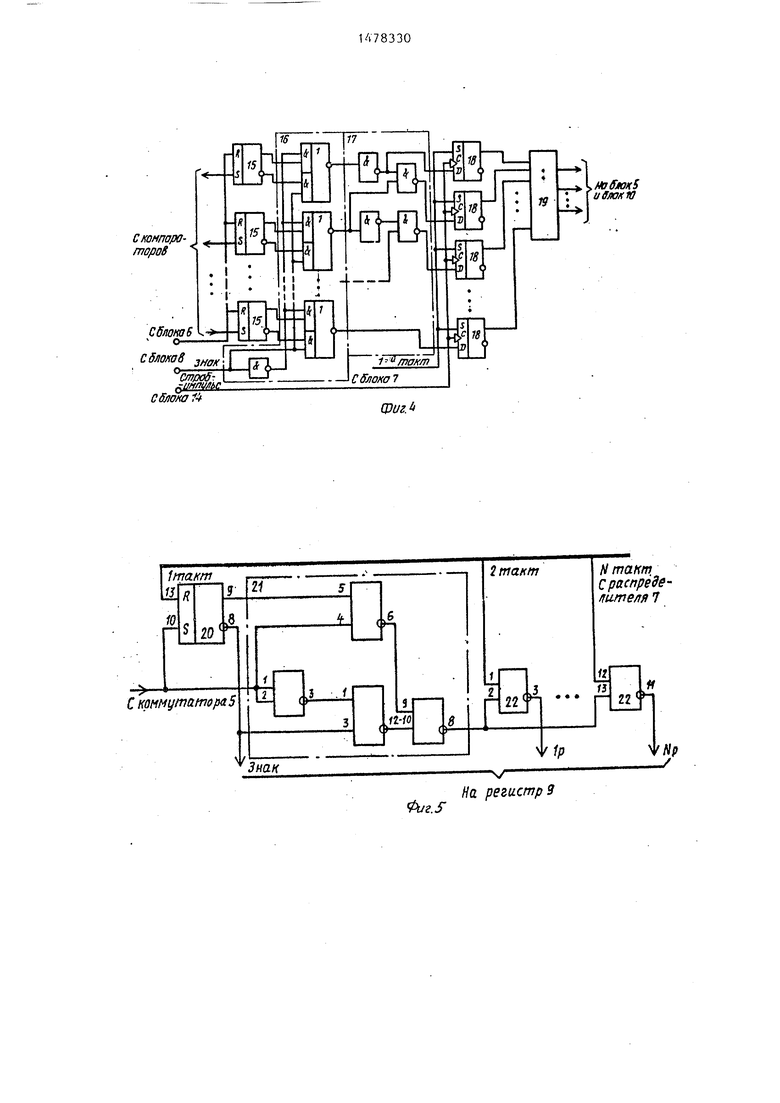

Анализатор импульсной последова- тельности(фиг. 5) содержит триггер 20, коммутатор 21 на элементах И-НЕ, группу элементов И 22.

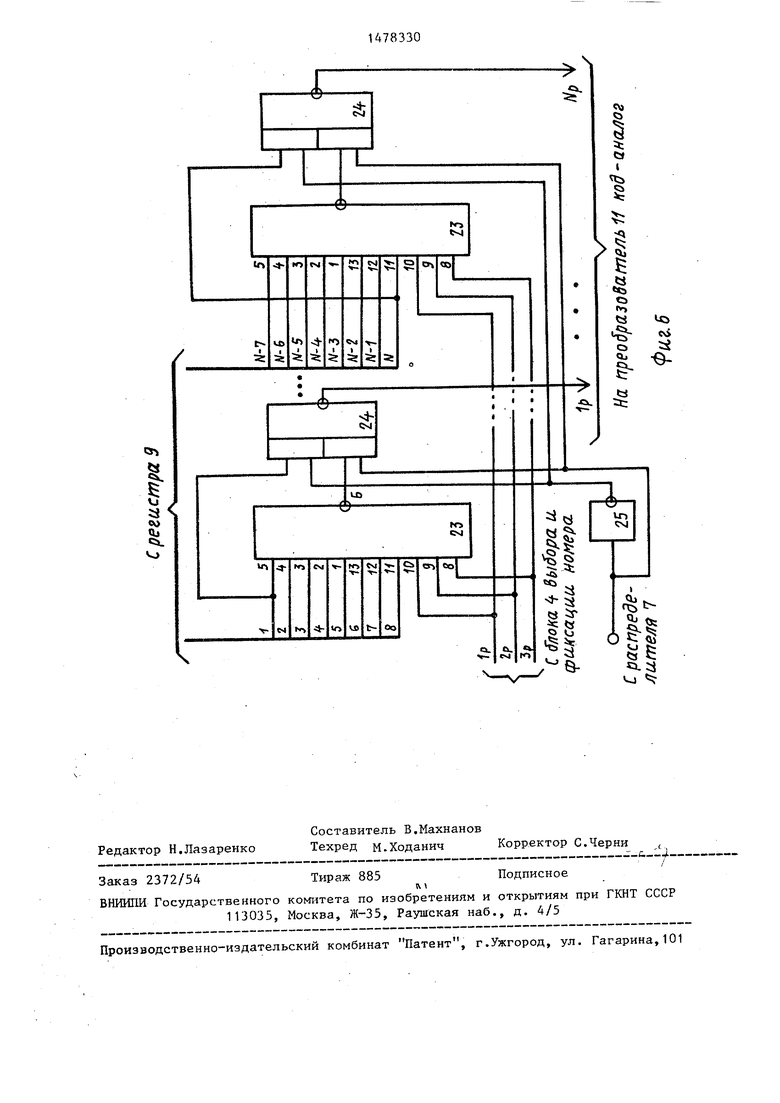

Формирователь кода для визуального контроля (фиг. 5) содержит мультиплексор 23 и коммутатор на элементах 2И-ИЛИ-НЕ 24 и инверторе 25.

Аналого-цифровой преобразователь работает следующим образом.

Входное напряжение Ux подается одновременно на входы всех М усилителей 1 с коэффициентами передачи, представляющими степенями обоснования системы счисления, по которой работает аналого-цифровой преобразователь. С выхода усилителей 1 усиленное входное напряжение поступает на сигнальные входы соответствующих устройств 2 выборки-хранения, на управляющие входы которых подается n-ый тактовый импульс с распределителя 7, представляющий импульс готовности кода аналого-цифрового преобразователя. Во время действия импульса готовности устройства 2 выборки-хранения повторяют входные напряжения, поступающие с выходов соответствующих усилителей 1 , а по окончании импульса готовности запоминает их мгновенные значения и переходят в режим хранения на цикл преобразования.

Запомненные мгновенные значения напряжений поступают на первые вхо

5

0

5

0

5

0

5

0

5

ды соответствующих компараторов 3, на вторые входы которых подается компенсирующее напряжение с преобразователя 11 код - аналог, а на третьи входы - импульсы с генератора 6 для стробирования результатов сравнения в каждом такте цикла преобразования. За время действия строб-импульса на выходах тех компараторов, на которых компенсирующее напряжение превысило уровень входного напряжения, появляются импульсы превышения, поступающие одновременно на коммутатор 5 и блок 4 выбора и фиксации номера последовательности, на управляющие входы последнего подаются также ИМПУЛЬСЫ с генератора 6 , импульс первого такта с распределителя 7 и знаковый разряд с анализатора 8.

В блоке выбора и фиксации номера последовательности 4 первая группа триггеров 15 служит для запоминания состояния выходов компараторов 3 в каждом такте преобразования. Передним фронтом каждого импульса, поступающего с генератора 6, все триггеры первой группы устанавливаются в нулевое состояние. Затем проходящими импульсами с компараторов, на которых компенсирующее напряжение превысило уровень входного напряжения, соответствующие триггеры первой группы устанавливаются в единичное состояние. Одновременно с одним из импульсов генератора 6 на блок 4 выбора и фиксации номера последовательности поступает импульс первого такта с распределителя 7, передним фронтом которого все триггеры 18 второй группы устанавливаются в едииничное состояние, и сигналы с их выходов подаются на шифратор 19, где вырабатывается код номера компаратора Зт. В первом такте преобразования всегда выбирается га-й компаратор, что необходимо для определения знака входного напряжения. Сигналы первой группы триггеров 15 с единичных или нулевых выходов, в зависимости от знака входного напряжения, через коммутатор 16 подаются на приоритетный шифратор 17, где производится выбор триггера (начиная с нижнего по схеме), на котором окажется высокий потенциал. Этот процесс повторяется каздый такт преобразования, но в триггеры 18 второй группы эта информация записывается только по строб-импульсу,

проходящему с формирователя 14 импульсов.

Таким образом, блок 4 набора и фиксации номера последовательности 4 m-го компаратора, а во втором такте, при приходе строб-импульса, выбирает тот компаратор, начиная с m-го, на выходе которого присутствует импульс превышения компенсирующего напряжения над уровнем входного напряжения, и запоминает код этого номера до конца цикла преобразования.

Код номера выбранного компаратора который является также кодом порядка выходного кода аналого-цифрового преобразователя, подается на коммутатор 5, который подключает выход выбранного компаратора к входу анализатора 8, на управляющие входы которого подаются импульсы всех п тактов распределителя 7. Для пояснения принципа работы анализатора 8 на фиг. 5 приведена его электрическая принципиальная схема. Импульс первого такта своим передним фронтом по R-входу устанавливает в нулевое состояние триггер 20, S-вход которого через коммутатор 5 в данный момент подключен к компаратору 3„. На первый вход последнего в этом такте подается нулевой уровень компенсирующего напряжения (Uk 0), а на второй вход - усиленное входное напряжение (с выхода усилителя 1 с наибольшим коэффициентом усиления) Если усиленное входное напряжение превышает уровень компенсирующего напряжения, т.е. входное напряжение положительно, то на выходе компаратора Зт появляется импульс, который через коммутатор 5 поступает на S-вход триггера 20 и устанавливает его в единичное состояние. При отрицательном входном сигнале компаратор 3 m не вырабатывает импульса и триггер 20 сохраняет нулевое состояние. В зависимости от знака входного сигнала выход коммутатора 5 подключается к группе элементов И 22 через коммутатор 21, Так как импульсы тактов, поступающие с распределителя 7, сдвинуты во времени друг относительно друга на период частоты следования импульсов генератора 6, то в каждом также пишь на один из группы элементов И 22 подается импульс такта U, если на выбранном в этом цикле преобразования компараторе 3 произойдет превыше

0

83306

ние компенсирующим напряжением урон- ня входного сигнапс-i, то импульс1, превышения с указанного компаратора через коммутатор 5 и элемент И, и группы элементов 22, на который в данном такте подан тактовый импульс, проходит на вход соответствующего триггера регистра 9 и устанавливает

Q его в нулевое состояние, так как в каждом такте передним фронтом тактового импульса соответствующий триггер устанавливается в единичное состояние. Если же импульс превышения

с с компкратора 3; отсутствует в данном такте, то соответствующий триггер регистра 9 остается в единичном состоянии до конца цикла преобразования. По переднему фронту первого тактового импульса следующего цикла преобразования все триггеры регистра 9 устанавливаются в нулевое состояние. Выходной код с регистра 9, который представляет выходной ток

5 мантиссы аналого-цифрового преобразователя через формирователь 10 кода поступает на преобразователь 11 код - аналог, где из этого кода вырабатывается компенсирующее напряжение. Для пояснения принципа работы формирователя 10 кода на фиг. 6 приведена его электрическая принципиальная схема.

На вход инвертора 25 подается

5 импульс п-го такта (импульс готовности кода АЦП) с распределителя 7, который, проходя через инвертор на первый управляющий вход коммутатора на элементах 24, разрешает прохожде- ние через него кода с мультиплексора 23, в котором код, поступивший с регистра 9, преобразуется из кода с плавающей запятой в код с фиксированной запятой путем выбора канала,

5 соответствующего коду,- поданному на управляющие входы мультиплексора с блока 4 выбора и фиксации номера последовательности. Во всех других тактах цикла преобразования на вто0 рой управляющий вход коммутатора

подается потенциал, разрешающий прохождение кода с регистра 9 через коммутатор на вход преобразователя код - аналог 11. Во время действия

5 импульса готовности кода АИД на выходе преобразователя 11 код - аналог можно наблюдать натуральную величину мгновенного ттченич амплитуды входного сигнала, что дает

0

возможность проследить неискаженную форму преобразуемого сигнала.

С знакового разряда анализатора 8 сигнал поступает на управляющий вход источника 12 опорного напряжения, который в зависимости от знака входного напряжения вырабатывает опорное напряжение +UKwqkr/4 или

-U

К макс

/4. Это напряжение подается

на первый вход блока 13 сравнения, на второй вход которого поступает компенсирующее напряжение с преобразователя 11 код - аналог. При превышении компенсирующим напряжением

опорного напряжения U

К ДЛЯ КС

/4

на выходе блока сравнения появляется сигнал превышения, который поступает на формирователь 14 импульсов, где во втором такте, по импульсу второго такта, поступающего с распределителя 7, вырабатывается строб-импульс длительностью от момента превышения до конца второго такта (фиг. 2). Сформированный строб-импульс с выхода формирователя 14 импульсов подается на третий управляющий вход блока 4 выбора и фиксации номера последовательности где по этому импульсу производится запись информации во вторую группу триггеров 18 (фиг. 4).

Таким образом, введение устройства выборки-хранения в АЦП снижает динамическую погрешность преобразования, а выбор канала для преобразования входного напряжения до достижения компенсирующим напряжением значения UkMCIKC/2, позволяет уменьшить время преобразования.

Формула изобретения

1. Аналого-цифровой преобразователь, содержащий М усилителей, входы которых объединены и являются входной шиной, М компараторов, входы стробирования которых, вход распределителя импульсов и первый управляющий вх-од блока выбора и фиксации номера последовательности объединены и подключены к выходу генератора, а выходы блока выбора и фиксации номера последовательности являются первой выходной шиной, соединены с соответствующими управляющими входами коммутатора и первыми управляющими входами формирователя кода для визуального контроля, выходы

5

0

5

0

5

0

5

0

5

которого через преобразователь код - аналог соединены с первыми информационными входами компараторов, выходы которых соединены с соответствующими информационными входами блока выбора и фиксации номера последовательности и коммутатора, выход которого соединен с информационным входом анализатора импульсной последовательности, управляющие входы с первого по М-ый которого подключены к соответствующим выходам распределителя импульсов и объединены с первыми входами регистра, второй вход которого подключен к первому выходу анализатора импульсной последовательности, а выходы соединены с информационными входами формирователя кода для визуального контроля и являются второй выходной ши- рной, второй управляющий вход блока выбора и фиксации номера последовательности соединен с первым выходом распределителя импульсов, М-й выход которого соединен с дополнительным входом формирователя кода для визуального контроля, отличающийся тем, что, с целью уменьшения динамической погрешности и времени преобразования, в него дополнительно введены М устройств выборки-хранения, соединенные последовательно, источник опорного напряжения, ( блок сравнения и формирователь импульсов, причем выход формирователя импульсов соединен с третьим управляющим входом блока выбора и фиксации номера последовательности, знаковый вход которого объединен с управляющим входом источника опорного напряжения и подключен к первому выходу анализатора импульсной последовательности, вторые выходы которого соединены соответственно с третьими входами регистра, информационные входы устройств выборки-хранения подключены к выходам соответствующих усилителей, управляющие входы объединены с дополнительным входом формирователя кода для визуального контроля, входы объединены, а выходы подключены к вторым информационным входам соответствующих компараторов, второй выход распределителя импульсов соединен с управляющим входом формирователя импульсов, а второй вход блока сравнения подключен к выходу преобразователя код - аналог.

2. Преобразователь по п. 1, отличающийся тем, что.блок выбора и фиксации номера последовательности выполнен на первой и второй группах триггеров, коммутаторе, приоритетном шифраторе, шифраторе, причем R-входы трип еров первой группы объединены и являются первым управляющим входом блока, S-входы - информационным входами блока, выходы каждого триггера соединены с соответствующими информационными входами коммутатора, управляющий вход которого является знаковым входом блока, а выходы коммутатора через приоритетный шифратор соединены с D-входами триггеров второй группы, S-входы которых объединены и являются вторым управляющим входом блока, С-входы объединены и являются третьи управляющим входом блока, а выходы соединены с соответствующими входа0

0

ми шифратора, выходы которого являются выходами блока.

3. Преобразователь по п. 1, отличающий с я тем, что анализатор импульсной последовательности выполнен на триггере, коммутаторе и элементах И по количеству информационных разрядов преобразователя, первые входы которых являются управляющими с второго по М-й входами блока, вторые входы объединены и подключены к выходу коммутатора, первый и второй управляющие входы которого подключены соответственно к прямому и инверсному выходам триггера, R-вход которого является первым управляющим входом блока, S-вход - информационным входом блока и подключен к информационному входу коммутатора, инверсный выход является первым выходом блока, а выходы элементов И - вторыми выходами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1981 |

|

SU1014137A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1984 |

|

SU1282326A1 |

| Устройство для обнаружения поврежденного участка телеграфного тракта | 1981 |

|

SU1042194A2 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1997 |

|

RU2130199C1 |

| Устройство для измерения времени установления выходного сигнала цифроаналогового преобразователя | 1990 |

|

SU1716601A2 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| СПУТНИКОВАЯ СИСТЕМА СВЯЗИ "КИБОЛ" | 1992 |

|

RU2033693C1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1981 |

|

SU1039025A1 |

ИЗОБРЕТЕНИЕ ОТНОСИТСЯ К ИЗМЕРИТЕЛЬНОЙ ТЕХНИКЕ И МОЖЕТ БЫТЬ ИСПОЛЬЗОВАНО ПРИ АНАЛИЗЕ И РЕГИСТРАЦИИ ХАРАКТЕРИСТИК ЭЛЕКТРИЧЕСКИХ СИГНАЛОВ В ЦВМ. ИЗОБРЕТЕНИЕ ПОЗВОЛЯЕТ УМЕНЬШАТЬ ДИНАМИЧЕСКУЮ ПОГРЕШНОСТЬ И ВРЕМЯ ПРЕОБРАЗОВАНИЯ АНАЛОГОВЫХ СИГНАЛОВ В ЦИФРОВУЮ ФОРМУ ПУТЕМ ВВЕДЕНИЯ В АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ УСТРОЙСТВ ВЫБОРКИ И ХРАНЕНИЯ И ВЫБОРА КАНАЛА ВО ВРЕМЯ ФОРМИРОВАНИЯ КОМПЕНСИРУЮЩЕГО НАПРЯЖЕНИЯ UKМАКС/2. СИГНАЛ С ЗНАКОВОГО РАЗРЯДА АНАЛИЗАТОРА ПОСТУПАЕТ НА УПРАВЛЯЮЩИЙ ВХОД ВВЕДЕННОГО ИСТОЧНИКА ОПОРНОГО НАПРЯЖЕНИЯ, КОТОРЫЙ В ЗАВИСИМОСТИ ОТ ЗНАКА ВХОДНОГО НАПРЯЖЕНИЯ ВЫРАБАТЫВАЕТ ОПОРНОЕ НАПРЯЖЕНИЕ +UKМАКС/4 ИЛИ - UKМАКС/4. ЭТО НАПРЯЖЕНИЕ ПОДАЕТСЯ НА ПЕРВЫЙ ВХОД ДОПОЛНИТЕЛЬНО ВВЕДЕННОГО БЛОКА СРАВНЕНИЯ, НА ВТОРОЙ ВХОД КОТОРОГО ПОСТУПАЕТ КОМПЕНСИРУЮЩЕЕ НАПРЯЖЕНИЕ С ПРЕОБРАЗОВАТЕЛЯ КОД-АНАЛОГ ИЗВЕСТНОГО АЦП. ПРИ ПРЕВЫШЕНИИ КОМПЕНСИРУЮЩИМ НАПРЯЖЕНИЕМ ОПОРНОГО НАПРЯЖЕНИЯ /UKМАКС/4/ НА ВЫХОДЕ БЛОКА СРАВНЕНИЯ ПОЯВЛЯЕТСЯ СИГНАЛ ПРЕВЫШЕНИЯ, КОТОРЫЙ ПОСТУПАЕТ НА ВВЕДЕННЫЙ ФОРМИРОВАТЕЛЬ ИМПУЛЬСА, ГДЕ ВЫРАБАТЫВАЕТСЯ СТРОБ-ИМПУЛЬС ДЛИТЕЛЬНОСТЬЮ ОТ МОМЕНТА ПРЕВЫШЕНИЯ ДО КОНЦА ВТОРОГО ТАКТА. СФОРМИРОВАННЫЙ СТРОБ-ИМПУЛЬС ПОДАЕТСЯ НА БЛОК ВЫБОРА И ФИКСАЦИИ НОМЕРА ПОСЛЕДОВАТЕЛЬНОСТИ, РАЗРЕШАЯ ЗАПИСЬ НОМЕРА КАНАЛА, В КОТОРОМ ПОЯВИЛСЯ СИГНАЛ ПРЕВЫШЕНИЯ. ТАКИМ ОБРАЗОМ, ВЫБОР КАНАЛА И СРАВНЕНИЕ АНАЛОГОВОГО СИГНАЛА С КОМПЕНСИРУЮЩИМ НАПРЯЖЕНИЕМ UKМАКС/2 ПРОИЗВОДЯТСЯ ОДНОВРЕМЕННО И НА ВЫБОР КАНАЛА НЕ ЗАТРАЧИВАЕТСЯ ДОПОЛНИТЕЛЬНОГО ВРЕМЕНИ. 2 З.П. Ф-ЛЫ, 6 ИЛ.

фиг.1

I

Oj

Q p: r rs

§.

I

%

Щ.

a

ss

Й

Распределитель 7

Сконпаро- тороВ

С блока 6

С блока 8

CS/IOKO ft

ноУмк5 uffMKrt

фиг1

&je.S

На регистр

| Автометрия, 1974, № 3, с | |||

| Способ приготовления сернистого красителя защитного цвета | 1915 |

|

SU63A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU1014137A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-05-07—Публикация

1986-10-20—Подача