1

(21)4393789/24-24

(22)17.03.88

(46) 07.12.89о Бюл.№ 45 (72) А.В.Тимченко

(53)621.372.542:681.32(088.8)

(56)Погрибной В.А..Бортовые системы обработки сигналов.- Киев: Наукова , думка, 1984, с.86.

Авторское свидетельство СССР 1425840, кл. Н 03 Н 17/06, 1987.

(54)ЦИФРОВОЙ ФИЛЬТР С ДЕЛЬТА-МОДУЛЯЦИЕЙ

(57)Изобретение относится к вычислительной технике и технике связи. Его

использование ц ус.тройст. цифрояой обработки с.г1учайн).гл процессов попло-- ляет повысить, быстродействиг. Цифровой фильтр содержит генератор 1 импульсов, двоичные счетчики 2, 3, формирователь 4 импульсов, блок 6 оперативной памяти, буферный регистр 8, блок 9 постоянной памяти и накапливающие сумматоры 11 - 13. Благодаря введению формирователя 5 импульсов, управляемого переключателя 7 и Ц( мультиплексора 10 в фильтре умножение реализуется лишь на операниях сложен11Я и сдвига. 2 з.п. ф-лы, 4 шь

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1988 |

|

SU1587624A1 |

| Цифровой фильтр | 1987 |

|

SU1425840A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1987 |

|

SU1494210A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1986 |

|

SU1424119A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1987 |

|

SU1425841A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1988 |

|

SU1683172A1 |

| Цифровой фильтр | 1986 |

|

SU1387174A1 |

| Цифровой фильтр с дельта-модуляцией | 1987 |

|

SU1418908A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1988 |

|

SU1510091A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1987 |

|

SU1481893A1 |

Изобретение относится к вычислительной технике и технике связи. Его использование в устройствах цифровой обработки случайных процессов позволяет повысить быстродействие. Цифровой фильтр содержит генератор 1 импульсов, двоичные счетчики 2, 3, формирователь 4 импульсов, блок 6 оперативной памяти, буферный регистр 8, блок 9 постоянной памяти и накапливающие сумматоры 11-13. Благодаря введению формирователя 5 импульсов, управляемого переключателя 7 и демультиплексора 10 в фильтре умножение реализуется лишь на операциях сложения и сдвига. 2 з.п. ф-лы, 4 ил.

Сг.

кп х

B&:i4

Изобретение относится к вычислительной технике и технике связи и может быть использовано в устройствах цифровой обработки случайных процессо (цифровая ф L ьтpaция и спектральный аншшз).

Цель изобретения - повьш1ение быстродействия .

На фиг,1 припедена функциональная схема фильтра; на фиг,2 - выполнение блока оперативной памяти; на фиг,3 - выполнение второго формирователя импульсов; на фиг.4 - временные диаграммы работы.

Цифровой фильтр содержит генератор 1 импульсов, первый и второй двоичные счетчики 2 и 3, первый и второй формироватепи 4 и 5 импульсов, блок 6 оперативной памяти, управляемый переключатель 7, буферный регистр 8, блок 9 постоянгой дтамяти, демульти- плексор 10, первый - третий накапливающие сумматоры 11 - 13,

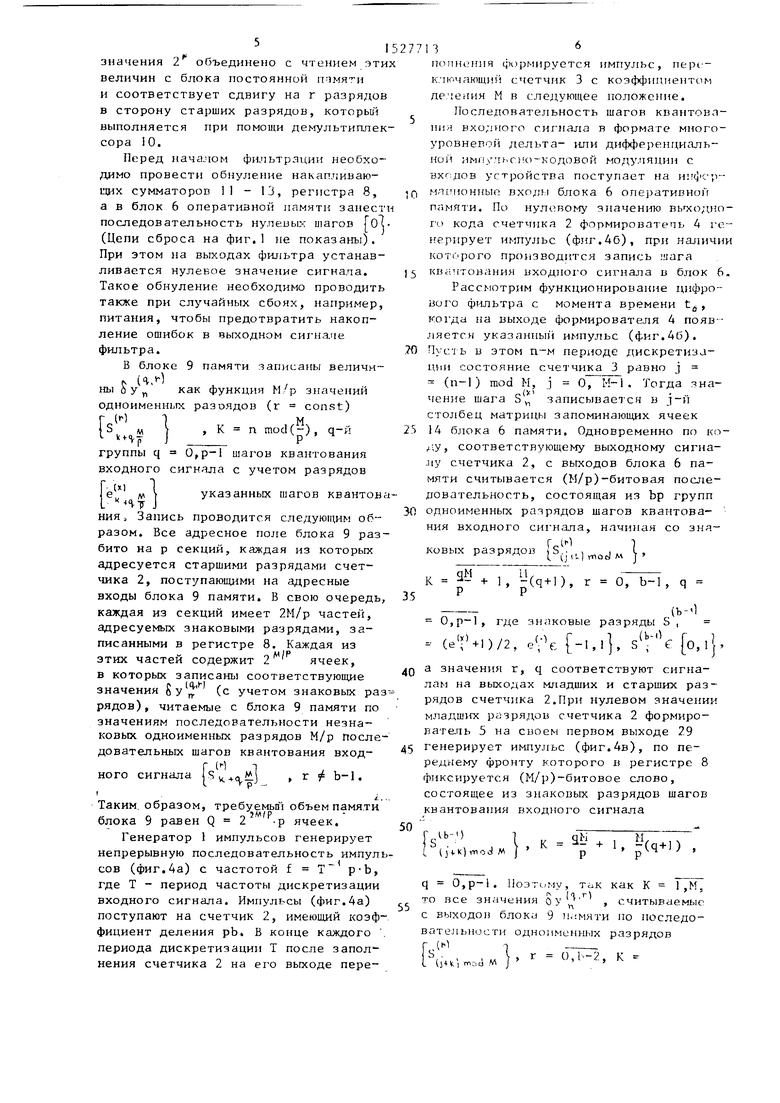

Блок 6 оперативной памяти содержит (фиГо2) матрицу bi M запоминающих ячеек 14 (Ь - разрядность шагов квантования входного сигнала; М - длина импульсной характеристики фильтра), первьй и второй дешифраторы 15 и 16 На фиг, 2 о бозначены информационные входы 17, первые и вторые адресные входы 18 и 19, управляющий вход 20 блока, а также первые и вторые выходы 21 и 22 первого дешифратора 15 и выходы 23 второго дешифратора 16,

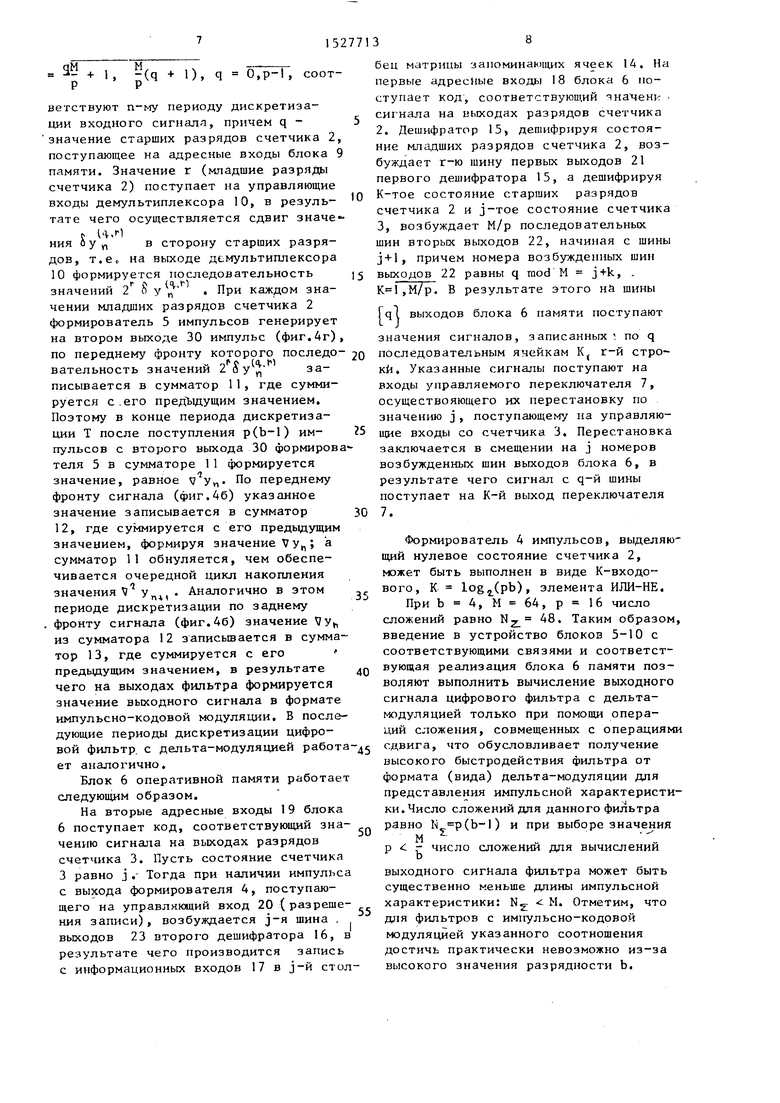

Второй формирователь 5 импульсов содержит (фиг,3) элемент ИЛИ-НЕ 24, первый и второй элементы И 25 и 26, Па фиг„3 обозначены тактовый и инфор- мационные входы 27 и 28, первый и второй выходы 29 и 30,

Цифровой фильтр с дельта-модуляцией работает следующим образом,

В фильтре реализуется следующий атгоритм цифровой фильтрации. Выходной сигнал цифрового фильтра в формате импульсно-кодовой модуляции равен h

М-1 цч

у.

k i m.-o

,|Ь)

(I)

К

О - входная последо вательность;

0,М-1 - импульсная характеристика циф рового ф1шьтра.

ельности Is I и JS I последовгчтельности тагов

квантования соответствующих величин и представлены в формате многоуровневой дельта-модуляции или дифференциальной импульсно-кодовой модуляции. Шаги квантования входного сигнала

поступают на вход фильтра с ко0

5

0

о 5

дирующего устройства - дельта-модулятора и представлены Ь-разрядным словом, представляющим собой знаковый разряд и Ь-1 разрядов абсолютной величины шага квантования входного сигнала: Ь-2

, (О

(Г)

z: s :

.(«)

-k

г-о

(2)

Г 1 где SK € , U - кодирование г-го раз,У ,- , ряда щага; е 1 6 -1,11 - кодирование знака.

шага.

Разделив свертку (1) на р частей и . записав щаги квантования входного сигнала согласно (2), после соответствующих преобразований получают алгоритм функционирования цифрового фильтра

(VulM .

h 1 P-t .1- .- -Г

у„ -ИГ ГЦ 2

1 :О ГеО

VM

( (г1 ,n,.

Вычисление по (3) разделяют последовательных этапа, каждый которых реализуется при помощи рования с накоплением:

о .

35

У. 0

О

vy;

ГУ,

(ц, ,

р

z:

..1

р

Вычисление последней суммы производится при помощи р(Ь-1} с ммирова1- О

с%) m К-т к-т

Cy-KlM

5

«.-IT к-л

л,rlf.:

НИИ величин о у к- / S

которые могут быть вычислены заранее

как функция значений соответствующих битов щагов квантования входного

г (г) -)М Г

сигнала |S V , m m, mod(-)ejO,

- l , r 0, b-2. Величины P J

вычислены с учетом знаковых разрядов

(«И

записаны в

щагов квантования

5

Г C l 1)«

блоке 9 постоянной памяти фильтра. Умножение последовательности велиГ «VrlT -

8у J , г О, Ь-2 на

чин

1 n

, к n mod(-), q-й

группы q 0,p-l шагов квантования входного сигнала с учетом разрядов

1

значения 2 объединено с чтением этих величин с блока постоянной п-чмяги и соответствует сдвигу на г разрядов в сторону старших разрядов, которьй выполняется при помощи де гультиплек- сора 10.

Перед началом фильтрации необходимо провести обнулеьше накапливающих сумматоров 11 - 13, регистра 8, а в блок 6 оперативной памяти занести последовательность нулевых шагов Г0(- (Цепи сброса на фиг.1 не показаны). При этом на выходах фильтра устанавливается нулевое значение сигнала. Такое обнуление необходимо проводить также при случайных сбоях, например, питания, чтобы предотвратить накопление ошибок в выходном сигна11е фильтра.

В блоке 9 памяти записаны величи (Ч-,) ны О у fi как функция М/р значений

одноименных разоядов (г const)

-нИ

указанных шагов квантова

ВИЯ, Запись проводится следующим образом. Все адресное поле блока 9 разбито на р секций, каждая из которых адресуется старшими разрядами счетчика 2, поступающими на адресные входы блока 9 памяти. В свою очередь, каждая из секций имеет 2М/р частей, адресуемых знаковыми разрядами, записанными в регистре 8. Каждая из

м / Р этих частей содержит 2 ячеек,

в которых записаны cooтвeтcтвyюш e значения (с учетом знаковых раз рядов), читаемые с блока 9 памяти по значениям последовательности незнаковых одноименных разрядов М/р после

довательных шагов квантования входного сигнала

Г 1

г / b-l.

Таким, образом, требуемьп объем памяти блока 9 равен Q 2 .р ячеек.

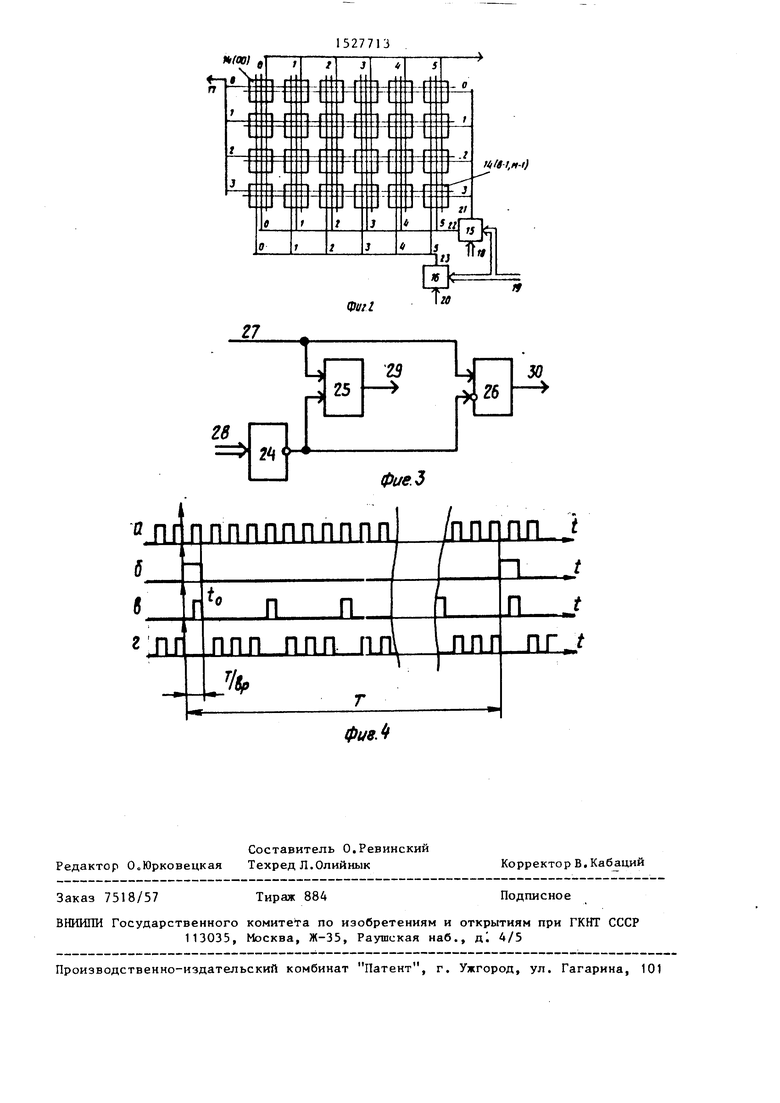

Генератор 1 импульсов генерирует непрерывную последовательность импульсов (фиг.Аа) с частотой f Т Р Ь, где Т - период частоты дискретизации входного сигнала. Импульсы (фиг.4а) поступают на счетчик 2, имеющий коэффициент деления рЬ, В конце каждого . периода дискретизации Т после заполнения счетчика 2 на его выходе пере5

77

5 70

3

T

5

0

5

о

1 3

поииения ({Нормируется импульс, nept;- кчючающил счетчик 3 с коэффип.нентом де.чеиия М в следующее положение.

Последовательность шагов квантования входного сигнала в формате много- уровнепой дельта- или дифференциальной импу-чьсио-кодовой модуляции с вхг:дов устройства поступает на и:Iфc p- млглионныо входм блока 6 опе ативноГг памяти. По нулевому значению выходного кода счетчика 2 формироватепь 4 генерирует импульс (фиг.Аб), при наличии которого производится запись ;лага кваь тонания входного сигнала в блок 6.

Рассмотрим функционирование цифрового фильтра с момента времени t , когда на выходе формирователя 4 появ-- ляется указанный импульс (фиг.46). Пусть в этом периоде дискретиза- цяи состояние счетчика 3 равно j (п-1) mod М, j О, М-1. Тогда значение шага S

(XI

. записывается в j-и столбец матрицы запоминающих ячеек 14 блока 6 памяти. Одновременно по ко- л У, соответствующему выходному сигналу счетчика 2, с выходов блока 6 памяти считывается (М/р)-битовая последовательность, состоящая из Ьр групп одноименных разрядов шагов квантования входного сигнала, начиная со знаковых разрядов sJJ,,,j, |,

К + 1, - (q + 1), г О, Ь-1, q

(b-O

0,р-1, где знаковые разряды S ,

(е Г.1)/2, ,l, ,lj,

а значения г, q соответствуют сигналам на выходах младших и старших разрядов счетчика 2.При нулевом значении младших разрядов счетчика 2 формиро- пате.пь 5 на своем первом выходе 29 генерирует импульс (фиг.4в), по переднему фронту которого в регистре 8 фиксируется (М/р)-битовое слово, состоящее из знаковых разрядов шагов квантования входного сигнала

Г Ь- )IпММ

,4.).odMl 7

q 0,р-1. Поэтому, так как К 1,N.

г (n г то все значения О У , считываемые

с выходом блоку 9 по последовательности одноименных разрядов г (h1 т ..

,- . . М Ь Г 0,Ь-2, К L ( rnaci J

ЗМ Р

М-(q О, q 0,р-1 , соответствуют п-му периоду дискретизации входного сигналя, причем q - значение старших разрядов счетчика 2, поступающее на адресные входы блока 9 памяти. Значение г (младшие разряды счетчика 2) поступает на управляющие входы демультиплексора 10, в резуль- тате чего осуществляется сдвиг значе J (}

ния йу у в сторону старших разрядов, т. ее на выходе демультиплексора 10 формируется последовательность значений 2 У п При каждом значении младших разрядов счетчика 2 формирователь 5 импульсов генерирует на втором выходе 30 импульс (фиг.Аг), по переднему фронту которого последо- вательность значений 2 S У Jij записывается в сумматор 11, где суммируется с,его предЪщущим значением. Поэтому в конце периода дискретизации Т после поступления р(Ь-1) им- пульсов с второго выхода 30 формирова теля 5 в сумматоре 11 формируется значение, равное ,. По переднему фронту сигнала (фиг.Аб) указанное значение записывается в сумматор 12, где суммируется с его предыдущим значением, формируя значение а сумматор 11 обнуляется, чем обеспечивается очередной цикл накопления значения v у.. . Аналогично в этом

УП, периоде дискретизации по заднему

фронту сигнала (фиг.4б) значение Vy из сумматора 12 записьшается в сумматор 13, где суммируется с его предыдущим значением, в результате чего на выходах фильтра формируется значение выходного сигнала в формате импульсно-кодовой модуляции, в последующие периоды дискретизации цифровой фильтр, с дельта-модуляцией работа ет аналогично.

Блок 6 оперативной памяти работае следующим образом.

На вторые адресные входы 19 блока 6 поступает код, соответствую11Ц1Й зна

чению сигнала на выходах разрядов счетчика 3. Пусть состояние счетчика 3 равно j .- Тогда при наличии импульса с выхода формирователя 4, поступающего на управляющий вход 20 (разрешеi

ния записи), возбуждается j-я шина выходов 23 второго дешифратора 16, в результате чего производится запись с информационных входов 17 в j-й стол5)5 20 25 ЗО

35

Q -д

50

55

бец матрицы запоминающих ячеек 14. На первые адресные входы 18 блока 6 поступает код, соответствующий тначени . сигнала на выходах разрядов счетчика

3,возбуждает М/р последовательньк шин вторых выходов 22, начиная с шины J+1, причем номера возбужденных шин выходов 22 равны q mod М j+k, . К 17м/р. В результате этого на шины

fql выходов блока 6 памяти поступают

значения сигналов, записанных : по q последовательным ячейкам К г-й строки. Указанные сигналы поступают на входы управляемого переключателя 7, осуществояющего их перестановку по значению j, поступающему на управляющие входы со счетчика 3. Перестановка заключается в смещении на j номеров возбужденных шин выходов блока 6, в результате чего сигнал с q-й шины поступает на К-й выход переключателя 7.

Формирователь 4 импульсов, выделяющий нулевое состояние счетчика 2, может быть выполнен в виде К-входо вого, К log(pb), элемента ИЛИ-НЕ.

При , , число сложений равно 2. Такнм образом, введение в устройство блоков 5-10 с соответствующими связями и соответствующая реализация блока 6 памяти позволяют выполнить вычисление выходного сигнала цифрового фильтра с дельта- модуляцией только при помощи операций сложения, совмещенных с операциями сдвига, что обусловливает получение высокого быстродействия фильтра от формата (вида) дельта-модуляции для представления импульсной характеристики.Число сложений для данного фильтра равно N р(Ь-1) и при выборе значения

, М р - число сложении для вычислении

D

выходного сигнала фильтра может быть существенно меньше длины импульсной характеристики: N - М. Отметим, что для фильтров с им1гульсно-кодовой модуляцией указанного соотношения достичь практически невозможно из-за высокого значения разрядности Ь.

91

tФормула изобретения

первого двоичного счетчика, выходы разрядов подключены к входам первого формирователя импульсов, выход которого соединен с управляющим входом блока оперативной памяти, информаци- онные входы которого являются входами фильтра, выход переполнения первого двоичного счетчика подключен к входу второго двоичного счетчика, буферный регистр, блок постоянной

памяти, первый - третий накапливающи сумматоры, тактовые входы второго и третьего накапливающих сумматоров объединены с входом обнуления первого накапливающего сумматора, выходы

первого и второго накапливающих сумматоров соединены с информационными входами соответственно второго и третьего накапливающих сумматоров, выходы третьего накапливающего сумматора являются вьосодами фильтра, отличающийся тем, что, с целью повьппения быстродействия фильтра, в него введены управляемый

переключатель, демультиплексор и

второй формирователь импульсов, такто вый вход которого подключен к выходу генератора импульсов, информационные входы второго формирователя импульсов объединены с первыми адресными входам блока оперативной памяти и подключены к выходам разрядов первого двоичного счетчика, выходы второго двоичного счетчика соединены с управляющими входами управляемого переключателя и вторыми адресными входами блока оперативной памяти, выходы которого подключены к информационным входам управляемого переключателя, выходы которого соединены с первыми инфор- мационными входами блока постоянной памяти и информационными входами буферного регистра, выходы которого подключены к вторым информационным входам блока постоянной памяти, вы- ходы которого соединены с информационными входами демультиплексора, управляющие входы которого и адресные входы блока постоянной памяти подключены к выходам соответственно

13

10

5

0

5

15 0 5 0 5

и старщих разрядов первого двоичного счетчика, первый и второй выходы второго формирователя импульсов и выходы демультиплексора соединены соответственно с управляющим входом буферного регистра, тактовым и информационными входами первого накапливающего сумматора, вход обнуления которого подключен к выходу первого формирователя импульсов,

2 о Фильтр поп.1,отлича- ю щ и и с я тем, что блок оперативной памяти содержит матрицу Ь X М запоминающих ячеек (Ь - разрядность шагов квантования входного сигнала, М - длина импульсной характеристики фильтра) и дешифраторы, информационные входы запоминающих ячеек первой - Ь-й строк матрицы соответствен. но объединены и являются информацион-i ными входами блока, первые входы первого и вход стробирования второго дешифраторов являются соответственно первыми адресными и управляющим входами Рлока, вторые входы первого и информационные входы второго дешифраторов соответственно объединены и являются вторыми адресными входами блока, первые и вторые выходы первог( и выходы второго дешифраторов подключены соответственно к первым входам разрешения считывания запоминающих ячеек первой - Ь-й строк матрицы, вторым входам разрешения считывания и входам разрешения записи запоминающих ячеек первого - М-го столбцов матрицы, выходы запоминающих ячеек первого - М-го столбцов матрицы соответственно объединены и являются выходами блока.

ftfooi

Фиг

фив.

Составитель О.Ревинский Редактор ОсЮрковецкая Техред Л.Олийнык

Заказ 7518/57

Тираж 884

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д1 4/5

HiH-lH-i)

Корректор В. Кабаций

Подписное

Авторы

Даты

1989-12-07—Публикация

1988-03-17—Подача