сигнала не уже исходного и принадлежит указанной выше полосе час «-от (О, г значит, при этом отсутствует наложение ciit;xv pa. Указанное обстоятельстве позволяет исключить предварительную филыоацию с помощью ФНЧ входного сигнала, которая обычно предшествует операции прореживания сигналов в системах с .

Уменьшение частоты дискретизации позволяет при гой же элементной базе по- высить разрешающую способность фильтра из-за возможности реализации более сложных алгоритмов фильтрации, например, путем увеличения длины и разрядности весовой последовательности, или увеличить быстродействие фильтров из-за резкого уменьшения чмслз операций, выполняемых за единицу времени. Причем уменьшение часто ы дискретизации позволяет также резко снизить требования по быстродейст- вию к аппаратуре дальнейшей обработки выходного сигнала цифрового фильтра и тем самым увеличить ее пропускную способность.

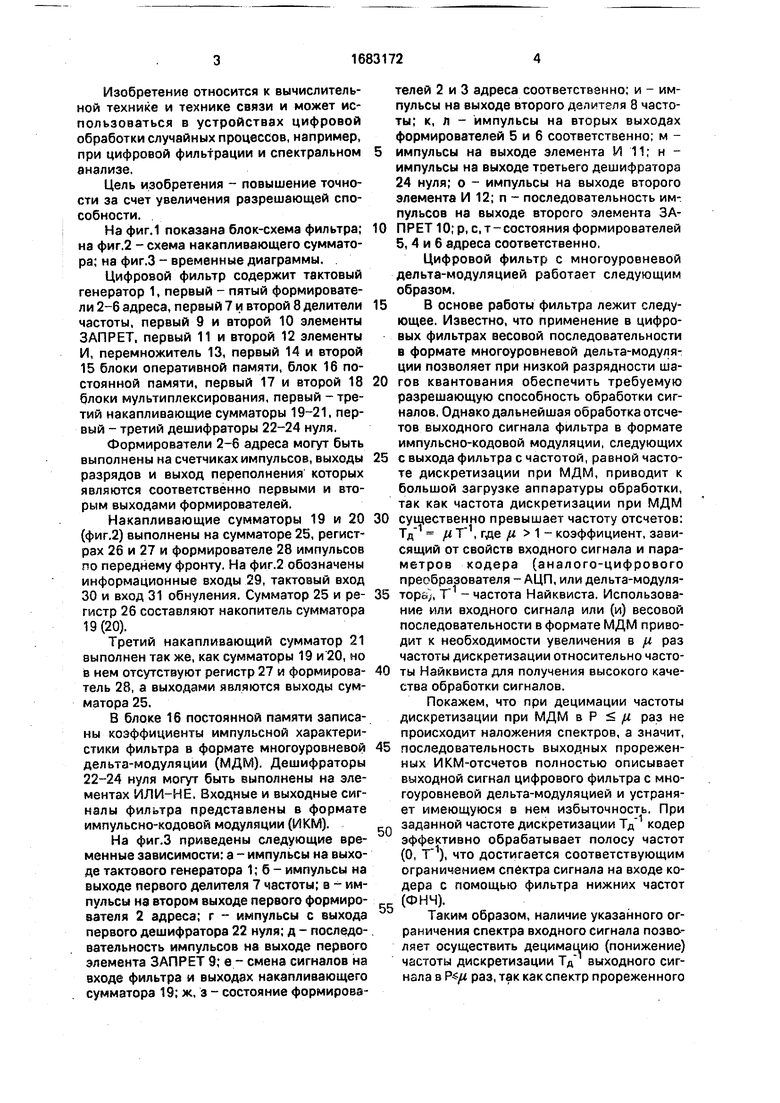

Выходной сигнал цифрового фильтра, входной сигнал которого представлен а формате ИКМ, весовзя последовательность - в формате МДМ, а выходной сигнал представлен в формате И КМ с частотой дискретизации Тд , записывается в виде

У„- Ј f xk-. Sjt),О)

k 1 m 0

где {Xk, k О -входная 1-1 KM;

{Srn }, гп 0, М-1 -- весорзя МДМ после- довательности.

Алгоритм (1) реализуется в фильтре путем представления разностным уравнением, в котором вь ходной сигнал представляется в формате И КМ с соответствующей частотой дискретизации ТУ /Р, и позволяет вычислять только каждое р-е значение выходного сигнала, не теряя промежуточных суммирований по (1):

МY,

- v - - j

Г) -h р -1 п-1 - А 1 Р1 0 ID-0

sch)

r -Tt Jrn

(2)

Путем перестановки знаков суммы в (2) 59 получают алгоритм, реализованный в фильтре

Ч -1

.Y,,., S

(HI

,-1

ю-1 п-1 - Л1- n-ri-7 j w

m 0 -°

где внутренняя сумма в (3) соответствует сумме р последовательных отсчетов входного сигнала с частотой дискретизации , а вычисление выходного сигнала фильтра (3) осуществляется за Тм рТд.

5 10 15 20 2530

дц

Qg

59

5Ь

Кроме того, вычисление только каждого t-rc. отсчета выходного сигнала {YKp} без ui-.iioiri . -:;5 лле ечл точногс накэпливаю- i (его cy fit- Oes- - ччв нсвпзмп но, тлк как те- .ск пром - ,- очные Згвсч яия а значит, I. фун«.:,1я .-,- рэции з цепом

Приведенной алюритм реализуется в фильтре следу:- 4 им образом.

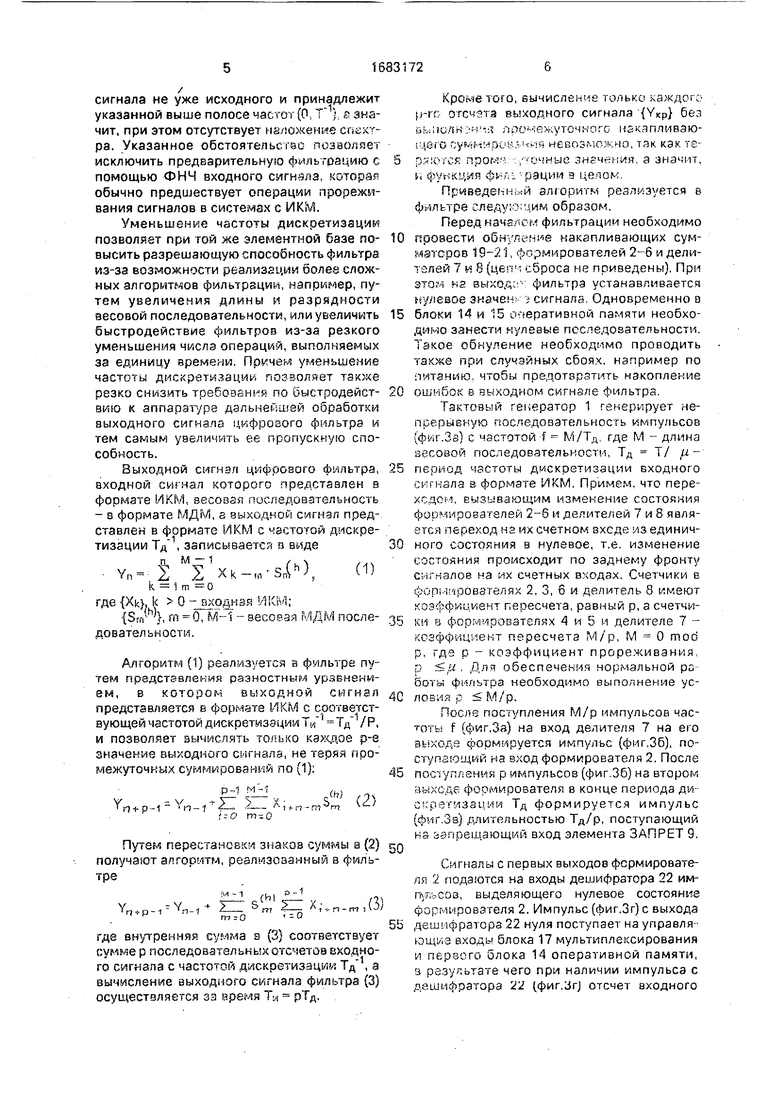

Перед нзчаягм фильтрации необходимо провести (-ие накапливающих сум- матсров 19-21, формирователей 2-6 и дели- - элей 7 и 8 (цеп1: сброса не приведены), При зто на выхода 1 фильтра устанавливается нулевое знамен } сигнала, Одновременно в блоки 14 и 15 оперативной памяти необходимо занести нулевые последовательности. Такое обнуление необходимо проводить также при случайных сбоях, например по питанию, чтобы предотвратить накопление ошибок в выходном сигнале фильтра.

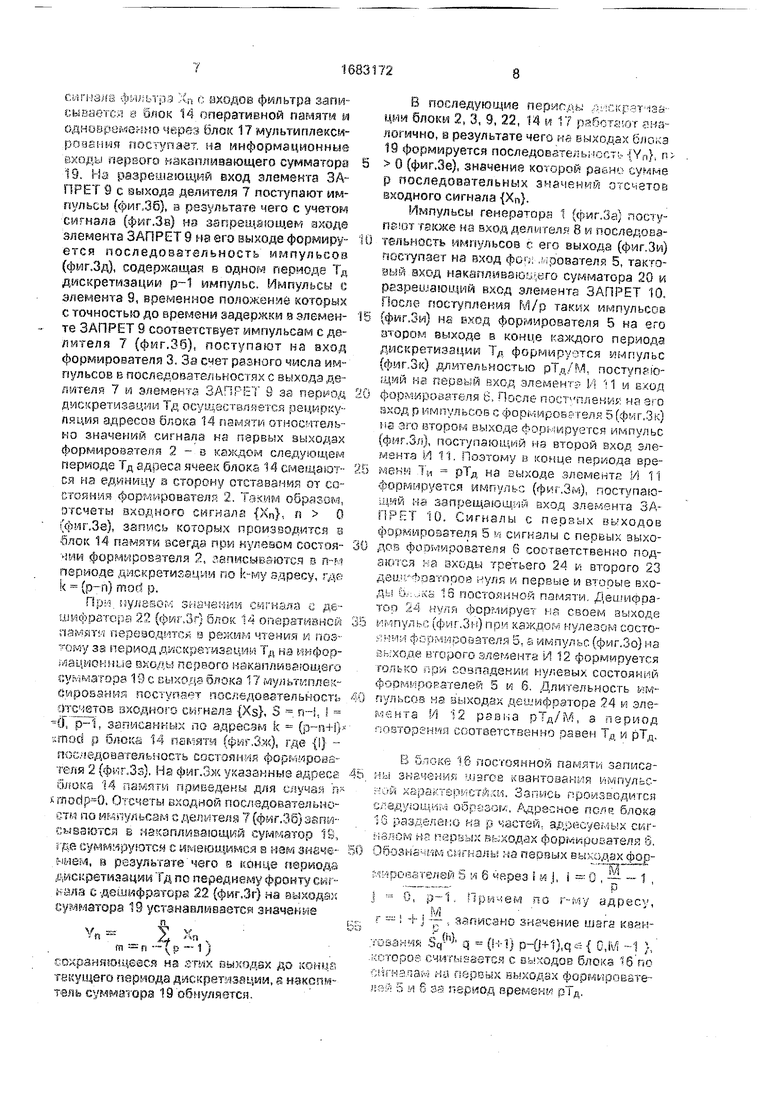

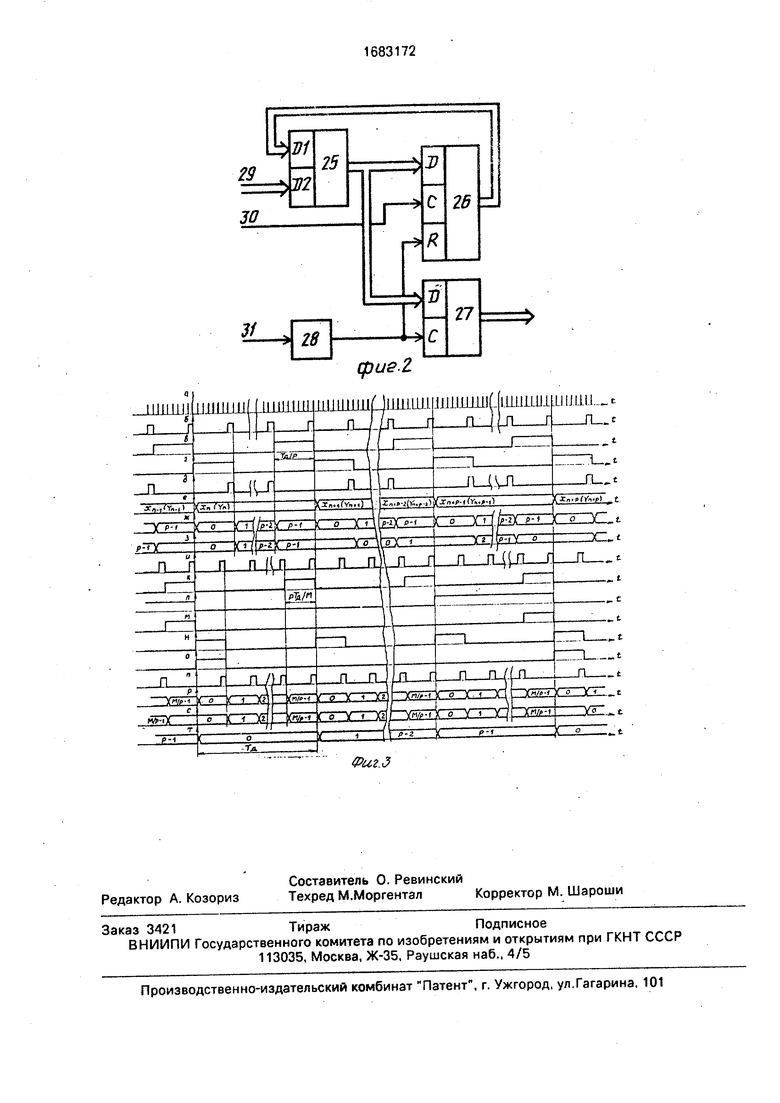

Тактовый геьератор 1 генерирует непрерывную последовательность импульсов .Зз) с частотой f - M/TA где М - длина весовой последовательности, Тд Т/ р. - период частоты дискретизации входного си кала з формате ИКМ, Примем, что пере- хсдсн, вызывающим изменение состояния формирователей 2-6 и делителей 7 и 8 является переход на их счетном зхсде из единичного состояния в нулевое, т.е. изменение состояния происходит по заднему фронту сигналов на их счетных входах. Счетчики в ф-opi з- .ровате/1йх 2. 3, б и делитель 8 имеют коэффициент пересчета, равный р, а счетчики в формирователях 4 и 5 и делителе 7 - коэффициент пересчета М/р, М - 0 mod р, гдэ о - коэффициент прореживания и &д, Для обеспечения нормальной ps боты фильтра необходимо выполнение условия с М/р.

После поступления М/р импульсов час- тоть f (фиг.За) на вход делителя 7 на его выходе формируется импульс (фиг.36), поступающий на вход формирователя 2. После поступления р импульсов (фиг.36) нз втором ныхсде фоомирователя в конце периода ди О . репзаиии Тд формируемся импульс (фиг Зз) длительностью Тд/р, поступающий нз запрещающий вход элемента ЗАПРЕТ 9,

Сигналы с первых выходов формирователя 2 подаются на входы дешифратора 22 им- rnv-сов, выделяющего нулевое состояние формирователя 2. Импульс (фиг.Зг) с выхода дешифратора 22 нуля поступает на управляющие входы блока 17 мультиплексирования и первого блока 14 оперативной памяти, з разуг.отате чего при наличии импульса с дешифратора 22 (фиг.Зг отсчет входного

сигнала фильтра ;(п с входов фильтра записывается в блок 14 оперативной памяти м одновременно через блок 17 мультиплексирования поступает, на информационные входы первого накапливающего сумматора 19. На разрешающий вход элемента ЗАПРЕТ 9 с выхода делителя 7 поступают импульсы (фиг,36), в результате чего с учетом сигнала (фиг.Зв) на запрещающем входе элемента ЗАПРЕТ 9 на его выходе формиру- ется последовательность импульсов (фиг.Зд), содержащая в одном периоде Тд дискретизации р-1 импульс, Импульсы с элемента 9, временное положение которых с точностью до времени задержки га элемен- те ЗАПРЕТ 9 соответствует импульсам с делителя 7 (фиг.36), поступают на вход формирователя 3, За счет разного числа импульсов Б последовательностях с выхода делители 1 м элемента ЗАПРЁТ 9 за период дмекретиззцмм Тд осуществл я ется р8цирку- пяция адресов блока 14 памяти относительно значений сигнала на первых выходах формирователя 2 - в каждом следующем периоде Тд адреса ячеек блока 14 смещают- ся на единицу в сторону отставания от состояния формирователя 2, Таким образом, отсчеты входного сигнала |ХП}, п О (фмг.Зе), запись которых производится а блок 14 памяти всегда при нулевом состоя- формирователя 2, записываются з п-м периоде дискретизации по k-му адресу, где k (p-n) mod p.

Прм. пулевом значении сигнала с дешифратора 22 (фиг .Зг) блок 14 оперативней лзмят - переводится s режим чтения у поэтому за период дискретизации Тд на инфор- мационние входы первого накапливающего сумматора 19 с выхода блока 17 .мультиплексирования поступает последовательность Отсчетов входного сигнала {Xs}, S n-i, I p-l, записанных по адресам k (p-n+iX srnod р блока 14 памяти (фиг.Зж), где - последовательность состояния формирователя 2 (фкг.Зз). На фиг.Зж указанные адреса блока 14 памяти приведены для случая h xmodp 0. Отсчеты входной последовательно- стм по импульсам с делителя 7 (фиг.Зб) записываются в накапливающий сумматор 19, где суммируются с имеющимся в нам зиече- имей, а результате чего в конце периода дискретизации Тд по переднему фронту сиг- кала с -дешифратора 22 (фиг.Зг) на выходах еуш/затора 19 устанавливается значение

У„

п р

зд ,

- 1

сохраняющееся на STMX выходах до конца текущего периода дискретизации, 8 накопитель сумматора 19 обнуляется.

В последующие периоды дукжрзгчзё-- ции блоки 2, 3, 9, 22, 14 м 17 работают аналогично, в результате чего на выходах блока 19 формируется последовательности {Yn}, г.; 0 (фиг.Зе), значение которой равно сумме р последовательных значений отсчетов входного сигнала {Хп}.

Импульсы генератора 1 (фиг.За) поступает также на вход делителя 8 и последовательность импульсов с его выхода (фиг.Зи) поступает на вход фогг; л ровзтеля 5, тактовый вход накапливающего сумматора 20 и разрешающий вход элементе ЗАПРЕТ 10. После поступления М/р таких импульсов (фиг.Зи) на вход формирователя 5 на его втором выходе в конце каждого периода дискретизации Тд формируется импульс (фиг.Зк) длительностью рТд/М, поступающий на пераый вход элемент Ц 1 и вход формирователя 6, После поступление на зго вход р иг пульсов с формирователя 5 (фиг.Зк) на зго втором выходе формируется импульс (фиг.Зл), поступающий на второй вход элемента И 11. Поэтому в конце периода времени Л и рТд на выходе элемента И 11 формируется импульс (фиг.Зм), поступающий на запрещающий вход элемента ЗАПРЕТ 10. Сигналы с первых выходов формирователя 5 и сигналы с первых выходов формирователя 6 соответственно подаются на входы третьего 24 и второго 23 дешифраторов куля и первые и вторые входы о.-:-.. 18 постоянной памяти. Дешифратор 24 нуля формирует на своем выходе мм пульс (фиг.Зн) при каждом нулевом состо- йиии формирователя 5, а импульс (фиг.Зо) на выходе второго элемента И 12 формируется только при совпадении нулевых состояний формирователей 5 и 6, Длительность &«м- пуль,ео8 на выходах дешифратора 24 и элемента И 12 равна рТд/iVi, а период повторения соответственно равен Тд и рТд.

В блоке 16 постоянной памяти записаны значения шэгое квантования мпульс- r-ой характеристик. Запись производится следующий обрйзом, Адресное ПОЛЕ блока 15 разделено на р частей, адресуемых сигналом на первых выходах формирователя б. Обозначим сигналы на первых выходах фЈр;мздовагелей S и 6 через I л , i 0 , - 1 ,

I 0, р-1, Причем по адресу,

У г - I ч-j - , записано значение шага кзанYOsaH s Sq(h} q (Н-1) p-0+1), 0,M 1 },

.которое считывается с выходов блока 1б по сигналам НУ первых выходах формирователей 5 и 6 за период рТд.

Импульс (фиг.Зн) с выхода третьего дешифратора 24 нуля пост4/ „т- - лч щие входы блока 18 мульп,- i v. jOs r я . второго блока 15 операп - л пг, р результате чего при наличии п у/чга ечаче- нме Yn с выходов первого как ч,. кующего сумматора 19 загшсыв&егся в 15 оперативной памяти и одиовреме 0 через блок 18 мульгимлс «t рования ног г/пает на вторые пйре.хит€ й 13

Последовательно sb -irar.3 i) с пыкода второго дели РЛЧ Р .лт п Тпу еет на разрешающий зхо ег.е.н а ЗАПРЕТ 10, на запрещз oui -ifi )т ко г от i t Tynssot импульсы (л и г ЗИ с пчосл элемента У1 11. В pe 3v1bTa re ого из ьыхо ,е з ьздечге ЗАПРЕТ 10 Нормируется послед с ягтельнос ь

(фИгЗп), СО -,

pTn , У

; 10, ere ч -ч е

- СОТ KV GAHPE-Г 1 соотяст г, пуль-сов L д-з мтелг 6 Си вход (РЛи 4

(„hi и i Ј

дов даосмчрсвгтег.: i 4 i - пераи вiop € опер тияно па n u u . Гь и . -с : г г с выхода дел ,-ел w , рТд OL /чдастзгя 1и.п л ячеек блокеп 15 м I J( , о 1ir, с ei а i ч

/ г

см лриоде врэ- -.г с злрмен и О OpL X С

Sric,i - i г

j, 1Ч,«-/пг о на

нь, о на

пы OrrUS 15

с С . V рЈ иОза еяЕ.мостях 1C з i-epi, ос

i чр/У1 ч11с зоресо Пг, (, 3

ес г е,. GJ

, о «-1

ч .

н р - т - - i

г 15

тооь, рзвчо

ST ОТО п .h Ф э /.

8Се,мемь« -„. нос г i ацоесов и где

/-. „ л

j и, -1 -

Р ЛО 5i-5 reri ijoc i ь

hC

i/И

cv

.it

r/v ,ii тОлС1-1 рсчва,шя - u j з /-ого пере- г.мо;«ь(теп ,3 . . /twe сигнала (фиг Зч) с вы/ста .. 4i 1сЛоО 2 - 5лоч 15 оператг ои res, ,ят iQr,eLu: : речи. чтения, & оазуАата1еч чоог TKJ pIV не в i гаыс -jxo nt-pf , 3 по-тупает псос i,i ге знпь {Yf}, iV Ijp-t-j 01 )ых з ч с а 5 о брЈтч1вной па ГР. па

. u гт п ; . - } j -- , о ft V

8

П О з

EN1 IU/P;, I I j- Э р LNTO

,. ч, епцццчЫ (.)

5 Е .г. ЮСТГ) tjj(.(Jt. - СОСТОЯ

. с- el с ь ч (-и jp с i .

-. л , i р ki ч е м - о с г о i i is 4 г риведеиы для сяу-иг (о1 е) ч ин рвале ppewcMi

ю л

Фор

V - о

.« i пч.Ь

п, J. с ч сое з

/ды перемно хигеля 13 за г рТд поступает после

5

0

. ij ез квантоаашп импульс

Кл, v5« - те,,г кк {Sq(W} q (iM)p-O- l}

УМ еччя { rSql } по импуль с°м . г втооого делителя Ь

Е jci3 ;ar --.огол Р накапливающим d 6 s ro , 20 д-,с су мируются - накоплен i : знэчениьм

В рэоисда времени Тм рТд по MS , k; хола второго элемента И К

t , -ч, в сумматоре 20 знзчс ь , JPLSTCS в накапливающей г ьзоттель сумматора 20 оЈыу о Зна 1вние г йчоплонных ь ц м f i f J прсиззедений {V.S / з кз-1. i о , рпеменч ртд равно значению г 31 зк. кач г ч- q f(k 1 } р - J

nii t i (/i re соо ветств /е. n - (, v- -i repnow дискретизации вчсдно s 10

1 ч i,; s (3}по ггсреднему фроч i / г 1 у-ьсо9 с элемента И 1 (фиг Зо) зэпг

С1 и

г,г J чеС1 г QH ДИС t

пг1

O

С св

Г и

ПГО По

. . . 3/ ОС

О

i R на яплвающ11й cvMM3 Gp 2 t о ч чся с на оплен - -.м в чем зьа ,икн, посгедрчЭ1ельнос1ь oi j ди 1 о сигнала цифроао О tcr е (Vk| с частотой

-Тд /р которые пост

Г i

сбогзом в цифровом за

- ерчод следования отсчзтов

о cv - ала бмльтра з форма е V (М)

гтс г/1 эгерацик суммиоовэния

svt обсчетов входного ои

, - знтзоачич импульсной хя

|1Для вычисления

не л ,тсслсдовательносту| зьаче- ,) периоде дискретизации 4 сн. Тд выполняется р сурши- затраты времен;, на вы- е it чодного отсчета фильтра, г -е к периоду Тд можно опреае- j -шзхения

н

М

М

-ум

t)

чг о эХоиииент прореживания

N - л 1. s чессвой послецовз епьчости, ,с врем выполнения операции с . итвагп-я накапливающими суммато- ja , t i, 5C соотзегс венно

1ум - время выполнения операции перемножений блоком 13.

Операции умножения и суммирования разнесены во времени, что содействует получению высокого быстродействия фильтра,

Использование весовой последовательности в формате МДМ позволяет получить требуемую разрешающую способность фильтра путем изменения разрядности весовых коэффициентов. Сигнал {Yn}, формируемый на выходах сумматора 19с частотой дискретизации , является бегущим средним р последовательных отсчетов входного сигнала Хп и также может использоваться в системах цифровой обработки сигналоа. Прямое прореживание выходных ИКМ отсчетов фильтра в р раз (вычисление каждого р-го отсчета) не позволяет достичь указанной цели, так как согласно (1) необходимо выполнять суммирование накапливающим сумматором для всех промежуточных отсчетов выходного сигнала и отсутствие такого накопления приводит в известных устройствах к потере функции фильтрации,

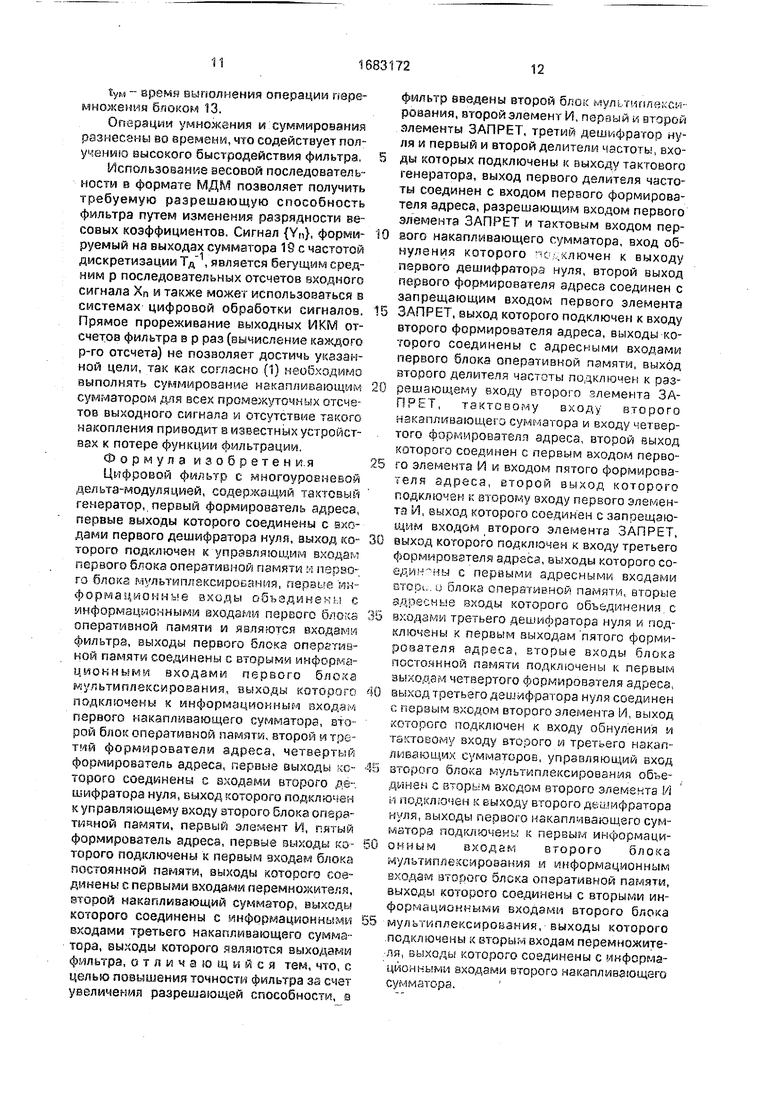

Формула изобретен и. я

Цифровой фильтр с многоуровневой дельта-модуляцией, содержащий тактовый генератор,, первый формирователь адреса, первые выходы которого соединены с входами первого дешифратора нуля, выход которого подключен к управляющим входам первого блока оперативной памяти и парэо-. го блока мультиплексирования, первые информационные входы объэдинечм с информационными входами первого блока оперативной памяти и являются входами фильтра, выходы первого блока оперативной памяти соединены с вторыми информа- ционными входами первого блока мультиплексирования, выходы которого подключены к информационным входам первого накапливающего сумматора, второй блок оперативной памяти, второй и третий формирователи адреса, четвертый формирователь адреса, первые выходы которого соединены с входами второго дешифратора нуля, выход которого подключен к управляющему входу второго Блока оперативной памяти, первый элемент И, пятый формирователь адреса, первые выходы ко- торого подключены к первым входам блока постоянной памяти, выходы которого соединены с первыми входами перемножителя, второй накапливающий сумматор, выходы которого соединены с информационными входами третьего накапливающего сумма-тора, выходы которого являются выходами фильтра, отличающийся тем, что, с целью повышения точности фильтра за счет увеличения разрешающей способности, в

фильтр введены второй блок мул1типле;. см- роаания, второй элемент И, пераый и второй элементы ЗАПРЕТ, третий дешифратор нуля и первый и второй делители частоты, входы которых подключены к выходу тактового генератора, выход первого делителя частоты соединен с входом первого формирователя адреса, разрешающим входом первого элемента ЗАПРЕТ и тактовым входом первого накапливающего сумматора, вход обнуления которого -:. -.ключей к выходу первого дешифратора нуля, второй выход первого формирователя адреса соединен с запрещающим входом первого элемента

ЗАПРЕТ, выход которого подключен к входу второго формирователя адреса, выходы которого соединены с адресными входами первого блока оперативной памяти, выход второго делителя частоты подключен к разрешающему входу второго элемента ЗАПРЕТ, тактовому входу второго накэпл1/гвакщего сумматора и входу четвертого формирователя адреса, второй выход которого соединен с первым входом первого элемента И и входом пятого формирователя адреса, второй выход которого подключен к второму входу первого элемента И, выход которого соединен с запрещающим входом второго элемента ЗАПРЕТ,

выход которого подключен к входу третьего формирователя адреса, выходы которого со- с первыми адресными входами sTOpt. и Г5лока оперативной памяти, вторые адресные входы которого объединения с

входами третьего дешифратора нуля и подключены к первым выходам пятого формирователя адреса, вторые входы блока постоянной памяти подключены к. первым выходам четвертого формирователя адреса,

выход третьего дешифратора нуля соединен с первым входом второго элемента И, выход которого подключен к входу обнуления и тактовому входу второго и третьего накапливающих сумматоров, управляющий вход

второго блока мультиплексирования объединен с вторым входом второго элемента И ii подключен к выходу второго дешифратора нуля, выходы первого накапливающего сумматора подключены к первым информационмым входам второго блока мультиплексирования и информационным входам второго блока оперативной памяти, выходы которого соединены с вторыми информационными входами второго блока

мультиплексирования, выходы которого подключены к вторым входам перемножителя, выходы которого соединены с икфсрма- цйонными входами второго накапливающего сумматора.

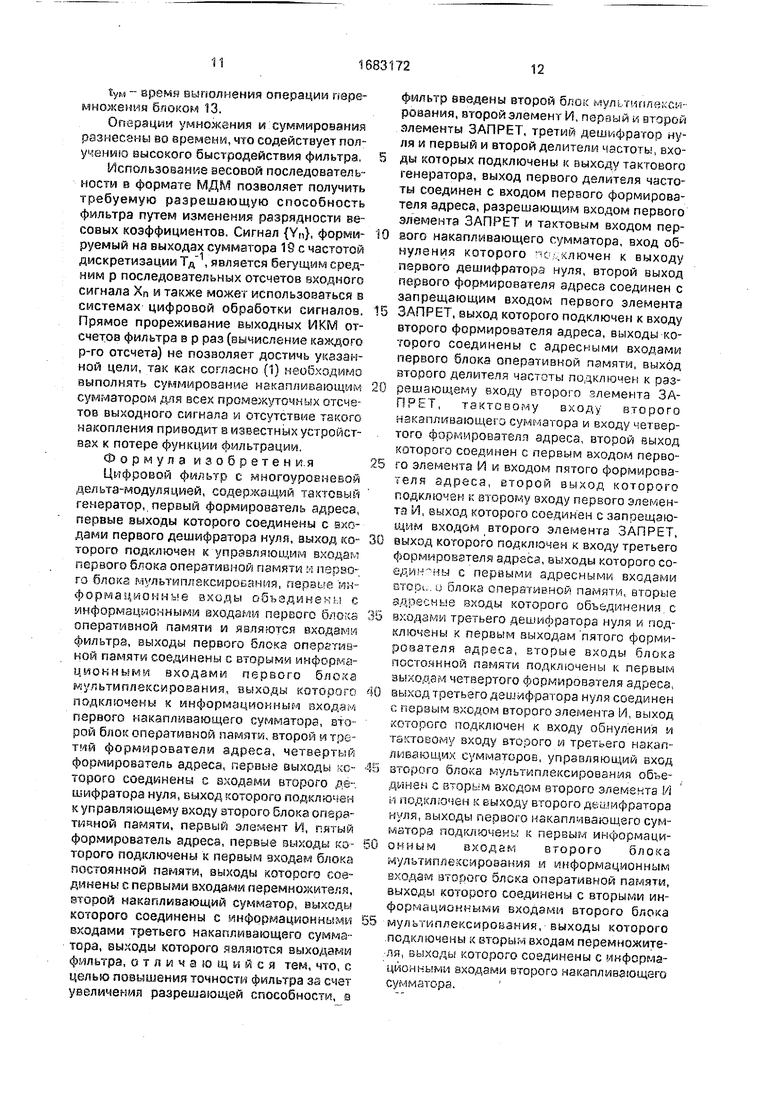

фие.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1988 |

|

SU1587624A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1987 |

|

SU1481893A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1987 |

|

SU1494210A1 |

| Цифровой фильтр с дельта-модуляцией | 1988 |

|

SU1527713A1 |

| Цифровой фильтр | 1986 |

|

SU1387174A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1986 |

|

SU1424119A1 |

| Цифровой фильтр с дельта-модуляцией | 1987 |

|

SU1418908A1 |

| Адаптивный телевизионный дельта-кодер | 1989 |

|

SU1690199A1 |

| Цифровой фильтр | 1987 |

|

SU1425840A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1987 |

|

SU1425841A1 |

Авторы

Даты

1991-10-07—Публикация

1988-12-26—Подача