образом: вывод 1 с тактовым входом контроллера, выводы 27-32 - с выходами 1-6 соответственно, выводы 33 и ЗА - с информационными входами 1 и 2, информационные входы с 3 по п контроллера соответствуют выводам 21-24, 35-38, 12-19 микроЭВМ.

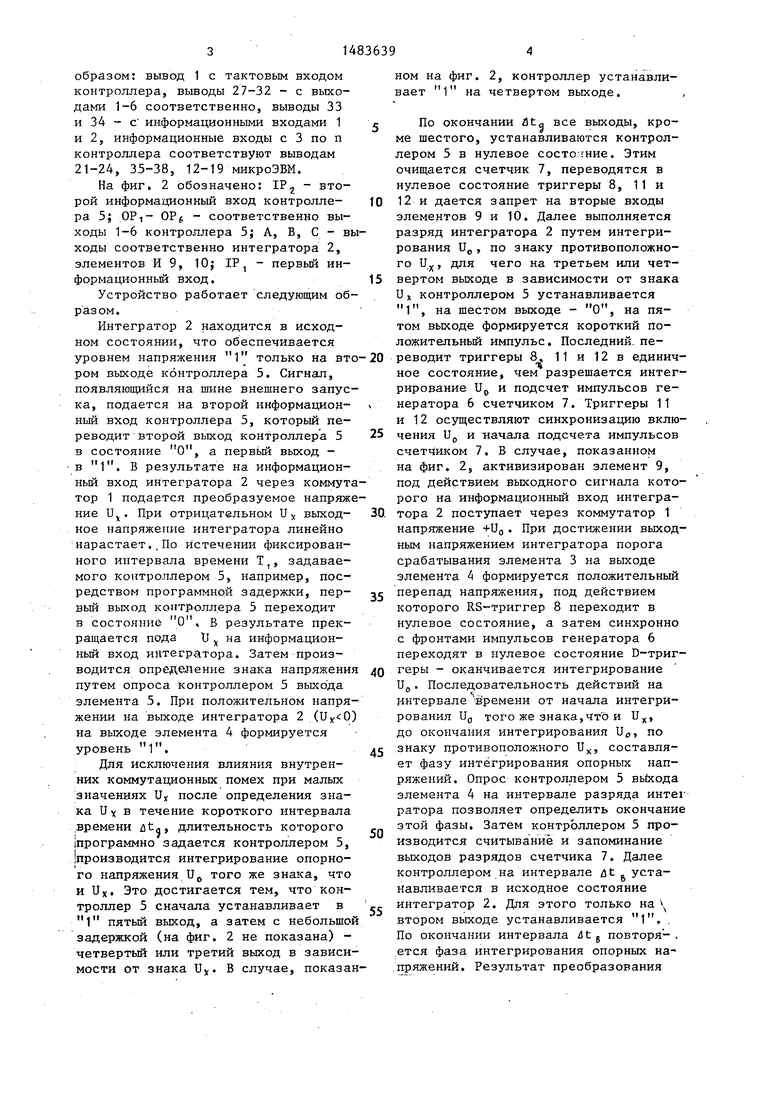

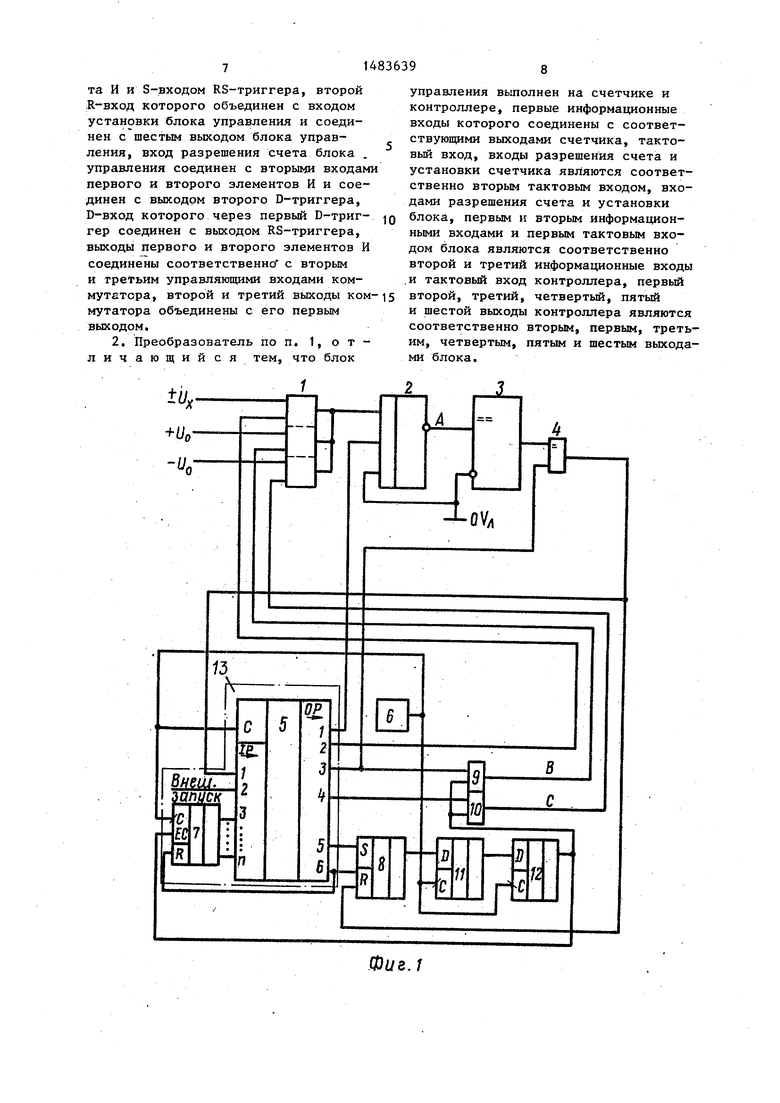

На фиг. 2 обозначено: 1Р2 - второй информационный вход контролле- ра 5; OPt- ОР - соответственно выходы 1-6 контроллера 5; А, В, С - выходы соответственно интегратора 2, элементов И 9, 10; IP, - первый информационный вход.

Устройство работает следующим образом.

Интегратор 2 находится в исходном состоянии, что обеспечивается уровнем напряжения 1 только на вто ром выходе контроллера 5. Сигнал, появляющийся на шине внешнего запуска, подается на второй информацион- ный вход контроллера 5, который переводит второй выход контроллера 5 в состояние О, а первый выход - в 1. В результате на информационный вход интегратора 2 через коммутатор 1 подается преобразуемое напряжение Ux. При отрицательном Ux выход- ное напряжение интегратора линейно нарастает.,По истечении фиксированного интервала времени Т15 задаваемого контроллером 5, например, посредством программной задержки, пер- вый выход контроллера 5 переходит в состояние О, В результате прекращается пода U х на информационный вход интегратора. Затем производится определение знака напряжения путем опроса контроллером 5 выхода элемента 5. При положительном напряжении на выходе интегратора 2 () на выходе элемента 4 формируется уровень 1.

Для исключения влияния внутренних коммутационных помех при малых значениях U после определения знака U у в течение короткого интервала времени dt, длительность которого программно задается контроллером 5, производится интегрирование опорного напряжения U0 того же знака, что и Ux. Это достигается тем, что контроллер 5 сначала устанавливает в 1 пятый выход, а затем с небольшой задержкой (на фиг. 2 не показана) - четвертый или третий выход в зависимости от знака Ux. В случае, показанном на фиг. 2, контроллер устанавливает 1 на четвертом выходе.

По окончании utq все выходы, кроме шестого, устанавливаются контроллером 5 в нулевое состо:ние. Этим очищается счетчик 7, переводятся в нулевое состояние триггеры 8, 11 и 12 и дается запрет на вторые входы элементов 9 и 10. Далее выполняется разряд интегратора 2 путем интегрирования U0, по знаку противоположного Ux, для чего на третьем или четвертом выходе в зависимости от знака U x контроллером 5 устанавливается 1, на шестом выходе - О, на пятом выходе формируется короткий положительный импульс. Последний переводит триггеры 8, 11 и 12 в единичное состояние, чем разрешается интегрирование U0 и подсчет импульсов генератора 6 счетчиком 7. Триггеры 11 и 12 осуществляют синхронизацию включения U0 и начала подсчета импульсов счетчиком 7. В случае, показанном на фиг. 2, активизирован элемент 9, под действием выходного сигнала которого на информационный вход интегратора 2 поступает через коммутатор 1 напряжение +U0. При достижении выходным напряжением интегратора порога срабатывания элемента 3 на выходе элемента 4 формируется положительный перепад напряжения, под действием которого RS-триггер 8 переходит в нулевое состояние, а затем синхронно с фронтами импульсов генератора 6 переходят в нулевое состояние D-триг геры - оканчивается интегрирование U0. Последовательность действий на интервале времени от начала интегрирования U0 того же знака,что и Ux, до окончания интегрирования U0, по знаку противоположного Ux, составляет фазу интегрирования опорных напряжений. Опрос контроллером 5 выхода элемента 4 на интервале разряда инте ратора позволяет определить окончани этой фазы. Затем контроллером 5 производится считывание и запоминание выходов разрядов счетчика 7. Далее контроллером на интервале dt устанавливается в исходное состояние интегратор 2. Для этого только на втором выходе устанавливается 1. По окончании интервала ut в повторя- , ется фаза интегрирования опорных на-1 пряжений. Результат преобразования

5 1

формируется контроллером 5 как разность кодов, полученных при первом и втором выполнении фазы интегрирова ния опорных напряжений.

При первом выполнении фазы интегрирования опорных напряжений длитель ность Т2 разряда интегратора равна

V TiO 4ti + 4t

о

(1)

где Tf - длительность интегрирования

преобразуемого напряжения; U0 - опорное напряжение; Ux преобразуемое напряжение; &t1 - приращение длительности Т за счет интегрирования Ue на интервале dt.; Ati - приращение 14 из-за неидеальности элемента сравнения и задержки включения U0. Поскольку повторение фазы интегрирования опорных напряжений следует непосредственно после интервала иt e и занимает малый промежуток времени, то условия работы элемента 3 практически не изменяются. Поэтому при вто ром выполнении фазы интегрирования опорных напряжений длительность Т разряда интегратора равна

Т, и t7 + &t..

(2)

Учитывая кодирование временных интервалов Т4 и Т Ј , выражения (1) и (2) можно представить в виде:

NI - N,2 + /IN, + N7 + qt; (3)

О

N - 4N, + dN, + q

(4)

где q t и q - погрешности дискретности при кодировании соответственно интервалов Т 2 и Т г .

Результат преобразования Nx определяется как разность N - N согласно формулам (3) и (4):

U

N, N, -i + (q,- qa). (5)

Таким образом, результат преобразования АЦП оказывается свободным от погрешностей, обусловленных не- идеальностью элемента 3 и задержкой включения опорного напряжения, с точностью до значения (q.,-q,), которое определяется разрешающей способ-

836396

ностью АЦП, Погрешность АЦП из-за неидеальности элемента 3 и задержки включения может достигать 1000 ступеней квантования. В предлагаемом

5 АЦП, как следует из формулы (5),

погрешность уменьшается до 1 ступени квантования. Указанное преимущество обеспечивает повышение точности и

10 стабильности АЦП и цифровых приборов на их основе, а также позволяет снизить требования к параметрам элемента 3 и устранить связанные с рассмотренной погрешностью ручные калибро15 |вочные операции и cociBei.. вующие им регулировочные элементы.

Формула изобретения

1, Интегрирующий аналого-цифровой 20 преобразователь, содержащий коммутатор, первый, второй и третий информационные входы которого являются соответственно входной шиной и шинами напряжения положительной и отрица- 25 тельной полярности, первый выход коммутатора соединен с информационным входом интегратора, вход начального значения интегрирования которого объединен с первым входом элемента срав- 30 нения и является шиной нулевого потенциала, выход интегратора соединен . с вторым входом элемента сравнения, генератор импульсов, выход которо о соединен с первым тактовым входом 5 блока управления, первый выход которого соединен с первым управляющим входом коммутатора, отличающийся тем, что, с целью повышения точности и стабильности, в него 40 введены элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, два D-триггера, два элемента И, RS-триг- гер, второй выход блока управления соединен с входом установки в исходное состояние интегратора, третий 4g выход соединен с первым входом первого элемента И и первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом элемента сравнения, а выход соединен с перед вым R-входом RS-триггера и первым информационным входом блока управления, второй информационный вход которого является шиной внешнего запуска, второй тактовый вход блока управления

объединен с его первым тактовым входом, с входами первого и второго D- триггеров,четвертый и пятый выходы блока управления соединены соответственно с первым входом второго элемента И и S-входом RS-триггера, второй R-вход которого объединен с входом установки блока управления и соединен с шестым выходом блока управления, вход разрешения счета блока . управления соединен с вторыми входами первого и второго элементов И и соединен с выходом второго D-триггера, D-вход которого через первый D-триг- гер соединен с выходом RS-триггера, выходы первого и второго элементов И соединены соответственно с вторым и третьим управляющими входами коммутатора, второй и третий выходы ком мутатора объединены с его первым выходом.

2. Преобразователь по п. 1, отличающийся тем, что блок

5

управления выполнен на счетчике и контроллере, первые информационные входы которого соединены с соответствующими выходами счетчика, тактовый вход, входы разрешения счета и установки счетчика являются соответственно вторым тактовым входом, входами разрешения счета и установки блока, первым и вторым информационными входами и первым тактовым входом блока являются соответственно второй и третий информационные входы и тактовый вход контроллера, первый второй, третий, четвертый, пятый и шестой выходы контроллера являются соответственно вторым, первым, третьим, четвертым, пятым и шестым выходами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь совмещенного интегрирования | 1989 |

|

SU1695503A1 |

| Интегрирующий аналого-цифровой преобразователь | 1988 |

|

SU1681384A1 |

| Интегрирующий аналого-цифровой преобразователь | 1989 |

|

SU1633493A1 |

| ПРЕОБРАЗОВАТЕЛЬ АНАЛОГ-КОД С ИНДУКТИВНЫМ ДАТЧИКОМ | 1992 |

|

RU2065665C1 |

| Аналого-цифровой преобразователь совмещенного интегрирования | 1991 |

|

SU1785075A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1695499A1 |

| СПОСОБ ИНТЕГРИРУЮЩЕГО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ НАПРЯЖЕНИЯ | 2005 |

|

RU2294595C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2062549C1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1481887A1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012131C1 |

Изобретение относится к цифровой электроизмерительной технике и может быть использовано в цифровых приборах и измерительных информационных системах. Изобретение позволяет повысить точность и стабильность интегрирующего аналого - цифрового преобразователя путем автоматической компенсации в каждом цикле преобразования погрешностей, вызванных неидеальностью элемента сравнения и задержкой включения опорного напряжения UO. После окончания интегрирования интегратором 2 преобразуемого напряжения UX и определения его знака под управлением контролера 5 реализуется фаза интегрирования UO: сначала в течение небольшого фиксированного интервала времени интегрируется UO, по знаку совпадающее с UX, а затем - UO, по знаку противоположное UX, разряжающее интегратор. Момент разряда интегратора определяется элементом 3. Длительность разряда интегратора кодируется, и код запоминается в контролере 5. Последний затем устанавливает интегратор 2 в исходное состояние. Далее повторяется фаза интегрирования UO. Результат преобразования формируется контролером 5 как разность кодов, полученных при первом и втором интегрировании UO. 2 ил.

±и

+и, -и

г

Фиг.1

Фиг. 2

| Высокочастотная цифровая измерительная система постоянного тока: Экспресс информация ВИНИТИ, сер | |||

| Контрольно-измерительная техника, вып | |||

| Устройство для сортировки каменного угля | 1921 |

|

SU61A1 |

| Прибор с двумя призмами | 1917 |

|

SU27A1 |

| Бухтияров Г.Д | |||

| Аналого-цифровые преобразователи | |||

| М.: Сов.радио, 1980, с | |||

| Прибор для запора стрелок | 1921 |

|

SU167A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1989-05-30—Публикация

1987-05-18—Подача