i

л

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр двоичного сигнала | 1986 |

|

SU1415430A1 |

| Цифровой асинхронный регенератор дискретных сигналов | 1990 |

|

SU1788582A1 |

| Цифровой фазометр | 1989 |

|

SU1709234A1 |

| Устройство синхронизации | 1979 |

|

SU773944A1 |

| Устройство автоматической подстройки частоты | 1989 |

|

SU1698987A1 |

| Цифровое фазосдвигающее устройство | 1988 |

|

SU1531202A1 |

| ПРИЕМНИК ДИСКРЕТНОЙ ИНФОРМАЦИИ С АВТОМАТИЧЕСКИМ СОГЛАСОВАНИЕМ СКОРОСТЕЙ ПЕРЕДАЧИ И ПРИЕМА | 2003 |

|

RU2249919C2 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ ПОЛОЖЕНИЕМ ТРАВЕРСЫ ГИДРАВЛИЧЕСКОГО ПРЕССА | 1992 |

|

RU2006370C1 |

| Эхолот | 1981 |

|

SU1054809A1 |

| Устройство для приема сигналов с однократной относительной фазовой манипуляцией | 1985 |

|

SU1317682A1 |

Изобретение относится к радиотехнике. Цель изобретения - повышение точности фильтрации. Цифровой фильтр содержит элемент И-НЕ 1, элемент ИЛИ-НЕ 2, реверсивный счетчик 3, блок 4 сравнения и RS=триггеры 5 и 6. Цифровой фильтр позволяет сформировать на выходе сигнал, длительность которого равна длительности входного сигнала. Цель достигается введением элемента ИЛИ-НЕ 2, блока 4 сравнения и RS=триггера 6, с помощью которых подавляются помехи типа ложный импульс и пропадание импульса, а также пакеты помех. 2 ил.

;о о

о

ел

Фиг.1

3149

Изобретение относится к радиотехнике и может быть использовано для фильтрации импульсных сигналов.

Цель изобретения - повьппение точности фильтрации.

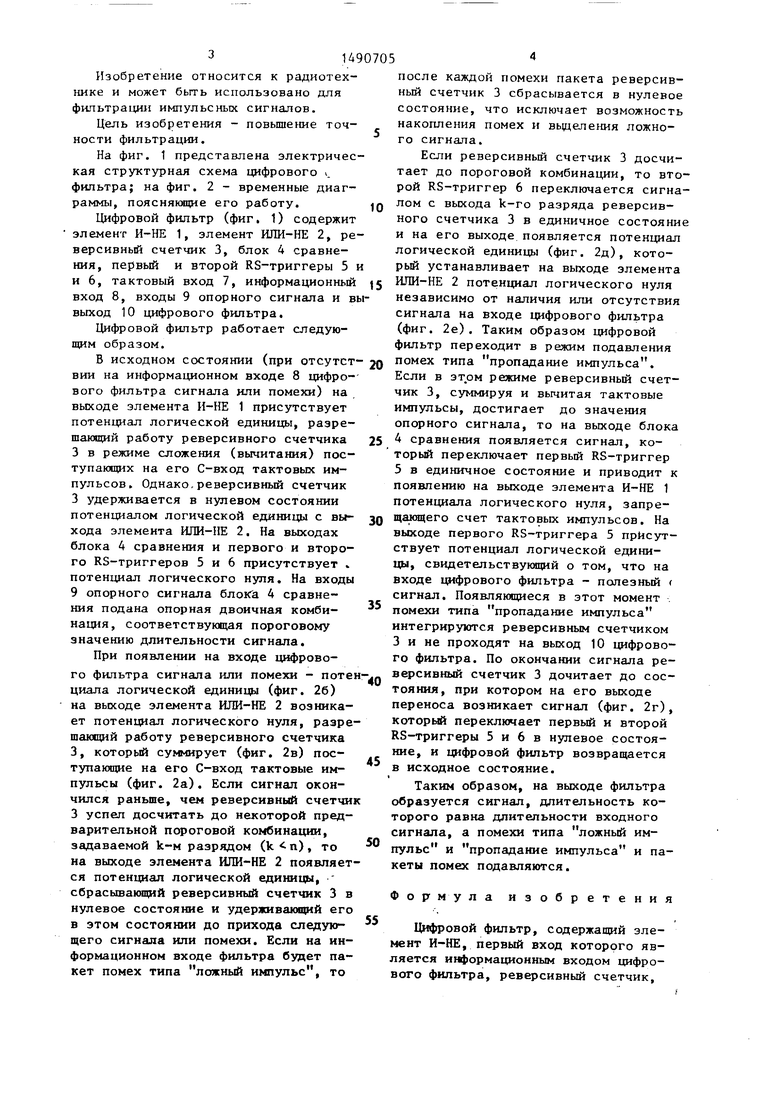

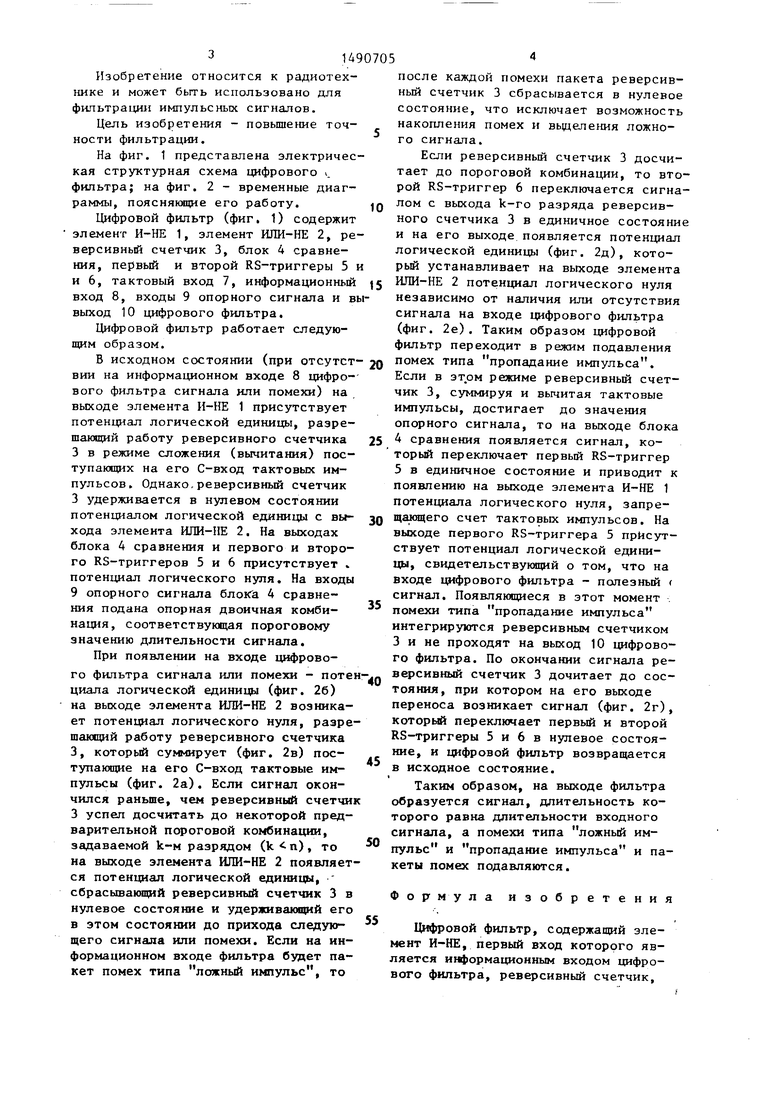

На фиг. 1 представлена электрическая структурная схема цифрового i. фильтра; на фиг, 2 - временные диаграммы, поясняющие его работу.

Цифровой фильтр (фиг. 1) содержит элемент И-НЕ 1, элемент ИЛИ-НЕ 2, реверсивный счетчик 3, блок 4 сравнения, первый и второй RS-триггеры 5 и 6, тактовый вход 7, информационный вход 8, входы 9 опорного сигнала и в выход 10 цифрового фильтра.

Цифровой фильтр работает следующим образом.

В исходном состоянии (при отсутст ВИИ на информационном входе 8 цифрового фильтра сигнала или помехи) на выходе элемента И-НЕ 1 присутствует потенциал логической единицы, разрешающий работу реверсивного счетчика 3 в режиме сложения (вычитания) поступающих на его С-вход тактовых импульсов. Однако,реверсивный счетчик 3 удерживается в нулевом состоянии потенциалом логической единицы с выхода элемента ИЛИ-ПЕ 2, На выходах блока 4 сравнения и первого и второго RS-триггеров 5 и 6 присутствует . потенциал логического нуля. На входы 9 опорного сигнала блока 4 сравнения подана опорная двоичная комбинация, соответствующая пороговому значению длительности сигнала.

При появлении на входе цифрового фильтра сигнала или помехи - поте циала логической единицы (фиг. 2б) на выходе элемента ИЛИ-НЕ 2 возникает потенциал логического нуля, разрешающий работу реверсивного счетчика 3, которьй суммирует (фиг. 2в) поступающие на его С-вход тактовые импульсы (фиг. 2а). Если сигнал окончился раньше, чем реверсивный счетчи 3 успел досчитать до некоторой предварительной пороговой комбинации, задаваемой k-M разрядом (k п), то на выходе элемента ИЛИ-НЕ 2 появляется потенциал логической единицы, сбрасывающий реверсивный счетчик 3 в нулевое состояние и удерживаю1ций его в этом состоянии до приходе следую щего сигнала или помехи. Если на информационном входе фильтра будет пакет помех типа ложный импульс, то

5

0

д

0

5

5

0

5

после каждой помехи пакета реверсивный счетчик 3 сбрасывается в нулевое состояние, что исключает возможность накопления помех и вьщеления ложного сигнала.

Если реверсивный счетчик 3 досчитает до пороговой комбинации, то второй RS-триггер 6 переключается сигналом с выхода k-ro разряда реверсивного счетчика 3 в единичное состояние и на его выходе появляется потенциал логической единицы (фиг. 2д), который устанавливает на выходе элемента ИЛИ-НЕ 2 потенциал логического нуля независимо от наличия или отсутствия сигнала на входе цифрового фильтра (фиг. 2е). Таким образом цифровой фильтр переходит в режим подавления помех типа пропадание импульса. Если в эт.ом режиме реверсивный счетчик 3, суммируя и вычитая тактовые импульсы, достигает до значения опорного сигнала, то на выходе блока

4сравнения появляется сигнал, который переключает первый RS-триггер

5в единичное состояние и приводит к появлению на выходе элемента И-НЕ 1 потенциала логического нуля, запре- щакяцего счет тактовых импульсов. На выходе первого RS-триггера 5 присутствует потенциал логической единицы, свидетельствующий о том, что на входе цифрового фильтра - полезный ( сигнал. Появляющиеся в этот момент помехи типа пропадание импульса интегрируются реверсивным счетчиком 3 и не проходят на выход 10 цифрового фильтра. По окончании сигнала реверсивный счетчик 3 дочитает до состояния, при котором на его выходе переноса возникает сигнал (фиг. 2г), который переключает первый и второй RS-триггеры 5 и 6 в нулевое состояние, и цифровой фильтр возвращается в исходное состояние.

Таким образом, на выходе фильтра образуется сигнал, длительность которого равна длительности входного сигнала, а помехи типа ложный импульс и пропадание импульса и пакеты помех подавляются.

Фор м у па изобретения

Ци|))ровой фильтр, содержащий элемент И-НЕ, первый вход которого является информационным входом цифрового фильтра, реверсивный счетчик.

первый RS-трнггер, S-вход которого соединен с вторым входом элемента И-НЕ, а выход является выходом цифрового фильтра, отличающий- с я тем, что, с целью повьппения точности фильтрации, введены блок сравнения, выход которого соединен с S-входом первого RS-триггера, последовательно соединенные второй RS- триггер, S-вход которого соединен с выходом k-ro разряда реверсивного счетчика, и элемент ШШ-НЕ, второй вход которого соединен с первым вхоППППП I 1П п 1 п 1ПГ }

/1/1/1/1/1

дом элемеич а И-НЕ, а выход - с R-ь.. - дом реверсивного счетчика, вход } - равления которого соединен с вторым входом элемента ШПННЕ, вход разрешения - с выходом элемента И-НЕ, счетный вход является тактовым входом . цифрового фильтра, выход переноса со4 единен с К-входами первого и второго RS-триггеров, а выходы п разрядов (ki n) соединены с первыми входами блока сравнения, вторые входы которого являются входами опорного сигнала цифрового фильтра.

Фиг. 2

| СПОСОБ ЛЕЧЕНИЯ МАЛЯРИИ С ПОМОЩЬЮ ТЕРАПЕВТИЧЕСКОЙ КОМБИНАЦИИ ИНГИБИТОРОВ ТЕЛОМЕРАЗЫ (ИМАТИНИБА МЕЗИЛАТ) И АРТЕМЕТЕРА | 2019 |

|

RU2722981C1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-06-30—Публикация

1987-06-24—Подача