4

СО со

СП а

Изобретение относится к электроизмерительной технике и может быть использовано в энергетических инфор-. мационно-измерительных системах.

Цель изобретения - повышение точности измерения электрических параметров.

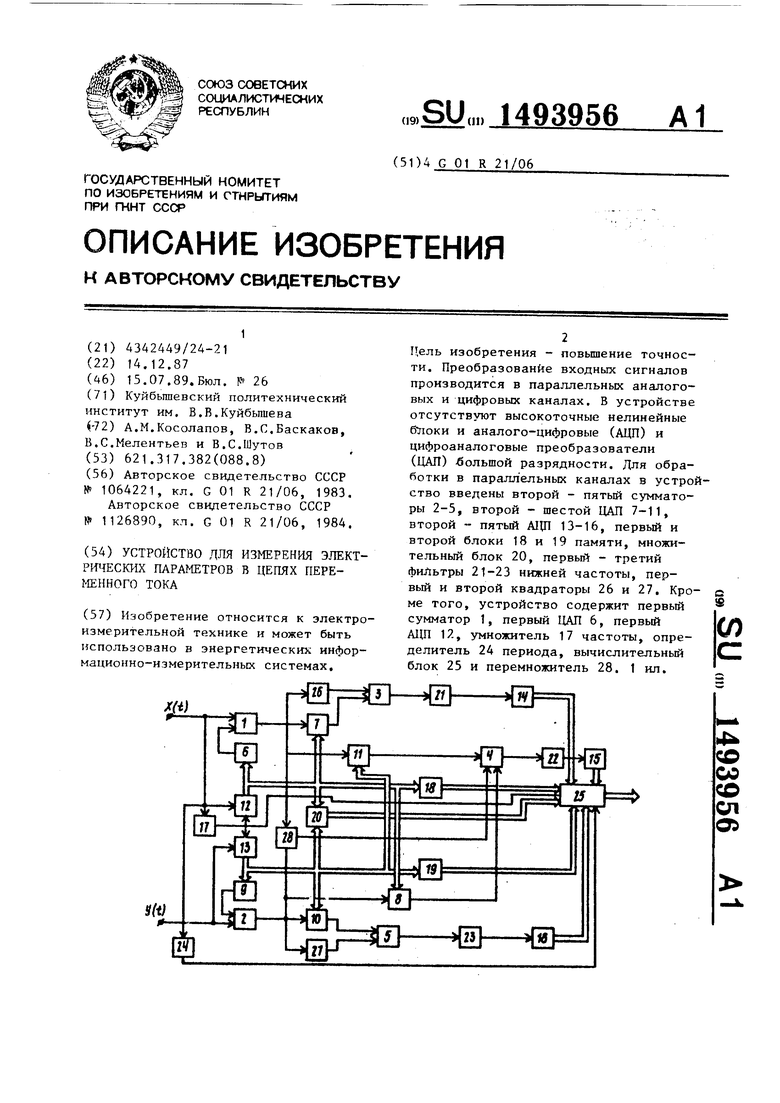

На чертеже представлена структурная схема устройства для измерения электрических параметров в цепях переменного тока.

Устройство содержит первый-пятый аналоговые сумматоры 1-5, первый-шес- той цифро-аналоговые преобразователи (ЦДЛ) 6-11, первый-пятый аналого-цифровые преобразователи (АЦП) 12-16, умножитель 17 частоты, первый и второй блоки 18 и 19 памяти, множительный блок 20, первый-третий фильтры 21-23 нижних частот (ФНЧ), определитель 24 периода, вычислительный блок 25, первый и второй квадраторы 26 и 27 и перемножитель 28, причем первый вход первого сумматора 1 соединен с выходом первого ЦАП 6,кодовые входы которого соединены с выходами первого АЦП 12, тактирующий вход которого соединен с выходом умножителя 17 частоты и тактирующим входом вычислительного блока 25, дополнительный тактирующий вход которого соединен с выходом определителя 24 периода, вход которого соединен с входом умножителя 17 частоты и подключен к входной шине напряжения контролируемой цепи, вход первого АЦП 6 соединен с входной шиной напряжения контролируемой цепи и вторым входом первого сумматора 1, выход которого соединен с первым входом перемножителя 28, входом первого квадратора 26, аналоговым входом шестого ЦАП 11 и аналоговым входом второго ЦАП 7, кодовые входы которого соединены с выходами первого АЦП 12, входами первого сомножителя множительного блока 20, кодовыми входами третьего ЦАП 8 и входами первого блока 18 памяти, а выход - с первым входом третьего сумматора 3, в.торой вхо которого соединен с выходом первого квадратора 26, а выход - с входом первого ФИЧ 21, выход которого соединен с входом третьего АЦП 14, выходы которого соединены с четвертыми кодовыми входами вычислительного блока 25, третьи кодовые входы которого соединены с выходами множительного

0

5

0

5

0

5

0

5

вхс)дами чстверто- 9,10 н 11

С)

блокЛ 20, входы BTopcjro сомиожи которого соединены с выходами вто го АЦП 13, кодовыми го, пятого и шестого ПАП и входами второго блока 1У памяти, вькоды которого гоедижмчь гг; нторьгми кодовыми входами вычислительиого блока 25, выход четвертого ЦЛП 9 соединен с первым второго сумматора 2, второй вход Koiojiorfi соединен с входной шиной тока контролируемой цепи и входом второго АПП i5, а выход - с вторым входом пиремножи- теля 28, аналоговыми вхо;ьчми третьего и пятого ПАП 8 и 10 и нхолом второго квадратора 27, выход которого соединен с первым uHvrir;) сумматора 5j второй вход которого соединен с выходом пятого ПАП 10, а выход - с входом третьего ФНЧ 23, выход которого соединен г входом пятого 16, выходы которого сс11:динены с шестыми кодовыми входами вычислительного блока 25, тактирующий вход которого соединен с тактируюпгим входом второго АЦП 13, выход перемпожите- ля 28 соединен с вх15дом четвертого сумматора 4 второй и третий входь) которого соединены с выхода - и третьего и шестого ЦАП Я и 11, а выход - с входом второго ФИЧ 22, выход которого соединен с входом четвертого АЦП 15, выходы которого соединены с пятыми кодовыми входами вычислительного блока 25, первые кодовые входы которого Соединены с выходами первого блока 18 памяти, а выходы являются выходом устройства

Устройство для измерения электрических параметров в цепях переменного тока, работает слг дующим образом.

Сигнал x(t)KyU(t) , cooТ1 етству - ший напряжению U(,) конгг)о.1П1руемой цепи, подается:на вход с гмма- тора 1, на первый вход АПП 12, на вход определителя 24 периода. Сигнал y(t)K.i(t),соответствующий току i(t) контролируемой цепи, подается на первые входы сумматора 2 и А1Ц113,

На тактирующие входы АЦП 12, 13 и вычислительного блока 25 подается сигнал с выхода умножителя 17 частоты. На выходе АЦП 12 сформируется код NJ, который при посгуплении очередного тактирующего импульса подается на цифровые входь ПАП 6,7,8, а также на вход блока 18 памяти и вход

первого Г(1МИ(гжнтеля множительного блока 20. На вьгхоле ЦЛГ1 6, в соот- нетстнии с кодом N, сформируется сигнал Xj, к(торьп} подается на второй вход су чматора 1 . На вьгходе сумматора 1 будет действовать сигнал x(t)-Xil. На вьгходе ,ЛГ1 13, в зависимости от неличины сигнала y(t), сформируется код TJ . , который при поступлении пчс-р(. дного тактирующего импульгл, подается на управляющие (цифровые) входы ЦАП 9,10,11, а также на вход блока 19 памяти и вход пт(;рого сомножите1тя множительного блока 20. На вьгходе ЦАП - 9, в соот- ветстиии с кодо N: сформируется сигнал Y;, который подается на второй вход сумматора 2. На вьгходе сумматора 2 будет действовать сигнал ty(t)- -Y. . АналогопьпЧ сигнал x(t)-X- подается на входы: первого квадратора 26, НАЛ 7,11, первый вход перемножителя 28, Аналоговый сигнал ГУ(t)-Yj подается на входы: второго квадратора 27, ЦАП 8, 10, второй вход перемножителя 28. На выходах перечисленных бпоков будут действовать сигналы:

х Ktax(t)-xj

Х, KiN.TxCt) Х| Х„ K,,N,x(t)-. J Хп (t:)Y, Xj K8N,y(t)-Y,J Х„ К,, N,ty(t)-Y Х,. K,,x(t)(t)-Y, где i, j - номера опорных сигналов в каналах X и У соответственно .

Г :сли положить ко-чффициенты переда -ш указанных блоков равнь ми K. K,Ni-2X,;K,,N.Yj;K,f 1 ; KjN, X,.;K,.N j 2Y ; , TO их выходные сигЬалы запишутся в виде: X Cx(t) - Х,. X (t)- Х,1 X,, YJ tx(t)- XiJ X,, Cy(t)-Yjj Х, (t)-YjJ Х,„ (t)-Y, X;,tx(t)(t)-Y: Одновременно будут сформированы спедуюгаие цифровые сигналы: на выходе блока 18 памяти сигнал ,соответствующий величине на вьхо- де блока 19 памяти - сигнал ,соот петствующий величине Yу, на выходе множительного блока 20 сигнал N,, соответствующий величине iYj, которые подаются на первьп, HTopoii, третий кодовые входы вычислительного блока 25 соответственно.

Сигналы X .. подаются на первый и второй входы сумматора 3, выход которого через ФНЧ 21 соединен с входом АЦП 14. На входе 14 действует сигнал

10

Хи (t)(t)-X.)dt,

а выходе - код N , соответствующие сигналу Х,

Сигналы У,, Х |подаются на первый,второй и третий входы сумматора 4,выход которого через ФНЧ 22 соединен с входом АЦП-15. На выходе

АДП 15 действует сигнал:

Х,, )(t).,y(t) г- YJ+ (t),

а на его вькоде - код N ,, соответствующий сигналу Х,5 .

Сигналы Х,д подаются на первый и второй входы сумматора 3, выход которого через ФНЧ 23 соединен с вхо- ом АЦП 16, На выходе АЦП 16 действует сигнал: г

flpY/ y(t)-Y,J 4y(t)-Yj dt, a на его выходе - код N , соответ- ствуклчий сигналу X,. .

7о

Сигналы N ,,, NJJ , M,j5 подаются на четвертьп, пятый и шестой кодовые входы вычислительного блока 25, в кото- ром осуществляется их цифровое интегрирование за период входного сигнала Т

N, i,(N,,),(1), (N,J,(2)

N;,- i (N,3)(3)

где п - число тактирующих импуЯьсов на выходе умножителя 17 частоты за период входного сигнала.

Затем в вычислительном блоке 25 вьтолняются операции суммирования сле

ующих сигналов (N,) ° 1

(N25)2 N,+ N,i (5); ()3 Nit (6)

Учитывая линейность операции интегрирования, результаты суммирования будут соответствовать следующим чинам:

т1

Т

(N.P. )-X.425.x(t)-l

+ Xi}dt jxVt) dt ;

Т

(N ,5)1 l(Lx(t)-X,Ji:y(t)-Yj

+ (t) - Vj.+ Y,x(t)-X, +X,Yj|dt

; J x(t)y(t)dt;

О

т (гРз Т I y(t)-Y, (t)- v. dt S y4t)dt.

При выполнении условия К К получим

- 1

N

,5)1 f S (t)dt,

(NM),NP ju(t)i(t)dt ;

- о

(N,,)3 i i (t)dt. e

В ходе дальнейшей обработки кодов, производимой в вычислительном блоке 25, выполняются следующие операции:

извлечение квадратного корня из сигналов ( 15- з Р вычис- Ленин действующих значений тока и напряжения соответственно:

вал времени /ST, за который определяется величина энергии

N Е dT()i dTPcp /iTNp i (7)

вычисление значений полной и реан- тинной мощности согласно соотношениям соответственно

N,

в

V(N ц),. (N)i , (8)

b«),(N,p3 -( (9)

Формула изобретения

Устройство для измерения электрических параметров в цепях переменно0

.5

0

5

0

35

40

45

50

55

ГО ТОКЛ, содержащее г1Г ремножитр 11 сумматор, первый BXCJ/; KoTopiii o .i;H- нен с вых(здом цифроаналогового прес б- разователя, кодог11 е входы которого соединены с ньгходами аналого-цифрового гтрробрачоватоля, тактиру лним яход которгзго сординен с выходом умножителя чаг готы li тактир ., Т )1(им входом вычислительного блока, дг ги пнитрлт.ный тактир т -1 ЦИ11 вход которого cocjuiHeH с выходом определителя перИ да, ход которого соединен с яходо 1 уг--л1ожителя частсзты и подкпючен к входно тине напряжения контролируемой цеии, -о т л и- ч а ю П1 е о с я тем, что, t: uoj hHi ннпиения TouiiocTH; )/ нег: ) ;|,ополк;1 тс ль- но введены BTOpoii , трети , четвертый и пятый аналого-цифровьи-- преопразова- тели, второй, третий, четвертый и пятый г1Налоговые сумТ 1атО ры, гторой, гретт1Й, четвертьй, пятый и iut.-сгой цифрсрг Л)алогоные преобр д копателя , два блока памяти, множитсл Л1Ы1Ч блок,два квадратора и три фильтра ни.жних частот, причем вход первого аналог Л циф- V oBoro преобразователя Г оединен с БходноГ (ПИКОЙ напряже1И;--1 контролируемой цепи и вторым входоч )вого сумматора, выход которого соединрн г первым входом перемнож П е,пя . ахо- дом первого квадраторг и аналоговым входом второ :; ii.Hibp - aзалогового преобразователя, кодовые вХ - ;ды которого соединены с р.ходами первого аналого-цифрового преобрато-- вателя, входами первого сомножителя множительного блока, ко, :овыми входами третьего /;иф1юанзлогов;-1го прпг брачо- вателя и входами первого С лока памяти, выход четвертого иифроаналогово-- го преобразователя соединен с первьм входом второго cyNmaTtjpa, второй вход которого соединен с вхотягл п1И}1ой то ка контролируемой пели л РХОДОМ вто- - рого аняпого-цифрового ппеоРразовате- ля, а выход - с iiTopbt -f входом перемножителя j аналоговьп ч входами третьего и пятого 1Г,ифроана,чоговьгх пре- обра эователен и входом )рого квадратора, выход второго цифроана. тогово- го преобразователя соединен с первым входом третьего сумматора, второГ вход третьего сумматора пединен с выходом первого квадратора, а вьпсад с входом первого фильтра -nmHtrx час тот, выход которого соединен с входом третьего аналого-цифрового преоб - разователя, третьи кодовые р,хо;;ы вычислительного блока соединены с выходами множительного блока, входы второго сомножителя которого соединены с выходами второго аналого-цифрового преобразователя, кодовыми входами четвертого, пятого и шестого цифро- аналоговых преобразователей и входами второго блока памяти, выходы которого соединены с вторыми кодовыми входами вычислительного блока, выходы третьего аналого-цифрового преобразователя соединены с четвертыми кодовыми входами вычислительного блока, выход перемножителя соединен с первым входом четвертого сумматора, второй и третий входы которого соединены с выходами третьего и шестого цифро- аналоговых преобразователей, а выход с входом второго фильтра нижних частот, выход которого соединен с входом четвертого аналого-цифрового пре

- g

0

образователя, выходы которого соединены с пятыми кодовыми входами вычислительного блока, первые кодовые входы которого соединены с выходами первого блока памяти, а выходы являются выходом устройства,выход второго квадратора соединен с первым входом пятого сумматора, второй вход которого соединен с выходом пятого цифро- аналогового преобразователя, а выход с входом третьего фильтра нижних частот, выход которого соединен с входом пятого аналого-цифрового преобразователя, выходы которого соединены с шестыми кодовыми входами вычислительного блока, тактирующий вход которого соединей с тактирующим входом второго аналого-цифрового преобразователя, выход первого сумматора соединен также с аналоговым входом шестого цифроаналогового преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Квадратор | 1981 |

|

SU1043676A1 |

| Аналого-цифровое множительное устройство | 1984 |

|

SU1215122A1 |

| Аналого-цифровое множительное устройство | 1984 |

|

SU1280400A1 |

| Устройство для измерения динамических характеристик | 1983 |

|

SU1168902A1 |

| Множительное устройство | 1984 |

|

SU1160442A1 |

| Гибридный функциональный преобразователь | 1980 |

|

SU879610A1 |

| Преобразователь аналог-код | 1978 |

|

SU766001A1 |

| Устройство для определения средней мощности случайных сигналов | 1986 |

|

SU1383399A1 |

| Гибридное множительное устройство | 1985 |

|

SU1325521A1 |

| СПОСОБ И УСТРОЙСТВО КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 2007 |

|

RU2352060C1 |

Изобретение относится к электроизмерительной технике и может быть использовано в энергетических информационно-измерительных системах. Цель изобретения - повышение точности. Преобразование входных сигналов производится в параллельных аналоговых и цифровых каналах. В устройстве отсутствуют высокоточные нелинейные блоки и аналого-цифровые (АЦП) и цифро-аналоговые преобразователи (ЦАП) большой разрядности. Для обработки в параллельных каналах в устройство введены второй - пятый сумматоры 2-5, второй - шестой ЦАП 7-11, второй - пятый АЦП 13-16, первый и второй блоки 18 и 19 памяти, множительный блок 20, первый - третий фильтры 21-23 нижней частоты, первый и второй квадраторы 26 и 27. Кроме того, устройство содержит первый сумматор 1, первый ЦАП 6, первый АЦП 12, умножитель 17 частоты, определитель 24 периода, вычислительный блок 25 и перемножитель 28. 1 ил.

| Устройство для измерения электрических параметров в цепях переменного тока | 1982 |

|

SU1064221A2 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Преобразователь активной мощности в код | 1983 |

|

SU1126890A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-07-15—Публикация

1987-12-14—Подача