Предлагаемое изобретение относится к информационно-измерительной техт ник1г, которая занимается созданием быстродействующей и высокоточной аппаратуры для преобразования аналрговых величин в цифровой код. Известен преобразователь напряже ния в код, в котором увеличение точности аналого-цифрового преобразования обеспечивается за счет автоматической коррекции погрешностей, возни какнцих в процессе преобразования 1 Известен так же преобразователь напряжения в код, содержащий двухпозиционный переключатель, аналогоцифровой (АЦП) и цифроаналоговые (ЦАП) преобразователи, вычислительны блок, блок памяти, электронные ключи блок управления, цифровую индикацию и регистрацию и связи между ними. Особенность данного устройства со тоит в том, что оно реализует некоторый единичный повторягсщийся процес при котором погрешности аналого-цифрового преобразования последовательн корректируются до уровня, определяющего заданную точность преобразовани Измерительный -процесс сходится, если передаточная характеристика АЦП .f(x) такова, что для всех х.,- е (х ) в рабочем диапазоне устройства аведливо условие (-i) Для скорости сходимости указанного рационногй измерительного процессправедливо соотношение: , И1) где 5 - цифровой .эквивалент истинного Кбез погрешностей) значения входной величины; - коды, полученные и-- V м в результате проведения соответственно И- 1 и и итераций. Разность (5у| 5 есть ни что иное, величина абсолютной погрешности еделения кода измеряемой величины каждой итерации. Очевидно, что больше (абсолютная погрешность образования, тем больше число итеий для достижения требуемой точноснеобходимо будет провести 2.

Недсстатком этого преобразователи является низкое быстродействие при больших значениях погрешностей тракта аналого-цифрового преобразования.

Цель изобретения - повышение быстродействия и точности преобразования аналоговой величины.

Поставленная цель достигается тем, что в Преобразователь аналог-код, содержащий переключатель, входы которог соединены соответственно с входной ши ной, с первым выходом блока управлени и с выходом цифроаналогового преобразователя, а выход с первым входом аналого-цифрового преобразователя, второй вход которого соединен со вторым выходом блока управления, первый -регистр памяти введены первый, второй « третий сумматоры, второй и третий регистры, множительный блок, делительный блок, причем выход аналого-цифрового преобразователя соединен с первыми.входами первого регистра памяти и первого сумматора, второй вход которого соединен с выходом первого регистра памяти, а выход с первыми входами множительного блока и делител ного блока, второй и третий вход которого соединены соответственнос третьим выходом блока управления и с выходом второго сумматора, а выход через множительный блок соединен с первым входом третьего сумматора, второй вход которого соединен с пер-, выми входами второго сумматора и третьего регистра памяти и с выходом второго регистра памяти,а выход со входом цифроаналогового преобразрвателя и с первым входом второго регистра памяти, второй вход которого соединен с четвёртым выходом Ълока управления, пятый выход которого соединен со вторым входом первого регистра памяти, а шестой выход со вторым. входом третьего регистра памяти, выход которого соединен со вторым входом второго сумматора.

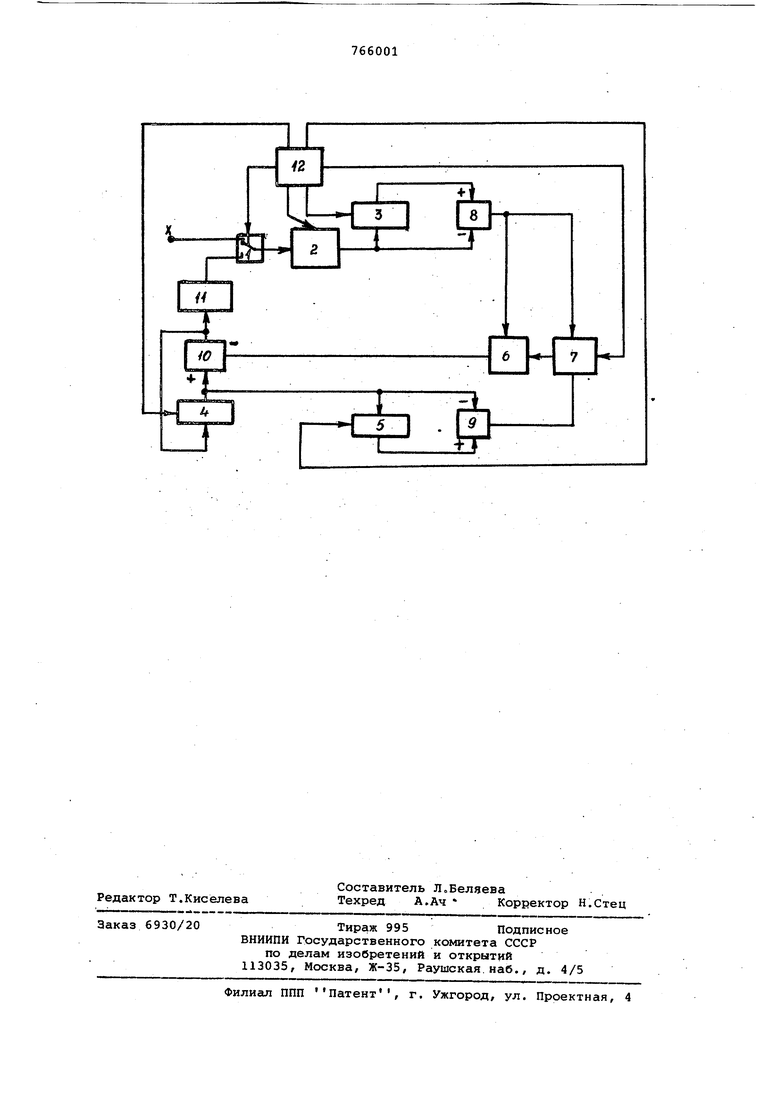

На чертеже представлена блок-схема преобразователя аналог-код.

Схема содержит переключатель 1,, аналого-цифровой преобразователь (АЦП) 2, первый 3, второй 4 и третий 5 регистры памяти, множительный блок б, делительный блок 7, первый 8, второй 9, третий 10 сумматоры, цифроаналоговый преобразователь .(ЦАП) 11 и блок12 управления.

Устройство работает следующим образе.

В исходном состоянии преобразователь 2, регистры 3,4 и 5 устанавливаются в нулевое положение, переключатель 1 - в такое положение, при котором преобразуемая величина подводится ко входу преобразователя 2, а на выходе делительного блока 7 устанавливается код единицы.

С помощью преобразователя 2 производится аналого-цифровое преобразование входной величины х. Результат преобразования, выраженный в определенгном коде о и названный намикодом нулевого приближения, через сумматоры 8 и 10, а также множительный блок б вводится преобразователем 11 и затем переписывается в регистр 4 памя.ти, после чего Зо записывается также в регистр 3. Из регистра 4 код Vo переписывается далее в регистр 5 памяти.

Передаточная характеристика цифроаналогового преобразователя 11 выбрана такой, что образующаяся в результате аналогового преобразования на его йыходе однородная с х аналоговая величина с заданной степенью точности равна воздействукнцему на ЦАП коду.

Во втором такте переключатель 1 переводится в положение, при котором выход ЦАП подключается ко входу АЦП. Производится аналого-цифровое преобразование сигнала ЦАП, равного как уже указывалось коду %. Результат аналого-цифрового преобразования (Vo) алгебраически складываясь с кодом Зо в сумматорах 8 и далее 10, образует код j первого приближения. Полученный на выходе сумматора 10 код о вводится сначала в ЦАП, а затем переписывается в регистр 4 памяти. Результат же (о) аналого-цифрового преобразования выходной величины ЦАП с выхода АЦП переписывается в регистр 3 памяти.

После установления на выходе ЦАП 11 новой величины, соответствующей коду первого приближения , в третье такте/ производится аналого-цифровое преобразование. Результат преобразования () суммируется в сумматоре 8 с хранящимися в регистре 3 результатом f(o). Разность f(%) - fCS) с выхода сумматора 8 поступает на вход блока 7. На другой его вход (вход числа-делимого) с выхода сумматора 9 поступает разность (% - V ) кодов, хран)цихся соответственно в регистрах 5 и 4 памяти. В результате обработки указанных разностей, на выходе блока 7 вместо кода единицы устанавливается код, равный отношению -9 ,

В следующем такте переключатель 1 вновь подключает преобразуемую величину X ко входу АЦП. Результат ее аналого-цифрового преобразования Jo суммируется в сумматоре 8 с хранящимся в регистре 3 кодом i ( ) . Разность (J) о далее в блоке б умножа о -Ч-1

. Реется на отношение

tVMeVf (.V1-)

зультат алгебраического суммирования с помощью сумматора 10 полученного произведения в блоке б с кодом , хранящимся в регистре 4, составляет код Зд. второго приближения.

Процесс коррекции может быть -продолжен для получения третьего результата приближения по данным 2. и -з . Для этого код (о) предыдущего приближения отбрасывается. То ест / из регистра 4 переписывается в ре гистр 5 (вместо ). Код х,, получен ный на выходе сумматора 10, вводится в ЦАП и затем переписывается в ре- . гистр 4 (вместо ). Результат преоб разования в код нового сигнала ЦАП (2) сначала участвует в опЕ|еделении нового отношения - после чего переписывается в регистр 3 (вместо (J), Вновь определяется код So (х преобразуется в код) и результат третьего приближения находят далее как: Действуя аналогичным образом результат нового VI + 1 приближения получаемый на выходе сумматора 10, опр деляется по следующей рекуррентной формуле:/ 2 Если к правой части добавить и от нять X, где X - цифровой эквивалент истинного (без погрешностей значения преобразуемой величины и проводя некоторые преобразования можно получит ) |t /.1 ( СХ) Учитывая значения t и tg перепи шем последнее выражение в виде м,ыв ,.r |-«Va|v f Выпишем выражение (1), характеризукяцее скорость сходимости-(или быст родействия) прототипа в виде: h 1- -1NПоказатель степени при разности(ц -iit) определяет скорость сходимости . итерационного процесса. Более высоко скоростью сходимости обладает тот итерационный процесс, у которого это показатель степени выше. Выражения (3) и (4) есть выражения, характеризующие скорости сходимости заявляемого устройства и прото типа. При этом итерационный процесс, характеризующийся соотношением (4) и реализуемый известным устройством, облсшает линейной сходимостью, так ,как указанный показатель степени при |разности (Зу - х) равен 1. Для предлагаемого устройства этот показатель лучше (1,618), и следовательно, предлагаемое устройство обладает значительно большим бь1стродействием. Следует отметить, что для частного случая, когда функция преобразования АЦП (х) линейная (то есть могут иметь место только аддитив.ная и мультипликативная погрешности) предлагаемое устройство в отличие от известного во всех случаях скорректирует эти погрешности за одну итерацию. То есть результат первого же приближения в предлагаемом устройстве свободен от погрешностей АЦП. Формула ./изЪбретения Преобразователь аналог-код, содерч жащий переключатель, входыкоторого соединенные соответственно с входной шиной, с первым выходом блока управления и с выходом цифро-аналогового преобразователя, а выход с первБМ входом аналого-цифрового преобразователя, второй вход которого соединен со вторым выходом блока управления, первый регистр ; памятиу отличающийс я тем, что, с целью повышения быстродействия и точности преобразования аналоговой величины введены первый, второй и третий сумматоры, второй и третий регистры, множительный блок, делительный блок, причем выход аналогоцифрового преобразователя соединен с первыми входами первого регистра памяти и первого сумматора, второй вход которого соединен с выходом первого регистра памяти, а выход с первыми входами множительного блока и делительного блока, второй и третий вход которого соединён соответственно с ретьим выходом блока управления и с выходом второго сумматора, а выход . через множительный блок соединен с первым входом третьего сумматора, второй вход которого соединен с первыми входами второго сумматора и третьего регистра памяти и с выходом второго регистра памяти а выход со входо1 цифроаналогового преобразователя и с первым входом второго регистра памяти, второй вход которого соединен с четвертым выходом блока управления, пятый выход которого соединен со вторым входом первого регистра памяти, а шестой выход со вторым входом третьего .регистра памяти, выход которого соединен со вторым входом второго сумматора . Источники информации, принятые во внимание при экспертизе 1.Алиев Т.Н. и др. Автоматическая коррекция погрешностей цифровых измерительных приборов, М., Энергия, 1975. 2.Авторское свидетельство СССР 219290, кл. Н 03 К 13/02, 03.01.67.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство преобразования аналога в код | 1980 |

|

SU890553A1 |

| Преобразователь "аналог-код | 1980 |

|

SU930649A1 |

| Устройство преобразования "аналог-код | 1979 |

|

SU834893A1 |

| Цифровой измеритель напряжения | 1977 |

|

SU677096A1 |

| Устройство для вычисления массы нефти и нефтепродуктов в резервуарах | 1983 |

|

SU1117653A1 |

| Устройство для определения статистических характеристик непрерывных случайных величин | 1981 |

|

SU1012270A1 |

| Преобразователь аналоговых величин в цифровой код | 1978 |

|

SU752789A1 |

| Устройство для автоматического регулирования формы полосы | 1984 |

|

SU1235577A1 |

| Устройство аналого-цифрового преобразования | 1987 |

|

SU1559405A2 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

Авторы

Даты

1980-09-23—Публикация

1978-11-01—Подача