СО. а:

С5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления средней мощности случайных сигналов | 1982 |

|

SU1034044A1 |

| Устройство аналого-цифрового преобразования | 1983 |

|

SU1188890A1 |

| Устройство для измерения электрических параметров в цепях переменного тока | 1987 |

|

SU1493956A1 |

| Экстраполятор видеосигнала изображения | 1989 |

|

SU1718246A1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1991 |

|

RU2013863C1 |

| Устройство для спектрально-временного анализа сигналов | 1989 |

|

SU1711109A1 |

| Устройство для решения задач оптимального управления | 1985 |

|

SU1327135A1 |

| Аналого-цифровой инкрементный дифференциатор | 1985 |

|

SU1343410A1 |

| ИЗМЕРИТЕЛЬ ПОТЕРЬ МОЩНОСТИ (ВАРИАНТЫ) | 2011 |

|

RU2467337C2 |

| Преобразователь код-напряжение | 1984 |

|

SU1197084A1 |

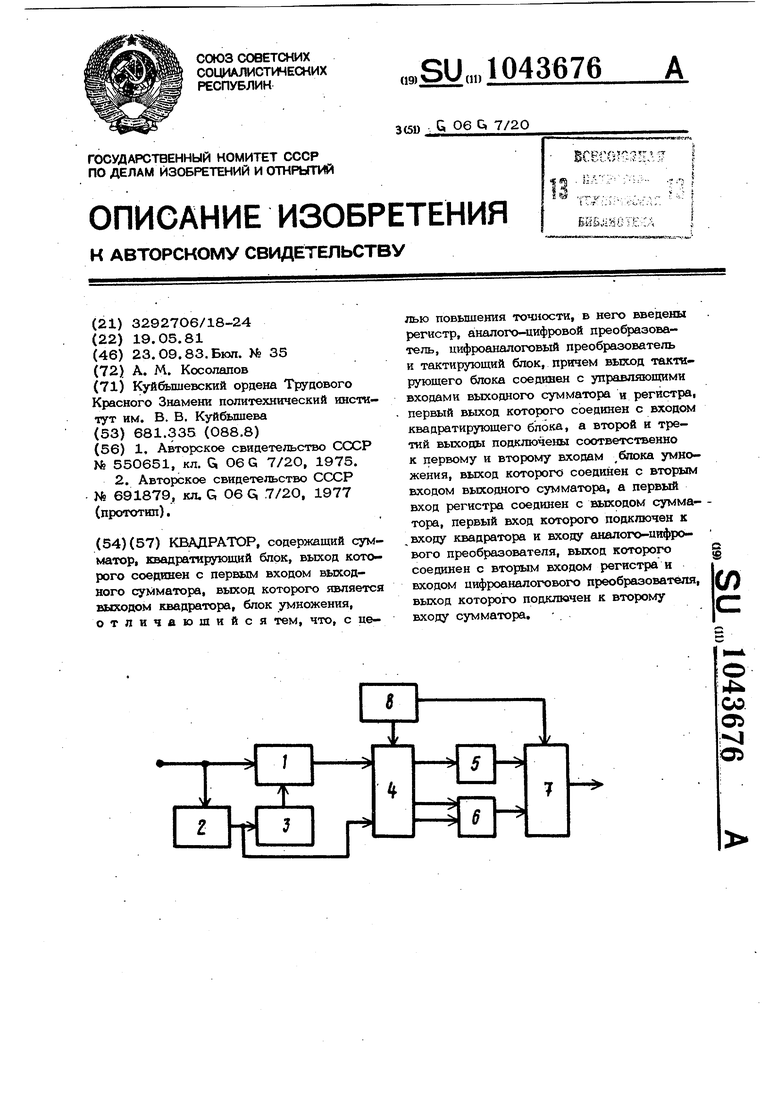

КВАДРАТОР, содержащий сумматор, квадратируюший блок, выход которого соединен с первым входом выходного сумматора, выход которого является выходом квадратора, блок умножения, отличающийся тем, что, с целью повышения точности, в него введены регистр, аналого-цифровой преобразователь, цифроаналоговый преобразователь и тактирующий блок, причем выход тактирующего блока соединен с управляющими входами выходного сумматора и регистра, . первый выход которого соединен с входом квадратирующего блока, а второй и третий выходы подключены соответственно к первому и второму входам блока умножения, выход которого соединен с вторым входом выходного сумматора, а первый вход регистра соединен с выходом сумма- тора, первый вход которого подключен к ,входу квадратора и входу аналого-иифрОвого преобразователя, выход которого соединен с вторым входом регистра и входом цифроаналогового преобразователя, ГЛ выход которого подключен к второму входу сумматора, - .

m Изобретение относится к измерительной и вычислительной технике. Известен квадратор, содержащий два сумматора, пороговые блоки, квадрати- рующий блок и ключи, входы пороговых устройств и первого сумматора соединен с входом устройства, а выход первого сумматора через квадратирующий блок и ключи соединен с входами второго сум матора, выходы пороговых устройств соединены с входами обоих сумматоров, входами ключей и друг с другом Cl 3 . Однако этот квадратор обладает недостаточной точностью и узким динамическим диапазоном при фо1 ировании на выходе цифрового сигнала. Это обусловл тем, что число дискре-гаых значений ком пенсирующего сигнала, задаваемого с пороговых устройств на вход первого сумматора, практически не может быть более двух для каждой полярности входного сигнала. Наиболее близким по техническому решению является квадратор, содержащий пороговые элементы, блок выделения модуля входного сигнала, блок определения знака входного сигнала, ключи, сумматор, квадратирующий блок, выход которого соединен с первым вхопом выхошшго сумматора, выход которого является выходом квадратрра, н блок умножения . Однако известному устройству присуща недостаточно высокая точность. 1 Целью изобретения является повьппе- ние точности. Поставленная цель достигается тем, что в квадратор, содержащий сумматор, квадратирующий блок, выход которого соединен с первым входом выходного сум матора, выход которого является выходом квадратора, блок умножения, введены регистр, аналого-цифровой, цифроаналоговый преобразователи и тактирующий блок причем выход тактирующего блока соеди нен с управляющими входами выходного сумматора и регистра, первый выход кот рого соединен с входом квадратирующего блока, а второй и третий выходы подклю чены соответственно к первому и второму входам блока умножения, выход которого соединен со вторым входом выходного сумматора, а первый вход регистра соединен с выходом сумматора, первый вход которого подключен к входу квадратора и входу аналого-цифрового преобразователя выход которого соединен со вторым входом регистра и входом цифрю- аналогового преобразователя, выход которого подключен ко второму входу сумматора. На чертеже приведена блок-юхема квадратора. Квадратор содержит сумматор 1, анаЛОГО--41ИФРОВОЙ преобразователь (АЦП) 2, цифроаналоговый преобразователь (ЦАП) 3, регистр 4, квадратнрукяций блок 5, блок 6 умножения, выходной сумматор 7, тактирующий блок 8. Квадратор работает следующим образсим. Входной сигнал X поступает на вход AUn 2 низкой точности и поеобразуется в дифровой код N 2. Входной сигнал X поступает на первый вход сумматора 1, а на второй его вход яоступает сигнал с выхода ЦАП 3, обратный по знаку относительно сигнала X. На выходе сумматоре 1 формируется сигнал F/(, где С, и С -шаги дискретизации по уровню для сумматора 1 3; N и N. -значения кодов на выходе сумматора 1 и А1Ш 2. Коды, соответствующие N и Мл ,череэ регистр 4 поступают на цифровой квадратирующий блок 5 и блок 6 умножения, где формируются коды, соответствующие ,,..N. (N..( 1 N.22 оответственно. Значения N,M, ), N 2 2 соответствуют старшим и младшим оловинам разрядов кодов для N и N ормируемых соответственно сумматором и АЦП 2. Выходной сумматор 7 прозводит сложение этих кодов, так что а его выходе формируется цифровой код N 7, пропорциональный X , с погрешостью, определяемой в основном погрещостями сумматора 1 и ЦАП 3, которые ыполняются точными, где V

-С учетом () из (2) поточим

Гс пелью сокращения аппаратурных за- 5 трат квадр тирукший блок 5 и блок 6 умвожения нспользуются многократно для реаяизацви условвя (2). Например, в nep-i

. BOM такте квадрати1 кш1им блоком 5 вое-, прой юпнтся первое слагаемое, блокс ю 6 умножения - вггорое и третье слагаемое, а выходной сумматор 7 производит их сложение и накапловает сумму. Во втором такте блоком 6 yifHOKeHHH воспроизводится четвертое и петое слагаемые, а is хвадратирукяцим блоком 5 - шестое слащемое. Выходной сумматор 7 к накоплейкому значению в первом такте суммирует четвертое, пятое и mecix e слагаемые и к KOHiiy второго такта формирует 20 результат преобразования. Тактирование

ос; шествлнется тактирующим блоком 8,

который может быть выполнен на основе генератора тактовых импульсов или распределителя импульсов.

Сумматор 1 выполнен, например, в виде последовательно соединенных анало- гового сумматора и АЦП.

Достоинством предлагаемого устройства является наличие малоразрядных блоков и низкие требования к -точности и стабильности характеристик АЦП да счет компенсаций погрешности АЦП выходном сумматоре сигналом, зависяши 1 от точной разности между входным сш налом X и сигналом с выхода ЦАП. Таким образом, .данный квадратор может быть построен на базе серийных линейных и малоразрядных цифровых интегральных схем.

Технико-экономическ эффект заклк -. чается в повышении точности Предлагаемого квадратора.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Квадратор | 1975 |

|

SU550651A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Квадратор | 1977 |

|

SU691879A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-09-23—Публикация

1981-05-19—Подача