ЧШ.

ч1Б:шчй

СО

ел

00 САЭ

Изобретение относится к вычисли-- тельной технике и может быть исни.гт-р- зовано в системах распознавания изображений .

Целью изобретения является упрощение устройства.

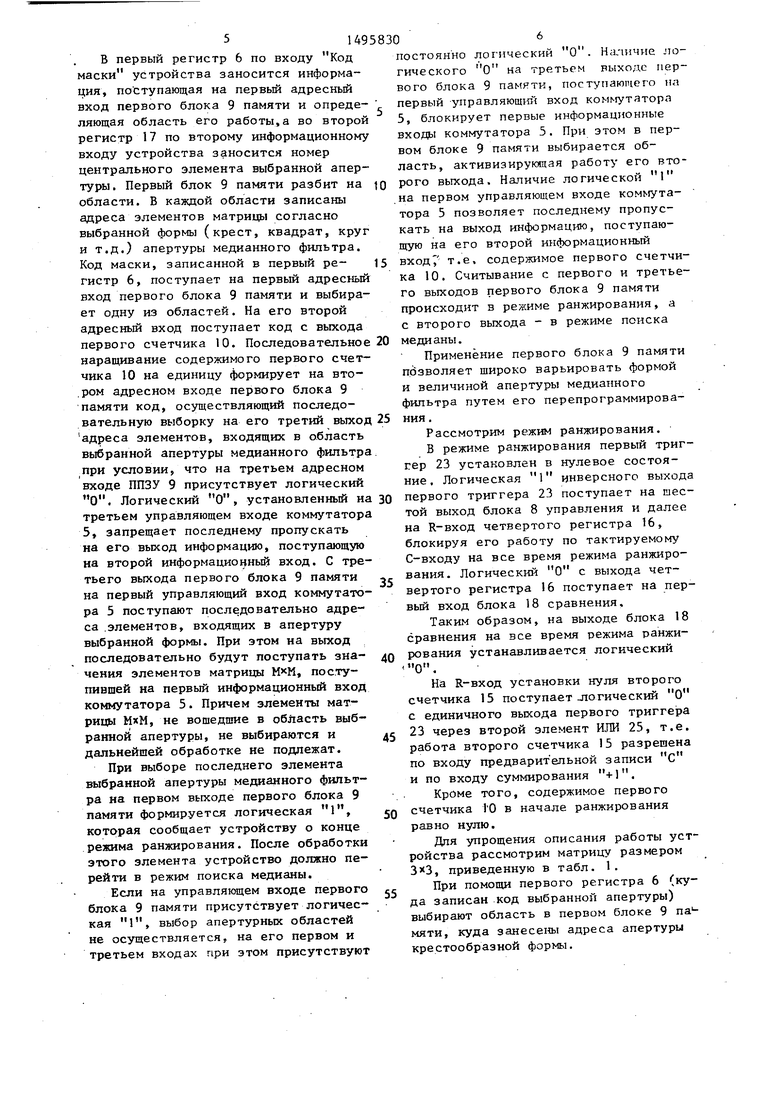

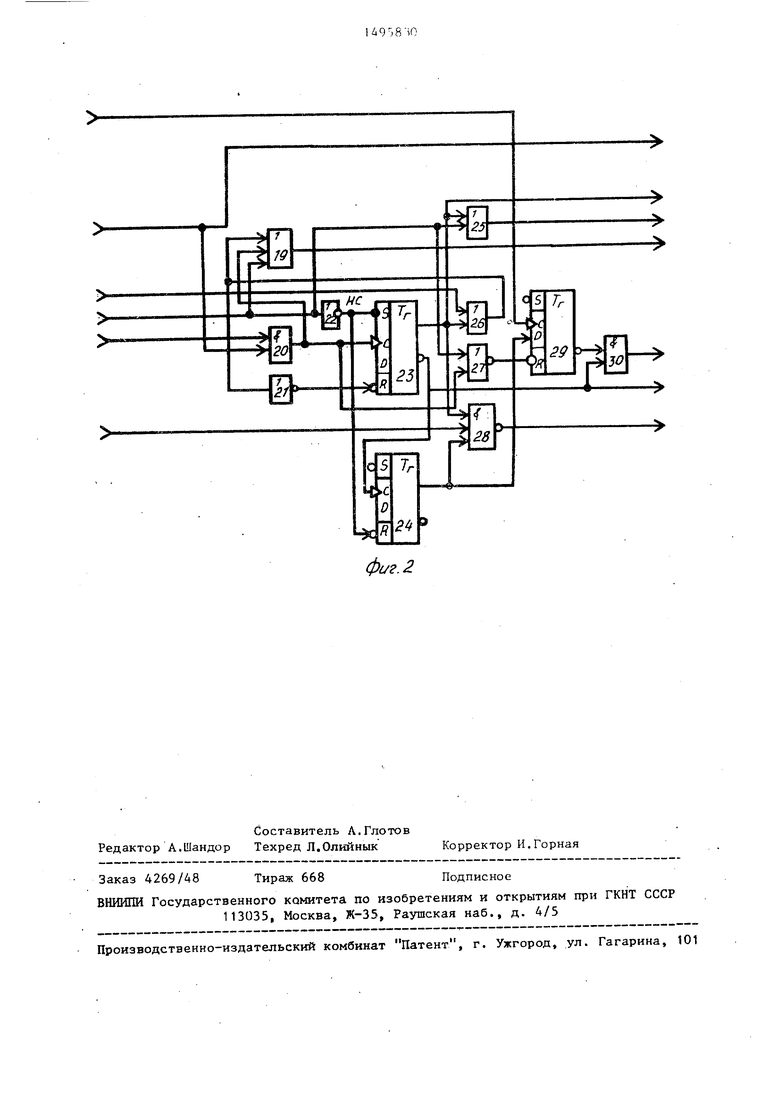

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - схема блока управления.

Устройство содержит датчик 1 сигнала, аналого-цифровой преобразователь 2, формирователь 3 апертуры, элеме,пт 4 задержки, коммутатор 5, первый регистр 6, третий регистр 7, блок 8 управления, первый блок 9 памяти, первый счетчик 10, генератор 1 импульсов, распределитель 12 импульсов, второй блок 13 памяти, сумматор

14, второй счетчик 15, четвертый регистр 16, второй регистр 17 и блок 18 сравнения.

Блок управления (фиг. 2) содержит первый элемент ИЛИ 19, первьш элемент И 20, первый 21 и второй 22 элементы НЕ, первый 23 и второй 24 триггеры, второй элемент ИЛИ 25, второй элемент И 26, третий элемент ИЛИ 27, четвертый элемент И 28, третий триггер 29 и третий элемент И 30.

Апертура устройства имеет размерность N , где М - число элементов .

Формирователь апертуры выполнен в виде последовательно соединенных регистров сдвига.

Устройство работает следующим образом.

В начале на управляю ций вход устройства поступает сигнал Сброс в виде логической 1, которая обеспечивает обнуление третьего регистра 7 первого счетчика 10 и второго счетчика 15 через первый 19 и второй 25 элементы ИЛИ по Р-входу (фиг. 2), а через элемент НЕ 22 устанавливает второй триггер 24 по R-входу в нуле- вое состояние, а триггер 23 - в единичное состояние по S-входу. Кроме этого, осуществляется процесс об нуле НИН второго блока 13 памяти. Процесс обнуления по сигналу Сброс идентичен процессу обнуления второго блока

С первого выхода датчика 1 сигналов на вход АЦП 2 периодически с интервалом времени Т поступает информация. С выхода АЦП оцифрованная информация поступает на информационный вход формирователя 3 апертуры. С второго выхода датчика 1 сигналов на тактирующий вход формирователя 3 апертуры поступает сигнал сопровождения информации, осуп(ествляющий сдвиг

13 памяти в режиме поиска медианы и

будет рассмотрен при описании режима еезаписанной информации и запись новой

поиска медианы. Отличие лишь в том,информации в первый сдвиговый регистр

что в начале работы на третьем входеформирователя 3 апертуры. Выходы форчетвертого элемента И 28 присутству-мирователя апертуры поступают на перет логический О, поступающий с еди-вый информационный вход коммутатора 5,

0

5

0

5

0

5

,,

0

5

ничного выхода второго триггера 24, которьй запрещает прохождение сигнала сопровождение выходной информации на второй выход устройства, исключая возможность считывания ложной медианы по первому выходу устройства.

Кроме того, логический О единичного выхода второго триггера 24 поступает на информационный D-вход третьего триггера 29 и при поступлении сигнала на его тактируемый С-вход последний остается в нулевом состоянии. По окончании обнуления второго блока 13 памяти первый триггер 23 устанавливается в нулевое состояние, т.е. на его инверсном выходе формируется логическая 1, которая поступает на тактируемый С-вход второго триггера 24 и устанавливает его в единичное состояние на все время работы устройства. Логическая 1 единичного выхода второго триггера 24 поступает на третий вход четвертого элемента И 28 и разрешает ему пропускать сигнал сопровождения выходной информации на второй выход устройства, а поступая- на информационный D-вход третьего триггера 29, разрешает последнему устанавливаться в единичное состояние при поступлении сигнала на вход синх- роблока 8 управления.

Кроме этого, логическая 1 инверсного выхода первого триггера 23, поступая на второй вход третьего элемента И, формирует на его выходе логическую 1, которая поступает на управляющий вход распределителя 12 импульсов и запрещает последнеь1у работу от тактовых импульсов генерато-. ра II импульсов. После этого устройство готово к работе, т.е. оно установлено в режим ранжирования.

С первого выхода датчика 1 сигналов на вход АЦП 2 периодически с интервалом времени Т поступает информация. С выхода АЦП оцифрованная информация поступает на информационный вход формирователя 3 апертуры. С второго выхода датчика 1 сигналов на тактирующий вход формирователя 3 апертуры поступает сигнал сопровождения информации, осуп(ествляющий сдвиг

В первый регистр 6 по входу Код маски устройства заносится информация, поступающая на первый адресньй вход первого блока 9 памяти и опреде- ляющая область его работы,а во второй регистр 17 по второму информационному входу устройства заносится номер центрального элемента выбранной апертуры. Первый блок 9 памяти разбит на области. В каждой области записаны адреса элементов матрицы согласно выбранной формы (крест, квадрат, круг и т.д.) апертуры медианного фильтра. Код маски, записанной в первый ре- гистр 6, поступает на первый адресный вход первого блока 9 памяти и выбирает одну из областей. На его второй адресный вход поступает код с выхода первого счетчика 10. Последовательное наращивание содержимого первого счетчика 10 на единицу формирует на вто- ,ром адресном входе первого блока 9 памяти код, осуществляющий последовательную выборку на его третий выход адреса элементов, входящих в область выбранной апертуры медианного фильтра при условии, что на третьем адресном входе ППЗУ 9 присутствует логический О. Логический О, установленный на третьем управляющем входе коммутатора 5, запрещает последнему пропускать на его выход информацию, поступающую на второй информационный вход, С третьего выхода первого блока 9 памяти на первый управляющий вход коммутатора 5 поступают последовательно адреса .элементов, входящих в апертуру выбранной формы. При этом на выход последовательно будут поступать зна- чения элементов матрицы , пос.ту- пиншей на первый информационный вход коммутатора 5. Причем элементы матрицы МхМ, не вошедшие в область выбранной апертуры, не выбираются и дальнейшей обработке не подлежат.

При выборе последнего элемента выбранной апертуры медианного фильтра на первом выходе первого блока 9

памяти формируется логическая 1

til М

которая сообщает устройству о конце режима ранжирования. После обработки этого элемента устройство должно перейти в режим поиска медианы.

Если на управляющем входе первого блока 9 памяти присутствует логическая 1, выбор апертурных областей не осуществляется, на его первом и третьем входах при этом присутствуют

Q 5 0 5 0 д 5

5

0

е

постоянно логический О. Наличие логического О на третьем выходе первого блока 9 памяти, поступающего ил первый управляющш вход коммутатора 5, блокирует первые информационные входы коммутатора 5. При этом в первом блоке 9 памяти выбирается область, активизирующая работу его второго выхода. Наличие логической 1 на первом управляющем входе коммутатора 5 позволяет последнему пропускать на выход информацию, поступающую на его второй информационный вход/ т.е. содержимое первого счетчика 10. Считывание с первого и третьего выходов первого блока 9 памяти происходит в режиме ранжирования, а с второго выхода - в режиме поиска медианы.

Применение первого блока 9 памяти позволяет широко варьировать формой и величиной апертуры медианного фильтра путем его перепрограммирования .

Рассмотрим режим ранжирования.

В режиме ранжирования первый триггер 23 установлен в нулевое состояние. Логическая 1 инверсного выхода первого триггера 23 поступает на шестой выход блока 8 управления и далее на R-вход четвертого регистра 16, блокируя его работу по тактируемому С-ВХОДУ на все время режима ранжирования. Логический О с выхода четвертого регистра 16 поступает на первый вход блока 18 сравнения.

Таким образом, на выходе блока 18 сравнения на все время режима ранжирования устанавливается логический , О.

На R-вход установки нуля второго счетчика 15 поступает логический О с единичного выхода первого триггера 23 через второй элемент ИЛИ 25, т.е. работа второго счетчика 15 разрещена по входу предварит ельной записи С и по входу суммирования +1.

Кроме того, содержимое первого счетчика 10 в начале ранжирования равно нулю.

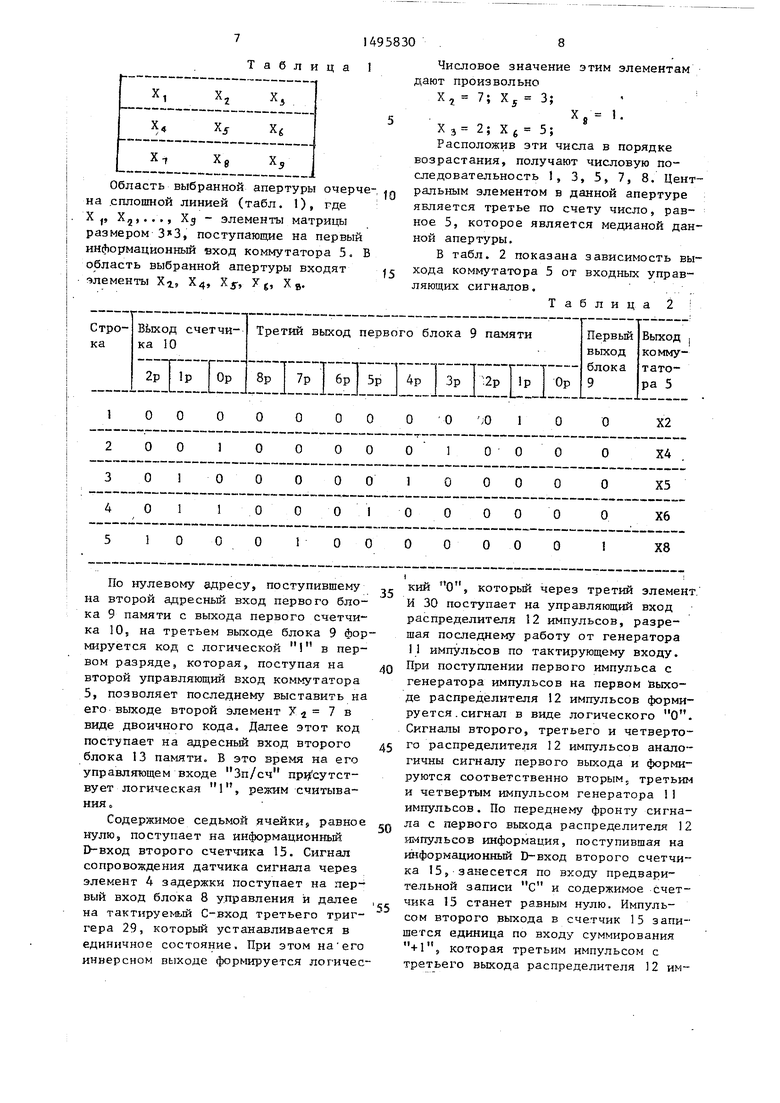

Дпя упрощения описания работы устройства рассмотрим матрицу размером З «3, приведенную в табл. 1.

При помощи первого регистра 6 (куда записан код выбранной апертуры) выбирают область в первом блоке 9 мяти, куда занесены адреса апертуры крестообразной формы.

Область выбранной апертуры очерчена .сплошной линией (табл. 1), где X J, Х,..., Х элементы матрицы размером поступающие на первый информационный вход коммутатора 5 , В область выбранной апертуры входят элементы Х, Х4 Хд-, X j, X g.

Числовое значение этим элементам дают произвольно

X- 7 V - 1

j- /,Aj- J)

х, t.

Хэ 2; Хб 5;

Расположив эти числа в порядке возрастания, получают числовую последовательность 1, 3, 5, 7, 8. Центральным элементом в данной апертуре является третье по счету число, равное 5, которое является медианой данной апертуры,

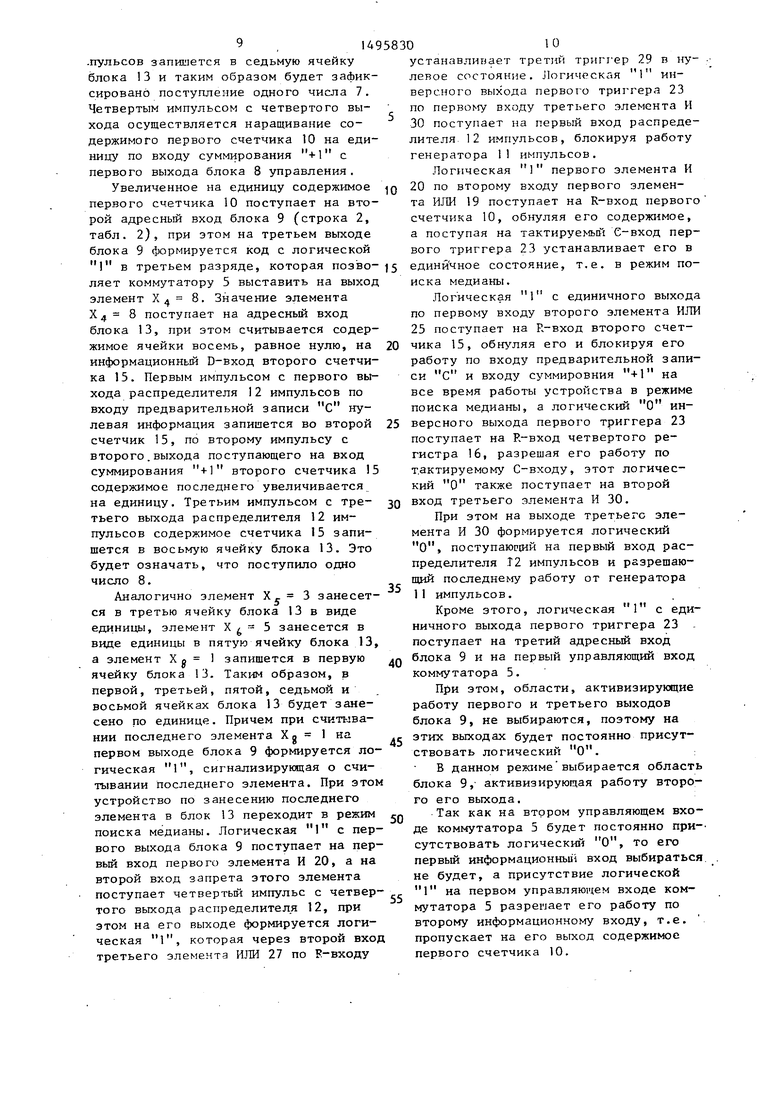

В табл. 2 показана зависимость выхода коммутатора 5 от входных управляющих сигналов. ..... Таблица 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для медианной фильтрации двумерных массивов | 1987 |

|

SU1524067A1 |

| Медианный фильтр | 1988 |

|

SU1562902A1 |

| Устройство для программного управления | 1990 |

|

SU1716482A1 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1987 |

|

SU1429148A2 |

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

| Устройство для сортировки информации | 1986 |

|

SU1365075A1 |

| Устройство для формирования признаков распознаваемых образов | 1986 |

|

SU1328830A1 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1987 |

|

SU1413656A1 |

| Устройство для определения текущей медианы | 1985 |

|

SU1322314A1 |

| ДИСКРЕТНАЯ МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1997 |

|

RU2110827C1 |

Изобретение относится к вычислительной технике и может быть использовано в системах распознавания изображений. Цель изобретения - в упрощение устройства. Это достигается введением элемента задержки 4, третьего регистра 7, первого блока памяти 9, первого счетчика 10, распределителя импульсов 12, второго блока памяти 13, сумматора 14, второго счетчика 15, четвертого регистра 16 и блока сравнения 18, что позволяет варьировать величину и форму апертуры. 2 ил.

По нулевому адресу, поступившему на второй адресный вход первого блока 9 памяти с выхода первого счетчика 10, на третьем выходе блока 9 формируется код с логической I в первом разряде, которая, поступая на второй управляющий вход коммутатора 5, позволяет последнему выставить на его выходе второй элемент У 7 в виде двоичного кода. Далее этот код поступает на адресный вход второго блока 13 памяти. В это время на его управляющем входе Зп/сч пр г сутст- вует логическая 1, режим считывания.

Содержимое седьмой ячейки равное нулю, поступает на информационный D-ВХОД второго счетчика 15. Сигнал сопровождения датчика сигнала через элемент 4 задержки поступает на первый вход блока 8 управления и далее на тактируемый С-вход третьего триггера 29, который устанавливается в единичное состояние. При этом на его инверсном выходе формируется логичес5

0

5

0

5

кий о, который череэ третий элемент. И 30 поступает на управляющий вход распределителя 12 импульсов, разрешая последнему работу от генератора 11 импульсов по тактирующему входу. При поступлении первого импульса с генератора импульсов на первом Выходе распределителя 12 импульсов формируется . сигнал в виде логического О. Сигналы второго, третьего и четвертого распределителя 12 импульсов аналогичны сигналу первого выхода и формируются соответственно вторым, третьим и четвертым импульсом генератора 11 импульсов. По переднему фронту сигнала с первого выхода распределителя 12 И1« пульсов информация, поступившая на информационный D-вход второго счетчика 15,занесется по входу предварительной записи с и содержимое счетчика 15 станет равным нулю. Импульсом второго выхода в счетчик 15 запишется единица по входу суммирования +1, которая третьим импульсом с третьего выхода распределителя 12 им.пульсов запишется в седьмую ячейку блока 13 и таким образом будет зафиксировано поступление одного числа 7. Четвертым импульсом с четвертого выхода осуществляется наращивание содержимого первого счетчика 10 на единицу по входу суммирования 1 с первого выхода блока 8 управления.

Увеличенное на единицу содержимое первого счетчика 10 поступает на второй адресный вход блока 9 (строка 2, табл. 2), при этом на третьем выходе блока 9 формируется код с логической 1 в третьем разряде, которая позво- ляет коммутатору 5 выставить на выход элемент Х 8. Значение элемента Х4 8 поступает на адресный вход блока 13, при этом считывается содержимое ячейки восемь, равное нулю, на информационный D-ВХОД второго счетчика 15. Первым импульсом с первого выхода распределителя 12 импульсов по входу предварительной записи С нулевая информация запишется во второй счетчик 15, по второму импульсу с второго.выхода поступающего на вход суммирования + второго счетчика 5 содержимое последнего увеличивается на единицу. Третьим импульсом с третьего выхода распределителя 12 импульсов содержимое счетчика 15 запишется в восьмую ячейку блока 13. Это будет означать, что поступило одно число 8.

Аналогично элемент Х 3 занесет

ся в третью ячейку блока 13 в виде единицы, элемент X 5 занесется в виде единицы в пятую ячейку блока 13, а элемент X g 1 запишется в первую ячейку блока 13. Таким образом, в первой, третьей, пятой, седьмой и восьмой ячейках блока 13 будет занесено по единице. Причем при считьлва- нии последнего элемента Xg 1 на первом выходе блока 9 формируется логическая 1, сигнализирующая о считывании последнего элемента. При этом устройство по занесению последнего элемента в блок 13 переходит в режим поиска медианы. Логическая 1 с первого выхода блока 9 поступает на пер- вьй вход первого элемента И 20, а на второй вход запрета этого элемента поступает четвертый импульс с четвертого выхода распределителя 12, при этом на его выходе формируется логическая 1, которая через второй вход третьего элемента ИЛИ 27 по Р-входу

устанавливает третий трип ер 29 в ну- левое состояние. Логическая 1 инверсного выхода первот-о триггера 23 по пepвo y входу третьего элемента И 30 поступает на первый вход распределителя 12 импульсов, блокируя работу генератора 11 импульсов.

Логическая 1 первого элемента И 20 по второму входу первого элемента ШШ 19 поступает на R-вход первого счетчика 10, обнуляя его содержимое, а поступая на тактируемый С-вход первого триггера 23 устанавливает его в единй чное состояние, т.е. в режим поиска медианы.

Логическая I с единичного выхода по первому входу второго элемента ИЛИ 25 поступает на R-вход второго счетчика 15, его и блокируя его работу по входу предварительной записи с и входу суммировния +1 на

все время работы устройства в режиме поиска медианы, а логический О ин- версного выхода первого триггера 23 поступает на R-вход четвертого регистра 16, разрешая его работу по тактируемому С-входу, этот логический О также поступает на второй вход третьего элемента И 30.

При этом на выходе третьего элемента И 30 формируется логический О, поступающий на первьй вход распределителя Т2 импульсов и разрешающий последнему работу от генератора 11 импульсов.

Кроме этого, логическая 1 с единичного выхода первого триггера 23 поступает на третий адресный вход блока 9 и на первый управляющий вход коммутатора 5.

При этом, области, активизирующие работу первого и третьего выходов блока 9, не выбираются, поэтому на этих выходах будет постоянно присутствовать логический О.:

В данном режиме выбирается область блока 9, активизирующая работу второго его выхода.

Так как на втором управляющем входе коммутатора 5 будет постоянно при-- сутствовать логический О, то его первый информационны11 вход выбираться. не будет, а присутствие логической 1 на первом управляю1чем входе коммутатора 5 разрешает его работу по второму информационному входу, т.е. пропускает на его выход содержимое первого счетчика 10.

n

Как было отмечено, центральным элементом в данной апертуре является третье по счету число, равное 5, т.е медиана данной апертуры равна 5.

Нулевая информация с выхода первого счетчика 10 через второй информационный вход коммутатора 5 поступает на адресный вход блока 13. Так как на управляющем входе Зп/сч присутству- ет логическая 1 в этот момент, поступающая с третьего выхода распределителя 12 импульсов, то осуществляется считывания нулевой ячейки блока 13 (равно нулю).

С выхода блока 13 информация пот/г ступает на второй вход сумматора 14 (на первом нулевая информация, поступающая с выхода четвертого регистра 16), а так как на обоих входах присутствует нулевая информация, то на информационный D-вход четвертого ре- ;гистра 16 поступит также нулевая ин- формация, которая по переднему фронту iпервого импульса с первого выхода iраспределителя 12 импульсов занесет- ; ся по тактирующему С-вкоду. По третьему импульсу с третьего выхода рас- пределителя 12 импульсов в блок 13 по

нулевому адресу запишется нулевая ин- зо ния на D-вход четвертого регистра 16

;4)Ормация с выхода четвертого счетчи: ка 16 (на время режима поиска медианы на выходе второго счетчика 15 постоянно присутствует логический О),

;а четвертым импульсом с четвертого выхода через блок 8 управления осуществляется наращивание содержимого первого счетчика 0 на единицу по входу суммирования +1. Таким образом, в первом счетчике 10 записан двоичный код, равный 001, который, поступив на адресные входы блока 13, считает содержимое первой ячейки, равное единице.

35

40

поступит число два, которое занесется в регистр 16 передним фронтом первого импульса с первого выхода распределителя 12 импульсов. Третьим импульсом с третьего выхода в третью ячейку блока 13 занесется нулевая информация, обнуляя третью ячейку. Четвертым импульсом с четвертого выхода содержимое первого счетчика 10 увеличится еще на единицу (код станет равным 100 4). В четвертой ячейке блока 13 присутствует нулевая информация, поэтому содержимое четвертого регистра 16 не изменится и останется равным двум. Третьим импульсом в четвертую ячейку блока 13 запищется нулевая информация (обнуление ячеек осуществляется последовательно не зависимо от того, записана в ней информация или нет).

Так как на первом входе сумматора 14 присутствует информация, равная нулю, то через второй вход сумматора 14 на D-вход четвертого регистра 16 поступит единица первой ячейки блока 13, которая передним фронтом первого импульса с первого выхода распределителя 12 импульсов занесется в четвертый регистр 16. Третьим импульсом с

45

50

поступит число два, которое занесется в регистр 16 передним фронтом первого импульса с первого выхода распределителя 12 импульсов. Третьим импульсом с третьего выхода в третью ячейку блока 13 занесется нулевая информация, обнуляя третью ячейку. Четвертым импульсом с четвертого выхода содержимое первого счетчика 10 увеличится еще на единицу (код станет равным 100 4). В четвертой ячейке блока 13 присутствует нулевая информация, поэтому содержимое четвертого регистра 16 не изменится и останется равным двум. Третьим импульсом в четвертую ячейку блока 13 запищется нулевая информация (обнуление ячеек осуществляется последовательно не зависимо от того, записана в ней информация или нет).

Четвертым импульсом с четвертого выхода распределителя 12 импульсов наращивается содержимое первого счетчика 10 (код станет равным 101 5).

третьего выхода распределителя 12 им-гс В пятой ячейке блока 13 записана еди-. пульсов в первую ячейку по пришедше- ница, которая при считывании посту- му адресу ( 1) запишется нулевая ™т на второй вход сумматора 14, на информация, т.е. произошло обнуление первом входе которого присутствует первой ячейки блока 13.число два. В результате суммирования

я е.

149583012

Четвертым импульсом с четвертого выхода распределителя 12 импульсов осуществляется наращивание первого

счетчика 10 на единицу (код станет

равным 010 2), но во второй ячейке блока 13 информация равна нулю, поэтому на второй вход сумматора 14 поступит нуль, а на первый - единица и в четвертый регистр 16 запищется снова единица, т.е. содержимое четвертого регистра 16 не изменится. По третьему импульсу с третьего выхода распределителя 12 импульсов по поступив- шему адресу (010 2) запишется нулевая информация, установленная на D- входе блока 13 с выхода второго счетчика 15.

Четвертым импульсом с четвертого выхода распределителя 12 импульсов увеличится содержимое первого счетчика 10 на единицу (код станет равным 011 3). При поступлении этого кода на адресный вход блока 13 содержимое третьей ячейки считается равным единице, которая поступит на второй вход сумматора 14, а на первом уже присутствует единица с выхода четвертого регистра 16. В результате суммирова

5

0

5

0

поступит число два, которое занесется в регистр 16 передним фронтом первого импульса с первого выхода распределителя 12 импульсов. Третьим импульсом с третьего выхода в третью ячейку блока 13 занесется нулевая информация, обнуляя третью ячейку. Четвертым импульсом с четвертого выхода содержимое первого счетчика 10 увеличится еще на единицу (код станет равным 100 4). В четвертой ячейке блока 13 присутствует нулевая информация, поэтому содержимое четвертого регистра 16 не изменится и останется равным двум. Третьим импульсом в четвертую ячейку блока 13 запищется нулевая информация (обнуление ячеек осуществляется последовательно не зависимо от того, записана в ней информация или нет).

Четвертым импульсом с четвертого выхода распределителя 12 импульсов наращивается содержимое первого счетчика 10 (код станет равным 101 5).

на D-ВХОД четвертого регистра 16 поступит число три, которое по передне ,му фронту первого импульса занесется в четвертый регистр 16, а так как ,во второй регистр 17 занесено зара- :Нее число три, которое поступает на второй вход блока 18 сравнения, TJD н выходе блока 18 сравнения формируется логическая 1, которая с выхода блока 18 сравнения по первом - информационному входу блока 8 управления поступает на второй вход четвертого элемента И 28, ас его седьмого выхода сигнал Лог. поступает на вход предварительной записи С третьего регистра 7 и заносит в регистр 7 передним фронтом содержимое первого счетчика 10, равное числу 5. Далее логический О поступает на второй выход устройства,

Таким образом, на первый выход устройства поступит значение медианы выбранной апертуры, равное 5. На это режим поиска медианы не заканчивается, он продолжается до тех пор, пока содержимое первого счетчика 10 не станет равным коду (Р. + 1), тде Р. - глубина памяти 13 блока. Это необходимо для того, чтобы по каждому последовательному коду первого счетчика 10 записать нулевую информацию в соответствующую ячейку блока 13. При достижении содержимого первого счетчика 10 кода,раБного (Р. + 1), на втором выходе блока 9 формируется логическая 1 (а в остальных случаях присутствует логический О), которая поступает на третий информационный вход блока 8 управления и далее на первьй вход второго ,элемента И 26 Ввиду того, что на втором входе этого элемента присутствует также логи- ческая 1 с единичного выхода третьего триггера 23, то на ее выходе формируется логическая 1, которая через первый вход первого элемента ИЛИ 19 поступает на R-вход первого счетчика 10, обнуляя последний, и через первый элемент HF, 21 на Р.-вход первого триггера 23, устанавливая последний в нулевое состояние, т.е в режим ранжирования. При этом логическая 1 с инверсного выхода первого триггера 23 поступает на второй вход третьего элемента И 30, на первда вход которой постуггает таюке логическая 1 с ннвйрсиого выхода третьего триггера 29. 1о этому на выходе третьего элемента И 30 установится логическая 1, которая поступит ия , первый вход распределителя 12 импулт - сов и -запретит его работу от генератора 1 импульсов до прихода следующего тактирующего сш нала. Далее процесс работы устройства циклически повторяется.

Логическая 1 на выходе блоха 18 сравнения Появляется в двух случаях: если содержимое четвертого регистра 16 равно содержимому второго ра 17 и если содержимое регистра 16

больше содержимого регистра 17.

Необходимость формирования логической 1 ка выходе блока 18 сравнения при равенстве содержимого четвертого регистру 16 и содержимого второго регистра 17 рассмотрено выие, а необходимость формирования логической I на выходе блока 18 сравнения рассматривают на втором примере.

Выбирают апертуру крестообразной

формы, рассмотренн то в первом примере и те же элементы из табл. 1, а именно Х, Х., Х, Х и Xg.

Дают числовое значение элементам;

Х 0; Х 3; 5 0;

X, 0; Х 0.

Расположив эти числа в порядке возрастания, получают числовую последовательность О, О, О, О, 3. Центральным элементом в данной апертуре является третье по счету число, равное О, т.е. медиана данной апертуры равна О.

В режиме ранжирования в нулевую ячейку блока 13 в этом случае запишется число четыре, равное количество нулей, а в третью ячейку блока 13 запишется единица, так как тройка

только одна. В режиме поиска медианы по нулевому адресу первого счетчика 10, поступившему на адресные входы блока 13, считывается из нулевой ячейки число четыре в четвертый регистр 16, а во втором регистре 17 по-прежнему занесено число три. Содержимое регистра 16 больше содержимого регистра 17, на выходе блока 18 . сравнения формируется логическая 1,

которая во второй регистр 17 запишет содержимое первого счетчика 10, т.е. нулевую информацию. Таким образом выставится на выход Выход 1 устройства величина медианы, равная нулю, что

соответствует примеру.

15

указанному числовому

Формула изобретения

Устройство для обработки изображений объектов, содержащее датчик сигналов, информационньй выход которого соединен с входом аналого-цифрового преобразователя, выход которого соединен с входом формирователя апертуры, первый и второй регистры, коммутатор, генератор импульсов и блок управления , отличающееся тем, что, с целью упрощения устройства, оно содержит первый и второй блоки памятиS блок сравнения, первый и второй счетчики, элемент задержки, распределитель импульсов, сумматор.и третий и четвертый регистры, Выход синхронизации датчика сигналов соединен с тактирующим входом формирователя апертуры и с входом элемента задержки, выход которого соединен с синхронизирующим входом блока управления, выход.формирователя апертуры соединен с первым информационным входом коммутатора, второй информационный вход которого соединен с выходом первого счетчика, суммирующий вход которого соединен с первым выходом блока управления, а вход Сброс первого счетчика соединен с четвертым выходом блока управления, вход , первого регистра является первым информационным входом устройства, а выход соединен с первым адресным входом первого блока памяти, второй адресный вход которого соединен с выходом первого счетчика, информацион- ный вход второго регистра является вторым информационным входом устройства, а выход второго регистра соединен с первым входом блока сравне- ния, второй вход которого соединен с выходом четвертого регистра, а выход с первым информационным входом блока управления, вход Сброс блока управления является управляющим входом устройства, информационный вход третьего регистра соединен с выходом

10

15

20

25

. - 50

9583016

первого счетчика, стробирующий вход третьего регистра соединен с седьмым выходом блока управления, вход Сброс третьего регистра соединен с управляющим входом устройства, выход третьего регистра является первым выходом устройства, первый вьгход первого блока памяти соединен с вторым информационным входом блока управления, второй выход первого блока памяти соединен с третьим информационным входом блока управления, первый вьгход распределителя импульсов соединен со стробирующим входом четвертого регистра, второй выход распределителя импульсов соединен с суммирующим входом второго счетчика, третий выход распределителя импульсов соединен с управляющим входом второго блока памяти, четвертый выход распределителя И1чпульсов соединен с четвертым информационньй входом блока управления, тактирующий вход распределителя импульсов соединен с выходом генератора импульсов, а управляющий вход соединен с пятым выходом блока управления, информационный вход четвертого регистра соединен с выходом сумматора, первый вход которого соединен с выходом четвертого регистра, .выход второго блока памяти соединен с вторым входом сумматора и с установочным входом второго счетчика, вход Сброс которого соединен с третьим выходом блока управления, выход коммутатора соединен с адресным входом второго блока памяти, информационный вход которого соединен с выходом второго счетчика, тактирующий вход которого соединен с первым выходом распределителя импульсов, вход Сброс четвертого регистра соединен с шестым выходом блока управления, седьмой выход блока управления является вторым выходом устройства, первый управляющий вход коммутатора и управляющий вход первого блока памяти соединены с вторым вьгходом блока управления, второй управляющий вход коммутатора соединен с третьим выходом первого блока памяти.

30

35

40

45

фи2.2

| Зарубежная радиоэлектроника, 1986, К 6, с | |||

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

| Устройство для обработки изображений объектов | 1984 |

|

SU1226500A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-07-23—Публикация

1987-11-20—Подача