Изобретение относится к вычислительной технике и может быть использовано для селекции информационных каналов в многоканальных системах сбора, регистрации и обработки информации.

Цель изобретения - повышение быстродействия устройства.

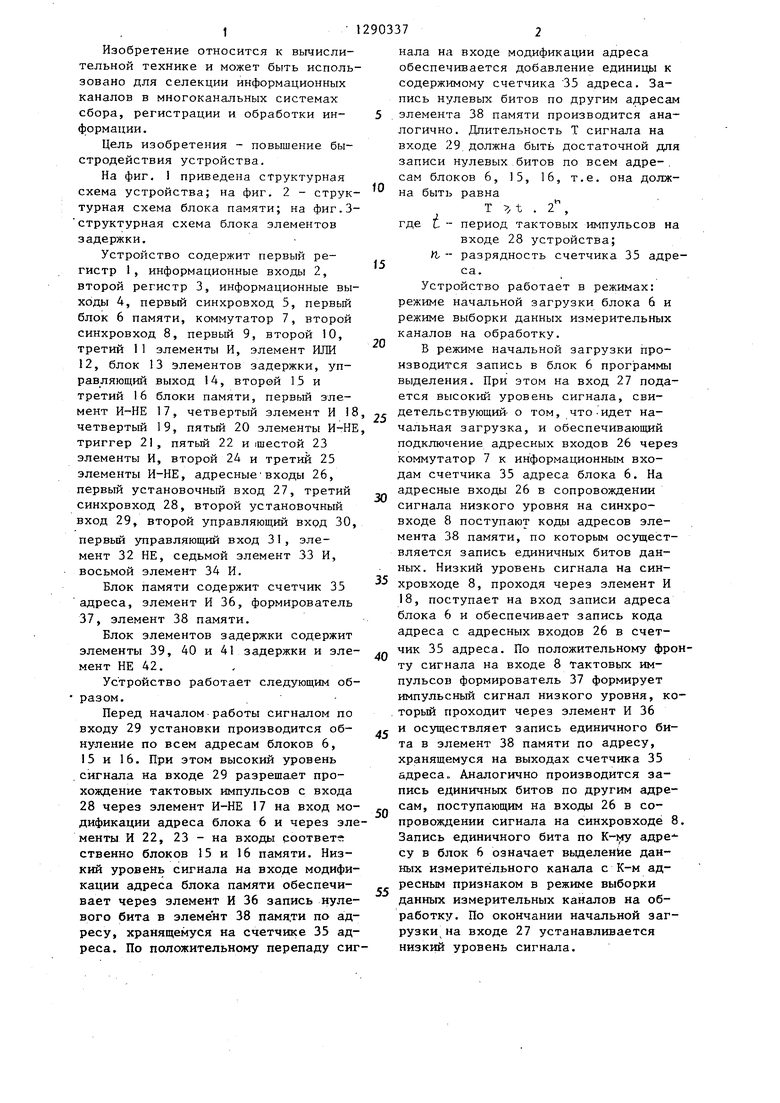

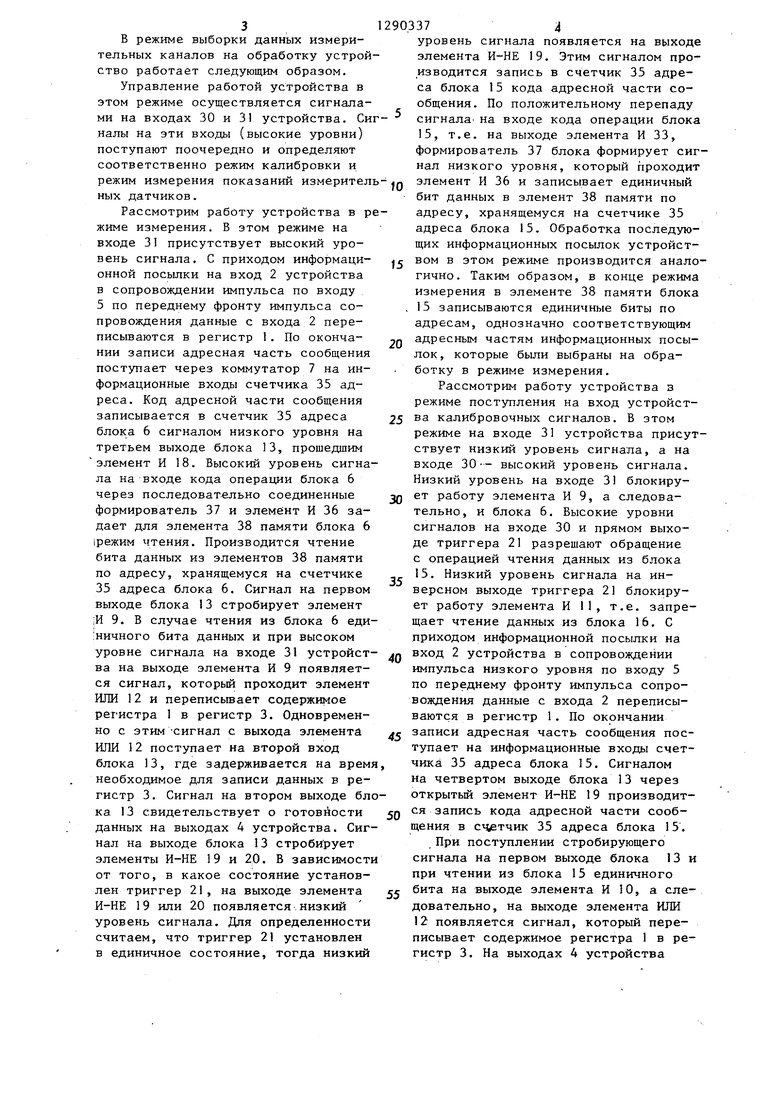

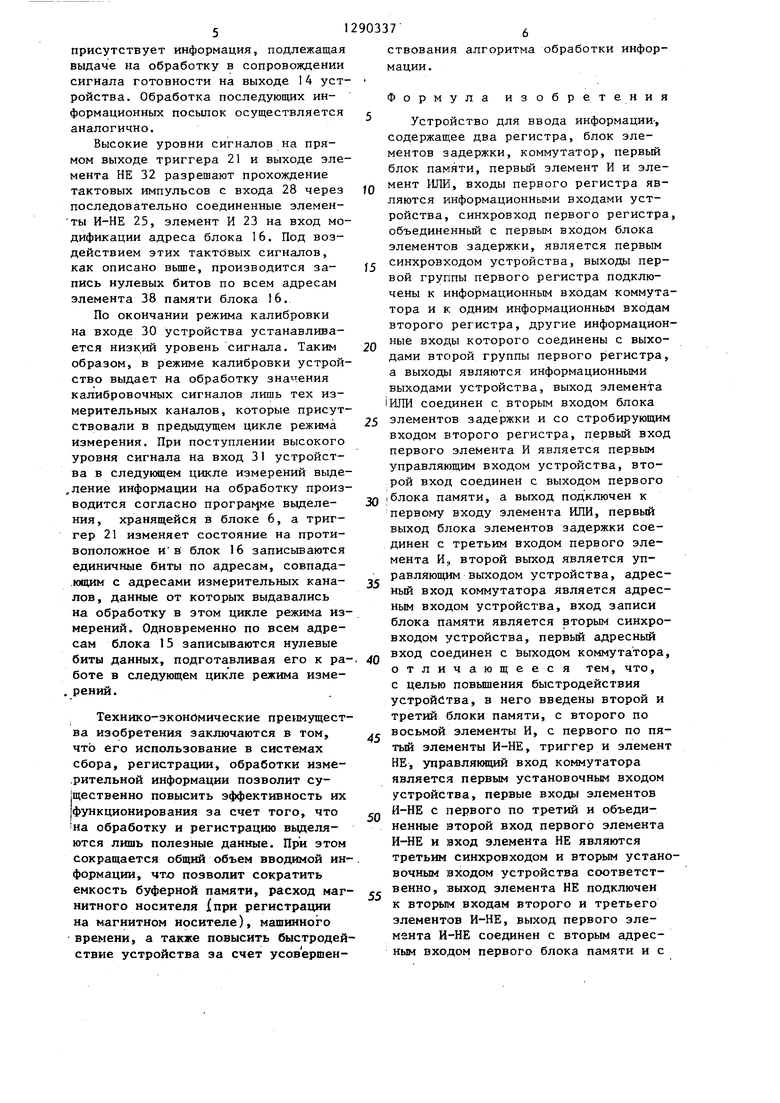

На фиг, 1 приведена структурная схема устройства; на фиг. 2 - структурная схема блока памяти; на фиг.З- структурная схема блока элементов задержки.

Устройство содержит первый регистр 1, информационные входы 2, второй регистр 3, информационные выходы 4, первый синхровход 5, первый блок 6 памяти, коммутатор 7, второй синхровход 8, первый 9, второй 10, третий 11 элементы И, элемент ИЛИ 12, блок 13 элементов задержки, управляющий выход 14, второй 15 и третий 16 блоки памяти, первый элемент И-НЕ 17, четвертый элемент И 18 четвертый 19, пятый 20 элементы И-НЕ триггер 21, пятый 22 и шестой 23 элементы И, второй 24 и третий 25 элементы И-НЕ, адресные входы 26, первый установочный вход 27, третий синхровход 28, второй установочный вход 29, второй управляющий вход 30, первый управляющий вход 31, элемент 32 НЕ, седьмой элемент 33 И, восьмой элемент 34 И.

Блок памяти содержит счетчик 35 адреса, элемент И 36, формирователь 37, элемент 38 памяти.

Блок элементов задержки содержит элементы 39, 40 и 41 задержки и элемент НЕ 42.

Устройство работает следующим об- разом.

Перед началом работы сигналом по входу 29 установки производится обнуление по всем адресам блоков 6, 15 и 16. При этом высокий уровень . сигнала на входе 29 разрешает прохождение тактовых импульсов с входа 28 через элемент И-НЕ 17 на вход модификации адреса блока 6 и через элементы И 22, 23 - на входы соответ ственно блоков 15 и 16 памяти. Низкий уровень сигнала на входе модификации адреса блока памяти обеспечивает через элемент И 36 запись нулевого бита в элемент 38 памя.ти по адресу, хранящемуся на счетчике 35 адреса. По положительному перепаду сиг

5

0

5

0

5

0

5

0

где

5

tнала на входе модификации адреса обеспечивается добавление единицы к содержимому счетчика 35 адреса. Запись нулевых битов по другим адресам элемента 38 памяти производится аналогично. Длительность Т сигнала на входе 29 должна быть достаточной для записи нулевых битов по всем адре-. сам блоков 6, 15, 16, т.е. она должна быть равна

Т .t . 2,

период тактовых импульсов на входе 28 устройства; И - разрядность счетчика 35 адреса.

Устройство работает в режимах: режиме начальной загрузки блока 6 и режиме выборки данных измерительных каналов на обработку.

В режиме начальной загрузки производится запись в блок 6 программы выделения. При этом на вход 27 подается высокий уровень сигнала, свидетельствующий- о том, что-идет начальная загрузка, и обеспечивающий подключение адресных входов 26 через коммутатор 7 к информационным входам счетчика 35 адреса блока 6. На адресные входы 26 в сопровождении сигнала низкого уровня на синхро- входе В поступают коды адресов элемента 38 памяти, по которым осуществляется запись единичных битов данных. Низкий уровень сигнала на син- хровходе 8, проходя через элемент И 18, поступает на вход записи адреса блока 6 и обеспечивает запись кода адреса с адресных входов 26 в счетчик 35 адреса. По положительному фронту сигнала на входе 8 тактовых импульсов формирователь 37 формирует импульсный сигнал низкого уровня, который проходит через элемент И 36 и осуществляет запись единичного бита в элемент 38 памяти по адресу, хранящемуся иа выходах счетчика 35 адреса,, Аналогично производится запись единичных битов по другим адресам, поступающим на входы 26 в сопровождении сигнала на синхровходе 8. Запись единичного бита по К-му адре- су в блок 6 означает вьщеленйе данных измерительного канала с К-м адресным признаком в режиме выборки данных измерительных каналов на обработку. По окончании начальной загрузки на входе 27 устанавливается низкий уровень сигнала.

3

в режиме выборки данных измерительных каналов на обработку устройство работает следующим образом.

Управление работой устройства в этом режиме осуществляется сигналами на входах 30 и 31 устройства. Си налы на эти входы (высокие уровни) поступают поочередно и определяют соответственно режим калибровки и режим измерения показаний измерител ных датчиков.

Рассмотрим работу устройства в р жиме измерения. В этом режиме на входе 31 присутствует высокий уровень сигнала. С приходом информационной посылки на вход 2 устройства в сопровождении импульса по входу 5 по переднему фронту импульса сопровождения данные с входа 2 переписываются в регистр 1. По окончании записи адресная часть сообщения поступает через коммутатор 7 на информационные входы счетчика 35 адреса. Код адресной части сообщения записывается в счетчик 35 адреса блока 6 сигналом низкого уровня на третьем выходе блока 13, прошедшим элемент И 18. Высокий уровень сигнала на входе кода операции блока 6 через последовательно соединенные формирователь 37 и элемент И 36 задает для элемента 38 памяти блока 6 1режим чтения. Производится чтение бита данных из элементов 38 памяти по адресу, хранящемуся на счетчике 35 адреса блока 6. Сигнал на первом выходе блока 13 стробирует элемент |И 9. В случае чтения из блока 6 еди ;ничного бита данных и при высоком уровне сигнала на входе 31 устройства на выходе элемента И 9 появляется сигнал, который проходит элемент ИЛИ 12 и переписьгоает содержимое регистра 1 в регистр 3. Одновременно с этим-сигнал с выхода элемента ИЛИ 12 поступает на второй вход блока 13, где задерживается на врем необходимое для записи данных в регистр 3. Сигнал на втором выходе бл ка 13 свидетельствует о готовйости данных на выходах 4 устройства. Сигнал на выходе блока 13 строби рует элементы И-НЕ 19 и 20. В зависимост от того, в какое состояние установлен триггер 21, на выходе элемента И-НЕ 19 или 20 появляется низкий уровень сигнала. Для определенности считаем, что триггер 21 установлен в единичное состояние, тогда низкий

903374

уровень сигнала появляется на выходе элемента И-НЕ 19. Этим сигналом производится запись в счетчик 33 адреса блока 15 кода адресной части сообщения. По положительному перепаду сигнала на входе кода операции блока 15, т.е. на выходе элемента И 33, формирователь 37 блока формирует сигнал низкого уровня, который проходит

5

0

элемент И 36 и записывает единичный

бит данных в элемент 38 памяти по адресу, хранящемуся на счетчике 35 адреса блока 15. Обработка последующих информационных посылок устройст1 вом в этом режиме производится аналогично. Таким образом, в конце режима измерения в элементе 38 памяти блока , 15 записываются единичные биты по адресам, однозначно соответствующим

Q адресным частям информационных посылок , которые были выбраны на обработку в режиме измерения.

Рассмотрим работу устройства з режиме поступления на вход устройст25 ва калибровочных сигналов. В этом

режиме на входе 31 устройства присутствует низкий уровень сигнала, а на входе 30-- высокий уровень сигнала. Низкий уровень на входе 31 блокируJQ ет работу элемента И 9, а следовательно, и блока 6. Высокие уровни сигналов на входе 30 и прямом выходе триггера 21 разрешают обращение с операцией чтения данных из блока 15, Низкий уровень сигнала на инверсном выходе триггера 21 блокирует работу элемента И 11, т.е. запрещает чтение данных из блока 16. С приходом информационной посылки на

0 вход 2 устройства в сопровождении импульса низкого уровня по входу 5 по переднему фронту импульса сопровождения данные с входа 2 переписываются в регистр 1. По окончании

е записи адресная часть сообщения поступает на информационные входы счет- чика 35 адреса блока 15. Сигналом на четвертом выходе блока 13 через открытьм элемент И-НЕ 19 производитCQ ся запись кода адресной части сообщения в счетчик 35 адреса блока 15.

При поступлении стробирующего сигнала на первом выходе блока 13 и при чтении из блока 15 единичного

ГС бита на выходе элемента И 10, а следовательно, на выходе элемента ИЛИ 12 появляется сигнал, который переписывает содержимое регистра 1 в регистр 3. На выходах 4 устройства

35

to

15

20

25

51290337

присутствует информация, подлежащая ыдаче на обработку в сопровождении сигнала готовности на выходе 14 устройства. Обработка последующих инормационных посылок осуществляется аналогично.

Высокие уровни сигналов на пряом выходе триггера 21 и выходе элеента НЕ 32 разрешают прохождение тактовых импульсов с входа 28 через оследовательно соединенные элемены И-НЕ 25, элемент И 23 на вход моификации адреса блока 16. Под возействием этих тактовых сигналов, ак описано вьше, производится заись нулевых битов по всем адресам элемента 38 памяти блока 16.

По окончании режима калибровки на входе 30 устройства устанавливается низк,ий уровень сигнала. Таким образом, в режиме калибровки устройство выдает на обработку значения калибровочных сигналов лишь тех изерительных каналов, которые присутствовали в предыдущем цикле режима измерения. При поступлении высокого уровня сигнала на вход 31 устройста в следующем цикле измерений выдеение информации на обработку производится согласно програь}ме выделения, хранящейся в блоке 6, а триггер 21 изменяет состояние на противоположное и в блок 16 записьгоаются единичные биты по адресам, совпада- lonuiMf с адресами измерительных канаов, данные от которых выдавались на обработку в этом цикле режима изерений. Одновременно по всем адресам блока 15 записываются нулевые биты данных, подготавливая его к ра-. боте в следующем цикле режима измерений.

Технико-экономические преимущества изобретения заключаются в том, что его использование в системах сбора, регистрации, обработки изме- рительной информации позволит суественно повысить эффективность их ункционирования за счет того, что на обработку и регистрацию вьщеля- тся лишь полезные данные. При этом сокращается общий объем вводимой инормации, что позволит сократить емкость буферной памяти, расход магнитного носителя {при регистрации на магнитном носителе), машинного времени, а также повысить быстродействие устройства за счет усовершен30

35

40

45

50

55

ств мац

Фо

сод мен бло мен ляю рой объ эле син вой чен тор вто ные дам а в вых 1ИЛИ эле вхо пер упр рой бло пер вых дин мен рав ный ным бло вхо вхо от с ц уст тре вос тый НЕ явл уст И-Н нен И-Н тре воч вен к в эле мен ным

5

0

5

0

5

0

5

0

5

ствования алгоритма обработки информации.

Формула изобретения

Устройство для ввода информации-, содержащее два регистра, блок элементов задержки, коммутатор, первый блок памяти, первый элемент И и элемент ИЛК, входы первого регистра являются информационными входами устройства, синхровход первого регистра, объединенный с первым входом блока элементов задержки, является первым синхровходом устройства, выходы первой группы первого регистра подключены к информационным входам коммутатора и к одним информационным входам второго регистра, другие информационные входы которого соединены с выходами второй группы первого регистра, а выходы являются информационными выходами устройства, выход элемента 1ИЛИ соединен с вторым входом блока элементов задержки и со стробирующим входом второго регистра, первый вход первого элемента И является первым управляющим входом устройства, второй вход соединен с выходом первого блока памяти, а выход подключен к первому входу элемента ИЛИ, первый выход блока элементов задержки соединен с третьим входом первого элемента И,, второй выход является управляющим выходом устройства, адресный вход коммутатора является адресным входом устройства, вход записи блока памяти является вторым синхровходом устройства, первый адресный вход соединен с йыходом коммутатора, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены второй и третий блоки памяти, с второго по восьмой элементы И, с первого по пятый элементы И-НЕ, триггер и элемент НЕ, управлякщий вход коммутатора является первым установочным входом устройства, первые входы элементов И-НЕ с первого по третий и объединенные второй вход первого элемента И-НЕ и вход элемента НЕ являются третьим синхровходом и вторым установочным входом устройства соответственно, выход элемента НЕ подключен к вторьпч входам второго и третьего элементов И-НЕ, выход первого элемента И-НЕ соединен с вторым адресным входом первого блока памяти и с

7

первыми входами пятого и шестого эле ментов И, вторые входы которых подключены к выходам второго и третьего элементов И-НЕ соответственно, выходы первой группы первого регистра подключены к первым адресным входам второго и третьего блоков памяти, вторые адресные входы которых подключены к выходам пятого и шестого элементов И cooToeTcfBeHHo, третий и четвертый выходы блока элементов задержки соединены с первым входом четвертого элемента И и с объединенными первыми входами четвертого и пятого элементов И-НЕ соответственно, второй вход четвертого элемента И является вторым синхровходом устройства, неинвертирующий выход триггера соединен с первыми входами второго и седьмого элементов И, с вторым входом четвертого элемента И-НЕ и третьим входом третьего элемента И-НЕ, инвертируюп1ий выход триггера соединен с третьим входом второго

10

903378

элемента И-НЕ, с вторым входом пятого элемента И-НЕ и с первьми входами третьего и восьмого элементов И, вы- ходы четвертого элемента И, четвер- 5 того и пятого элементов И-НЕ соединены с третьими адресными входами блоков памяти с первого по третий соответственно, выход первого элемент И подключен к вторым входам седьмого и восьмого элементов И, выходы которых соединены с входами записи второго и третьего блоков памяти соответственно, выходы которых подключены к вторым входам второго и третьего элементов И, третьи входы которых подключены к первому выходу блока элементов задержки, четвертые входы - являются вторым управляющим входом устройства, а выходы соединены с вторым и третьим входами элемента ИЛИ , установочный вход триггера является первым уп - равляющим входом устройст - ва.

5

20

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1986 |

|

SU1363225A2 |

| Многоканальное устройство ввода информации | 1985 |

|

SU1273936A2 |

| Устройство для ввода информации | 1985 |

|

SU1317446A1 |

| Устройство для ввода информации | 1987 |

|

SU1472912A1 |

| Устройство для сортировки информации | 1986 |

|

SU1606972A1 |

| Многоканальное устройство ввода информации | 1984 |

|

SU1196882A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1261010A1 |

| Устройство для ввода информации | 1987 |

|

SU1442999A2 |

| Устройство для сопряжения | 1985 |

|

SU1278861A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1361632A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве устройства для селекцю информационных каналов в многоканальных системах сбора, регистрации и обработки информации. Целью изобретения является повьше- ние быстродействия устройства. Цель изобретения достигается введением в устройство блоков памяти 15, 16, элементов И 10, 11, 18, 22, 23, 33, 34, элементов И-НЕ 17, 19, 20, 24, 25. Использование устройства в системах сбора, регистрации, обработки измерительной информации позволит существенно повысить эффективность их функционирования за счет того, что на обработку и регистрацию выделяются лишь полезные данные, что приводит к сокращению общего объема вводимой информации. 3 шт. jf 5 г (Л с N9 ;о о 00 00

Pu.tZ

Редактор И. Рыбченко

Составитель И. Алексеев Техред Л. Сердюков а

Заказ 7904/48

Тираж 673

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор М. Пожо

Подписное

| Устройство для селекции информационных каналов | 1982 |

|

SU1070538A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальное устройство ввода информации | 1984 |

|

SU1196882A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1987-02-15—Публикация

1985-04-26—Подача