J2b

CD CD GO

СД

31499

Изобретение относится к автоматике и вычислительной технике и может быть использовано при реализации средств контроля и диагностики отка- зов логических узлов„

Целью изобретения является расширение функциональных возможностей устройства путем обеспечения возможности регистрации степени активиза- ции исследуемой логической схемы,,

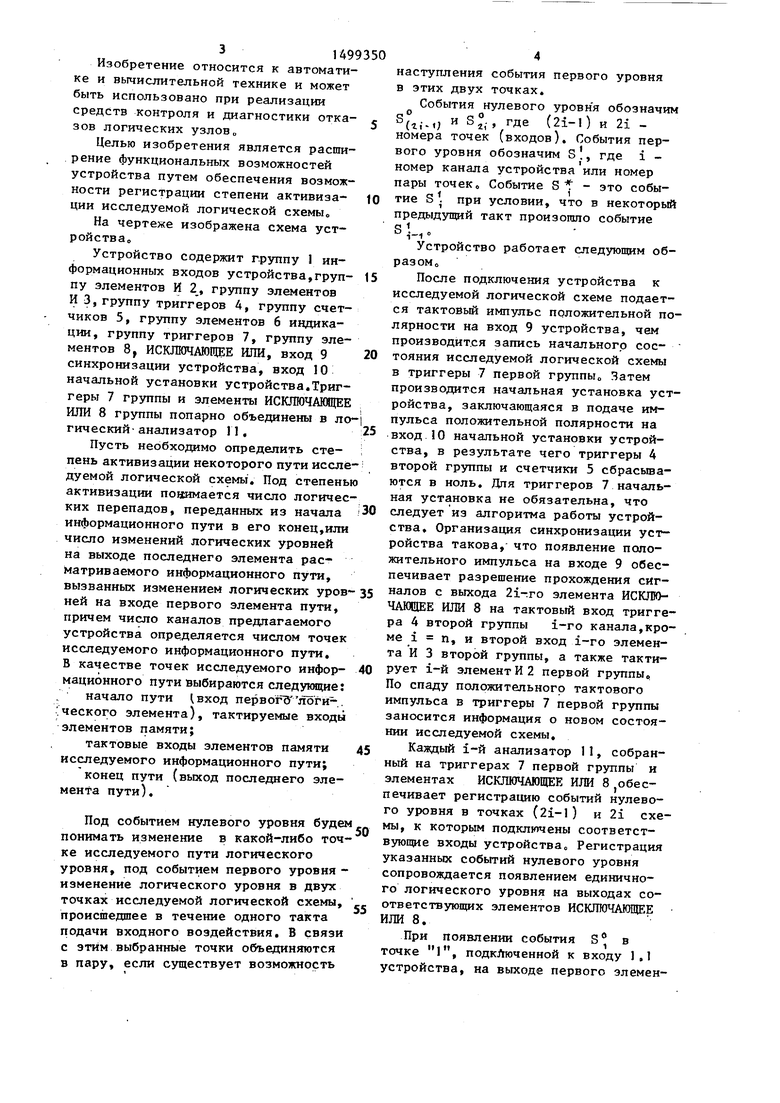

На чертеже изображена схема уст- ройствао

Устройство содержит группу 1 информационных входов устройства,груп- пу элементов И 2, группу элементов И 3, группу триггеров 4, группу счетчиков 5, группу элементов 6 индикации, группу триггеров 7, группу элементов 8, ИСКЛЮЧАЮЩЕЕ ШШ, вход 9 синхронизации устройства, вход 10 начальной установки устройства,Триггеры 7 группы и элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 8 группы попарно объединены в ло гический-анализатор 11,

Пусть необходимо определить ста- пень активизации некоторого пути исследуемой логической схемы. Под степень активизации понимается число логических перепадов, переданных из начала информационного пути в его конец,или число изменений логических уровней на выходе последнего элемента рас- матриваемого информационного пути, вызванных изменением логических уров ней на входе первого элемента пути, причем число каналов предлагаемого устройства определяется числом точек исследуемого информационного пути, В качестве точек исследуемого инфор- мационного пути выбираются следующие:

начало пути вход перво г5 логи-.. .ческого элемента), тактируемые входы элементов памяти;

тактовые входы элементов памяти исследуемого информационного пути;

конец пути (выход последнего элемента пути).

Под событием нулевого уровня будем

понимать изменение в какой-либо точке исследуемого пути логического уровня, под событием первого уровня - изменение логического уровия в двух точках исследуемой логической схемы, происшедшее в течение одного такта подачи входного воздействия, В связи с этим выбранные точки объединяются в пару, если сзпцествует возможность

0 5

0 5 0

5

0

наступления события первого уровня в этих двух точках.

События нулевого уровня обозначим

S.-O S°,-/« (21-1) и 2i - номера точек (входов). События первого уровня обозначим S I, где i - номер канала устройства или номер пары точек. Событие S - это событие S . при условии, что в некоторый предыдущий такт произогало событие

о 1

Ь ,. о

Устройство работает следующим об- разоМо

После подключения устройства к исследуемой логической схеме подается тактовый импульс положительной полярности на вход 9 устройства, чем производится запись начального состояния исследуемой логической схемы в триггеры 7 первой группы Затем производится начальная установка устройства, заключающаяся в подаче импульса положительной полярности на вход 10 начальной установки устройства, в результате чего триггеры 4 второй группы и счетчики 5 сбрасьша- ются в ноль, Дпя триггеров 7 начальная установка не обязательна, что следует из алгоритма работы устройства. Организация синхронизации устройства такова, что появление положительного импульса на входе 9 обеспечивает разрешение прохождения сигналов с выхода 2i-:ro элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 на тактовый вход триггера 4 второй группы i-ro канала,кроме i п, и второй вход i-ro элемента И 3 второй группы, а также тактирует i-й элемент И 2 первой группы. По спаду положительного тактового импульса в триггеры 7 первой группы заносится информация о новом состоянии исследуемой схемы.

Каждый i-й анализатор 11, собранный на триггерах 7 первой группы и элементах ИСКЛЮЧАЮЩЕЕ ИЛИ 8 обес- печивает регистрацию событий нулевого уровня в точках (2i-l) и 2i схемы, к которым подключены соответствующие входы устройства. Регистрация указанных событий нулевого уровня сопровождается появлением единичного логического уровня на выходах соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 8,

При появлении события S в точке 1, подключенной к входу 1,1 устройства, на выходе первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 появляется логическая единица, поступающая на информационный вход первого триггера 4 второй группы, а также на первый вход первого элемента И 3 второй группы. Если на этом же такте произошло событие Sj в точке ., подключенной ко входу 1„2 устройства, то на выходе второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 также появляется логическая единица При подаче следующего тактового импульса этот импульс поступает через элемент И 2 первой группы, на втором входе которого также установлена логическая единица, на вход записи первого триггера 4 второй группы, и этот триггер переключается в единицу если произошло событие первого уровня в точках 1 и 2, подключенных к входам 1„1 и 1.2 первого канала устройства. Так как на первом входе первого элемента И 3 второй группы присутствует сигнал логической единицы, то тактовый имп ульс поступает на счетный вход первого счетчика 5 и в последний записьшается информация о том, что событие S произошло в первом канале.

Логическая единица с выхода первого триггера 4 второй группы поступает на третий вход элемента И 2 первой группы второго канала и является сигналом разрешения работы второ- му каналу устройства. Если в точках 3 и 4, подключенных соответствен но к входам 1„3 и 1.4, также произошло событие первого уровня S , то при поступлении тактового импульса на счетный вход второго триггера 4 вто- рой группы в триггер производится запись логической единицы аналогично первому каналу при условии, что первым каналом было зарегистрировано событие Sj на некотором предыдущем .такте Логическая единица на выходе . второго триггера 4 второй группы поступает на третий вход элемента И 2 третьего канала устройства, разрешая его работу, и т.д.,

Импульс, с выхода второго элемента И 3 второй группы поступает на счетный вход второго счетчика 5, который фиксирует событие S, Этот же импульс поступает на первый вход нулевой установки первого триггера 4 и осуществляет его сброс в ноль,тем самым запрещая фиксацию повторного события s вторым каналом устройст

ва до появления очередного события S , регистрацию которого осуществляет первый канал При регистрации первым каналом устройства события S осуществляется очередное разрешение работы второго канала включением второго элемента И 2.

Работа последнего канала заключается в следующем. При наличии сигнала разрешения работы п-го канала с выхода (n-l)-ro триггера 4 второй группы, а также появлении логических единиц на выходах п-го входного ана5 лизатора, что соответствует фиксации в п-м канале события S , тактовый импульс проходит через элемент И 2 первой группы и поступает на счетный вход п-го сч- етчика 5, который фикси0 РУбт событие S Тактовый импульс с выхода п-го элемента И 2 первой группы поступает на первый вход нулевой установки (n-l)-ro триггера 4 второй группы, и происходит сброс в ноль

5 данного триггера, тем самым запрещается фиксация п-м каналом повторного

S

события S

до регистрации (п-1)-к

h t

Элементы инди

кации осуществляют отображение содержимого счетчиков дпя ее визуального восприятия I

Использование двух элементов: И 2 первой группы и И 3 второй группы в каждом канале, кроме последнего, объясняется особенностью функционирования триггеров 4 второй группы,которая заключается в том, что триггер 4 второй группы должен устанавливаться в единицу, если в соответствующих парах точек, подключенных к данному каналу, произошло событие S, где i- иомер канала, если в промежуток времени между наступлением событий S и S, произошло событие нулевого уровйя во второй точке рассматриваемой пары, т.ео в точке 21, необходим сброс триггера 4 второй группы i-ro канала и блокировка ()-ro канала, так как в противном случае зарегистрированное событие может нести искаженную информацию об активизации соответствующего информационного пути, так как одной из причин возникновения события S%, может быть изменение логического уровня во второй точке пары (точка 2i) за счет цепей, не входящих в рассматриваем1 1Й информационный путь,

Формула изобретения Устройство для анализа состояний логических схем, содержащее первую группу из двух триггеров и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, причем тактовые входы триггеров первой группы объединены и подключены к входу синхронизации устройства, информационньй вход первого триггера первой группы соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом первого триггера первой группы, отличающееся тем, что, с целью распшрения функцио- нальных возможностей устройства путем обеспечения возможности регистрации степени активизации исследуемой логической схемы, в устройстве первая группа триггеров содержит 2(п-1) триггеров, и введены группа из 2п-1 элементов ИСКЛЮЧАКЯДЕЕ ИЛИ, первая группа из п элементов И, вторая груп- ha из п-1 элементов И, вторая группа из п-1 тр иггеров, группа из п счетчи- ков и группа из п элементов индикации, причем информационный вход 2i-ro триггера первой группы (i 1,2,о.,п) соединен с первым входом 21-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ группы, вторюй вход которого соединен с выходом 2i-ro триггеров первой группы, выход 2i-го элемента ИСКШ)- ЧАЮЩЕЕ ИЛИ группы соединен с первым входом i-ro элемента И первой группы второй вход которого объединен с

тактовыми входами триггеров первой группы и подключен к входу синхронизации устройства, выход (21-1)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ группы соединен с первым входом i-ro элемента И второй группы и информационным входом i-ro триггера группы, выход j-ro (,2, .,„,п-1) элемента И первой группы соединен с вторым входом j-ro элемента И второй группы и тактовым входом j-ro триггера второй группы, выход j-ro элемента И второй группы соединен со счетным входом j-ro счетчика группы и первым входом установки в О (j-I)-ro триггера второй группы-, выход J-ro триггера второй группы соединен с третьим входом (j+l)-ro элемента И первой группы, вторые входы установки в О триггеров второй группы объединены с входами установки в О счетчиков группы и подключены к входу начальной установки устройства, выходы i-ro счетчика группы соединены с .входами i-ro элемента индикации группы, выход (2п-1)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ группы соединен с четвертым входом п-го элемента И первой , выход которого соединен с тактовым.входом п-го счетчика группы и первым входом установки в О (п-1)-го триггера второй группы,информационные входы триггеров первой группы образуют группу информационны входов устройствао

| название | год | авторы | номер документа |

|---|---|---|---|

| Пороговое устройство (его варианты) | 1984 |

|

SU1352449A1 |

| Устройство для определения количества единиц в двоичном числе | 1981 |

|

SU964627A1 |

| Программное устройство для фиксации и документирования времени | 1989 |

|

SU1677691A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1981 |

|

SU999057A1 |

| Устройство для контроля количества единиц двоичного кода по модулю К | 1986 |

|

SU1401464A2 |

| Устройство для обнаружения ошибок при передаче данных по телефонному каналу | 1987 |

|

SU1559415A1 |

| Сигнатурный анализатор | 1984 |

|

SU1242957A1 |

| Устройство для контроля экспоненциальных процессов | 1987 |

|

SU1500997A1 |

| Устройство для вычисления ядер Винера нелинейных объектов | 1984 |

|

SU1196896A1 |

| Устройство для исследования графов | 1987 |

|

SU1411773A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при реализации средств контроля и диагностики отказов логических узлов. Цель изобретения - расширение функциональных возможностей устройства за счет возможности регистрации степени активизации исследуемой логической схемы. Устройство содержит группу 1 информационных входов, группу 2 элементов И, группу 3 элементов И, группу 4 триггеров, группу 5 счетчиков, группу 6 элементов индикации, группу 7 триггеров, группу 8 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вход 9 синхронизации устройства, вход 10 начальной установки устройства. Устройство позволяет получить информацию о числе логических перепадов, переданных по информационному пути исследуемой схемы, а также о числе переданных перепадов в промежуточных точках пути. Положительный эффект достигается за счет введения групп элементов И, ИСКЛЮЧАЮЩЕЕ ИЛИ, триггеров, счетчиков и элементов индикации. 1 ил.

| Электроника о ПереВо с англ,- 1982, № 4, G.66 | |||

| Титце Чо, Шенк .Ко Полупроводниковая схемртехникао - Mot Мир, 1982, с„ 362. |

Авторы

Даты

1989-08-07—Публикация

1987-12-21—Подача