() УСТРОЙСТВО для КОНТРОЛЯ ПАРАЛЛЕЛЬНОГО ДВОИЧНОГО КОДА НА ЧЕТНОСТЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1056199A1 |

| Устройство для контроля тупиков и восстановления работоспособности вычислительной системы | 1988 |

|

SU1601613A1 |

| Устройство для контроля параллельного кода на четность | 1983 |

|

SU1100626A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1277105A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

| Устройство для контроля цифровых интегральных микросхем | 1986 |

|

SU1354142A1 |

| Устройство для мажоритарного выбора сигналов | 1989 |

|

SU1656539A1 |

| Многоканальная микропрограммная управляющая система | 1985 |

|

SU1280628A1 |

| Мультимикропрограммное устройство управления с контролем | 1985 |

|

SU1272333A1 |

| Многоканальное устройство для обмена управляющей информацией в вычислительной системе | 1988 |

|

SU1566362A1 |

1

Изобретение относится к вычислительной технике и может быть исполь зовано для проверки на четность информации, применяемой в параллельном коде. -.

Известно устройство для контр ля }ia чётность цифровой информации,

содержащее регистр, логические схемьГ И и ИЛИ С1 D.

Известно также асинхронное устройство для определения четности информации, содер сащее регистр, элемент ИЛИ, триггер, два элемента И, второй и третий элементы ИЛИ, элементы И, .второй триггер, элемент задержки С2 «

Недостатком этих утсройств является их сложность.

Известно также устройство для : : контроля параллельного двоичного кода на четность, содержащее два элемента И, регистр, счетный триг-.

гер ГЗЗНедостатком устройства является низкое быстродействие,, обусловленное учетом положения единицы старшего разряда кода.

Наиболее близким по технической сущности и достигаетму результату к предлагаемому устройству является устройство содержащее регистр, два элемента ИЛИ, группу элементов И, fn элементов И (где m - разрядность проверяемого кода) , элемент И, счетный триггер, причем выход первого

10 элемента ИЛИ соединен с первым входом элемента И, второй вход которого является входом тактовых импульсов, а выход соединен с первыми входами первой группы элементов И выходы

15 которых соединены со входами второго элемента ИЛИ, выход которого соединен со счетным входом Т-триггеpatif.

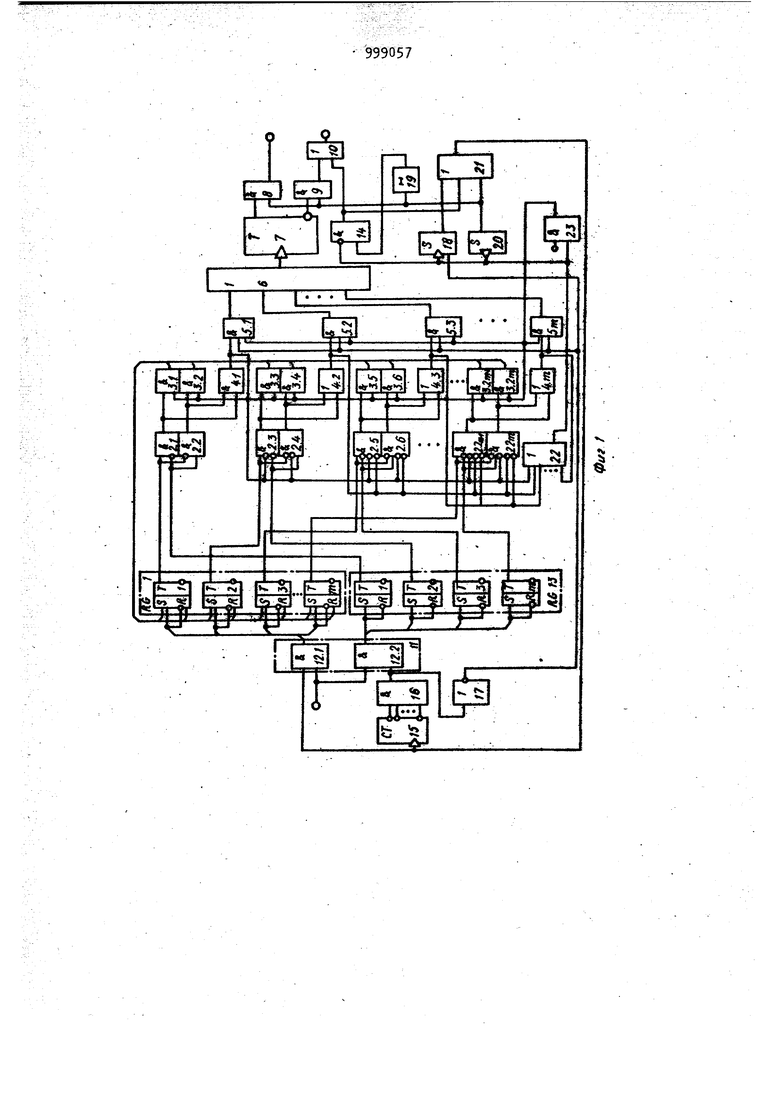

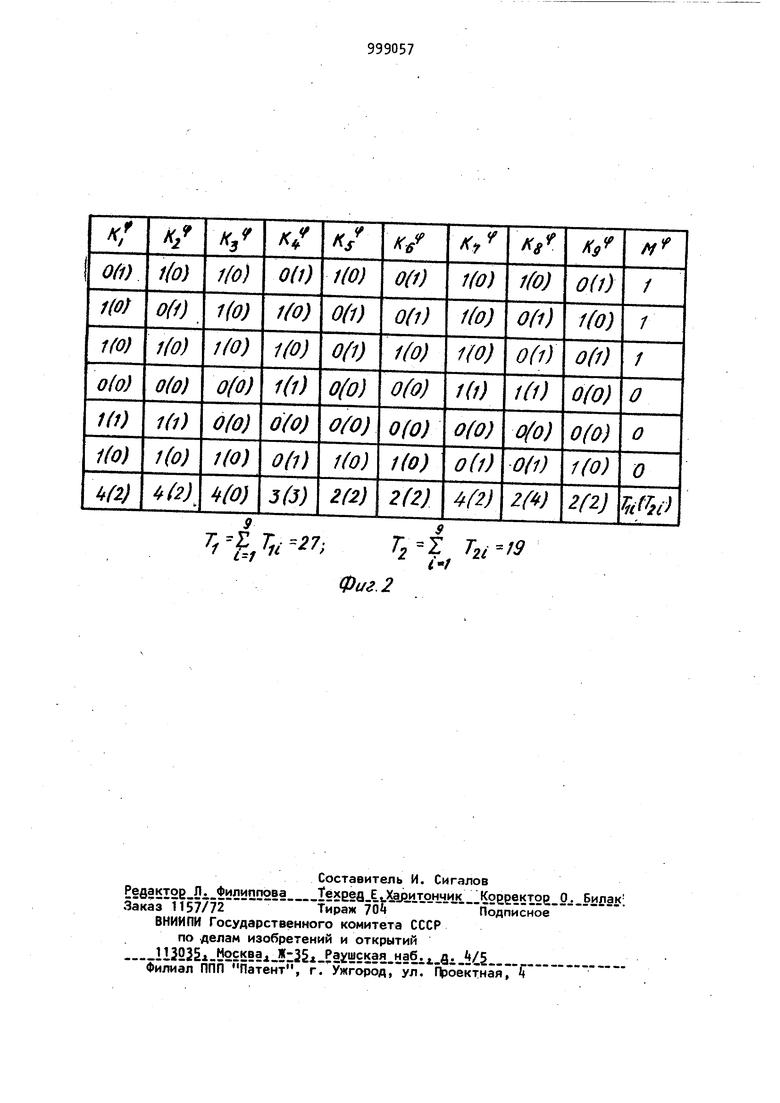

20 Недостатками известного устройст- ва являются его сложность и низкое быстродействие, обусловленное необходимостью опроса всех разрядов, которые находятся в единичном состоянии. а также необходимостью специального обнуления соответствующих разрядов послэ окончания процесса контроля кода на четность, что замедляет готовность устройства к контролю еледующей кодовой комбинации. , Многоразрядные коды с большим чи лом единиц требуют большого времени контроля, и следовательно обуславливают низкое быстродействие схемы. Целью изобретения является повыш ние быстродействия устройства. Поставленная цель достигается те что в устройство для контроля парал лельного кода на четность, содержащее регистр кода, первый и второй элементы ИЛИ, первую группу элемент И, первый и второй и третий элементы И и триггер, причем выход каждого элемента И группы соединен с соответствующим входом первого элемен та ИЛИ, выход которого соединен со счетным входом триггера, выход второго элемента ИЛИ соединен с первым входом первого элемента И, выход ко торого соединен с первыми входами всех элементов И первой группы, пря мой и инверсный выходы триггера сое динены с первыми входами второго и третьего элементов ИЛИ соответствен но, выход вторбго элемента И является первым выходом устройства, дополнительно введены регистр маски, коммутатор, счетчик, вторая и третья группы элементов И, группа элементов ИЛИ, первый и второй одновиб раторы, элемент задержки, третий и четвертый элементы ИЛИ, элемент НЕ, четвертый и пятый элементы И, причем информационный вход устройства соединен с информационным входом коммутатора, первая и вторая группы выходов которого соединены с информационными входами регистров кода , и маски соответственно, выход второго элемента ИЛИ соединен с инверс ным входом четвертого элемента И и входами первого и второго одновибраторов, выход которого соединен с первым входом третьего элемента ИЛИ через элемент задержки - с прямым входом четвертого элемента И и со вторыми входами второго и третьего элементов И, выход которого соединен с первым входом четвертого элемента ИЛИ, выход четвертого элемент И соединен со вторым вход®м третьего элемента ИЛИ и со вторым входом четвертого элемента ИЛИ, выход кото рого является вторым выходом устройства, выход первого одновибратора соединен с третьим входом третьего элемента ИЛИ, выход которого соединен со счетным входом счетчика и первым управляющим входом коммутатора, инверсные выходы счетчика соединены со входами пятого элемента И, выход которого соединен со вторым управляющим входом коммутатора и через элемент НЕ - со вторыми входами всех . элементов И первой- группы и управляющим входом первого одновибратора,выход i-ro разряда регистра кода (где i меняется от 1 до т, а m равно количеству разрядов контролируемого кода) соединен с прямым входом (2 i -1)-го элемента И и с первым инверсным входом 2 i-ro элемента И элементов И второй группы, а i-й выход регистра маски соединен с первым инверсным входом (2 i -1)-го элемента И и с прямым входом 2 i-ro элемента И элементов И второй группы, выходы (2 i -1)-го и 2 i-ro элементов И второй группы соединены с первыми входами (2i-1)-ro и 2i-ro элементов И третьей группы и со входами i-ro элемента ИЛИ элементов ИЛИ группы, выходы (2i-1)-ro и 2i-ro элементов И третьей группы соединены соответственно с единичным и нулевым входами i-ro разряда регистра кода, каждый выход i-ro элемента ИЛИ группы, где i меняется от 1 до (т-1), соединен с (i+1)-MH инверсными входами всех элементов И, от (2i-f1)-ro до 2 т-го элементов И второй группы и с i-м входом второго элемента ИЛИ, выход т-го элемента ИЛИ группы соединен с т-м входом второго элемента ИЛИ, выходы элементов ИЛИ группы соединены с третьими входами соответствующих элементов И первой группы, выход первого элемента И соединен со вторыми входами элементов И третьей группы. Сущность изобретения состоит в повышении быстродействия устройства за счет уменьшения числа единиц в коде путем маскирования контролируемых кодов обобщенно- статистическим кодом. Каждому пакету кодов (сист-еме пёредачи данных а целом) n(KjJ , К... ...Кд) ( - разрядный двоичный код, - длина пакета) может быть поставлен в соответствие обобщенный код - маска М (fJi.f,...,} значенуе разрядов которого вычисляются по формуле г если - V- Y ГГ) ./-r-i У., Ч m . О, если е.. , . - значение j-ro разряда kf, m ПЛг. j-и . Полученная таким образом маска м(ЛГ хранится в специальном J/J-.1 регистре и после поступления каждог контролируемого кода К осуществляется их поразрядное сумг-1ирование по модулю два . V / (/ Y 4/ 1 Г.-1Г г. г / J V 1 12-%тт1/ - tf (f {и -дег,с;;©м7 6 формируемом коде Г4 число един будет существенно меньше, чем в исходном коде К, благодаря чему процесс дешифрации кода (определение ;четности) ускорится. Введение этих элементов и их свя зей позволяет повысить быстродействие устройства за счет уменьшения . числа единиц в коде путем маскирования поступающих кодов. На фиг. 1 представлена функциональная схема устройства для контро ля параллельных кодов на четность; на фиг. 2 - пример контролируемого пакета кодов. Устройство содержит регистр 1 ко да, вторую группу элементов И 2, тр тью группу элементов И 3, группу эл ;ментов ИЛИ 4, первую группу элементов И 5, первый элемент ИЛИ 6, три1- гер 7 второй 8 и третий 9 элементы И, четвертый элемент ИЛИ 10, коммутатор 11 состоящий из первого 12.1 и второго 12.2. элементов И, регистр 13 маски, четвертый элемент И Т, счетчик 15 пятый элемент И 1 элемент НЕ 17, первый одновибратор 18, элемент задержки 19, второй одновибратор 20, третий элемент ИЛИ 2 второй элемент ИЛИ 22, первый элемент И 23. На фиг. 2 использованы следующие обозначения: 74 о контролируемые коды (в скобках записаны значения разрядов после маскирования; М маска для данного пакета ко flpB; Т и Т2 - время контроля (число единиц) i-ro кода до и после маскирования. Регистр 1 предназначен для хранения кодов, контролируемых на нечетность и поступающих из канала. Входы регистра 1 соединены парафазно с выходами группы элементов И П. Через открытые элементы И этой группы информация поступает в регистр 1. Единичные выходы каждого разряда регистра 1 соединены со входами группы элементов И 2. На вторые входы элементов И второй труппы поступают операнды с регистра 13 маски в которой маска записывается через группу элементов И 12 и хранится до конца проверки i-ro пакета кодов. Если после сложения по модулю два каких-либо разрядов на выходе группы элементов И 2 появится единичный сигнал, то он через группу элементов ИЛИ t, группу элементов И 5 и элемент ИЛИ 6 записывается в триггер 7, а также через группу элементов И 3 пройдет на соответствующие входы регистра 1 кода. Сострян ия регистра меняются таким образом, чтобы на выходе элементов И 2, которым соответствует единичная информация, появился ноль,Выходы элементов ИЛИ группы элементов ИЛИ А соединены с инверсными входами группы элементов И 2 и со входами элемента ИЛИ 22, который обладает задержкой на выключение (Г 21пер). Единица на выходе элемента ИЛИ 22, появляется при сложеНИИ по модулю два маски и нулевого кода первого регистра и остается до тех пор, пока не будет проверен весь код. Это позволяет подавать в схему тактовые импульсы, управлять счетчиком через одновмбратор 18, который срабатывает при отсутствии сигнола на управляющем входе, и вы-, дачей конечного результата через одновибратор 20 и элементы И 8 и Ч. По окончании проверки i-ro кода на выходе элемента ИЛИ 22 появляется нулевой сигнал и одновибратор 20 вырабатывает импульсы, по которым счетчик 15 переводится в первое сое-. тояние и код из канала поступает на регистр кода. Элемент НЕ 17 предназначен для того, чтобы при отсутствии информации в регистре 1 исключить запись информации в триггер 7. При равенстве нулю .суммы по модулю два маски и кода, сигнал на выходе элемента ИЛИ 22 исчезает. Задержанный первый импульс с выхода одновибратора 20 поступает на вход элемента И 1А и едиричный сигнал, соответствующий четному коду, проходит через элемент ИЛИ 10 на выход устрой ства. Время задержки элемента выбирается из условия , где Т - период времени поступления кодов на вход устройства. В исходном состоянии оба регистра 1 и 13 находятся в нулевом состоянии счетчик 15 тактов также находится в нулевом состоянии. Элемент И 16 от кр.ыт, открыты элементы И группы элементов И 12, с выхода элемента НЕ 17 на входы элементов И 5 поступает нулевой сигнал, триггер 7 находится в нулевом состоянии. Предлагаемое устройство работает следующим образом. Записанная в первой кодовой комби нации маска поступает на вход устрой ства и через открытые элементы И 12 группы элементов И поступает в регистр 13- Затем происхрдит сложение по модулю два содержимого обоих регистров. На выходе одного из элементов ИЛИ группы элементов ИЛИ k появляется единичный сигнал, который поступает на соответствующий вход элемента ИЛИ 22. На выходе элемента ИЛИ 22 появляется единичный сигнал, который открывает элемент И 23 и поступает на одновибратор 18, которь1Й вырабатывает управляющий сигнал. Эле менты И первой группы элементов И 5 закрыты и триггер 7 остается в исходном состоянии. Управляющий сигнал с выхода элемента ИЛИ 21 переводит счетчик 15 в первое состояние и открывает элементы И группы элементов И 11. При изменении нулевого состояния счетчика 15 закрмвается группа элементов И 12, а разрешающий сигнал с выхода элемента НЕ 17 поступает на входы группы элементов И 5. Контролируемая цифровая информация в .виде параллельного кода посту пает на входы регистра 1 через груп-, пу элементов И 11 и записывается в нем. Пусть, например, в регистр 13 записана маска 1010, а первый код Kdторый должен быть проверен на четность - 1110. При сложении по модулю два первых разрядов на выходе элементов И 2.1, 2.2 группы элементов И 2 сигнал будет отсутствовать и на выходе первого элемента ИЛИ группы элементов ИЛИ Ц появится нулевой сигнал. При сложении вторых разрядов на выходе элемента И 2.3 появится единица, которая пройдет на выход элемента ИЛИ . .2 группы элементов ИЛИ Ц и оставит единичный сигнал на выходе элемента ИЛИ .22 в единичном состоянии. Благодаря тактовым импульсам, поступающим на входы элементов И групп элементов И 3 и 5 эти элементы открыты и единица с выхода элемента И 2.3 проходит через элемент И 3.3 и устанавливает в нуль второй триггер регистра 1, а также проходит через элемент И 5.2 и элемент ИЛИ 6 на . вход триггера 7, переводя его в противоположное состояние. Нулевой потенциал с выхода второго триггера регистра 1 при сложении со вторым разрядом регистра 13 дает нулевой сигнал на выходе элемента И 2.3 и затем на выходе элемента ИЛИ Ц.2, Элементы И 2,5-2.2 m открываются, Kja них поступает информация с остальных разрядов регистра. На входы элемента ИЛИ 22 поступают нулевые сигналы с выхода всех элементов ИЛИ группы элементов ИЛИ 4 и сигнал на выходе элемента ИЛИ 22 исчезает. Элемент И 23 закрывается и тактовые импульсы перестают поступать в схему, по перепаду из 1 в О вырабатывается импульс одновибратором 20. Этот импульс открывает элементы И 8 ;Л 9. и информация о состоянии триггера, а, соответственно, и о четности или нечетности контролируемого кода, проходит через один из этих элементов на выход схемы (в данном случае с выхода триггера 7 считывается единичный сигнал ). По этому же импульсу с выхода одновибратора 20 происходит переключение счетчика 15 8 следующее состояние и очередной код поступает через вторую группу элементов И 11 на вход регистра 1, 9 . Таким образом, проверка на четность кода 1110 происходит за один такт вместо трех. При работе устройства может возниктуть случай, когда сумма по модулю два кода и маски станет равной нулю Д например, код 1010 и маска 1010). В этом случае при сложении маски и первоначального состояния регистра 1 на выходе элемента ИЛИ 22 остается нулевой сигнал и импульс с выхода одновибратора 20, задержанный элементом задержки 19 на время, .необходимое для записи в регистр 1 следующего кода,поступит на вход эле меИта И 14.. Так как сумма по модулю два маски и кода равны нулю,то на вы ходе всех m элементов ИЛИ группы эле ментов ИЛИ it и элемента 22 сигнал бу деГ отсутствовать. В результате импульс с выхода элемента задержки 19 ;пройдет через открытый элемент И 1 элемент ИЛИ 10 на выход схемы,что бу дет свидетельствовать о четном числе единиц ив прюверяемом коде. Счет чик 15 по этому импульсу переклю- чается.в следующее состояние и на регистр 1 записывается очередной код. После проверки всех кодов, поступивших для контроля, счетчик возвращается в нулевое состояние и устг ройство готово для приема очередной маски. Формула изобретения Устройство для контроля параллель ного двоичного кода на четность, содержащее регистр кода, первый и второй элементы ИЛИ, первую группу эле. ментов И, первый, второй и третий элементы И и триггер, причем выход каждого элемента И группы соединен с соответствующим входом первого эле мента ИЛИ, выход которого соединен со счетным входом триггера, выход второго элемента ИЛИ соединен с первым входом первого элемента И, выход которого соединен с первыми вхо:дами элементов И первой группы, прямой и инверсные выходы триггера соединены с первыми входами второго и третьего элементов ИЛИ соответственно, выход второго элементами является первым выходом устройства, от личающееся тем, что, с целью повышения быстродействия« в 7 него введены регистр маски, коммутатор, счетчик, вторая и третья группы элементов И, группа элементов ИЛИ, первый и второй одновибраторы, элемент задерхжи, третий и четвер- тый элементы ИЛИ, элемент НЕ, четвертый и пятый элементы И, причем информационный вход устройства соединен с информационным входом коммутатора, первая и вторая группы выходов которого соединены с информационными входами регистров кода и маски соответственно, выход второго элемента ИЛИ соединен с инверсным входом четвертого элемента И и входами первого и второго одновибраторовi выход которого соединен с первым входом третьего элемента ИЛИ, через элемент задержки - с прямым входом четвертого элемента И и со вторыми входами второго и третьего элементов И, выход которого соединен .с первым входом четвертого элемента ИЛИ, выход четвертого элемента И соединен со вторым, входом третьего элемента ИЛИ и со вторым входом четвертого элемента ИЛИ, выход которого является вторым выходом устройства, выход первого одновибратора соединен с третьим входом третьего элемента ИЛИ, выход которого соединен со счетным входом счетчика и первым управляющим входом коммутатора, инверсные выходы счетчика соединены со входами пятого, элемента И, выход которого соединен со вторым управляющим входом коммутатора и через элемент НЕ - со вторыми входами всех элементов И первой группы и управляющим входом первого одновибратора выход i-ro разряда регистра кода (гДе , am равно количеству разрядов контроли- . руемого кода) соединен с прямым входом (2i-1)-ro элемента И и с первым инверсным входом 2 i-ro элемента И второй группы, i-й выход регистра маски соединен с первым инверсным входом (2i-1)-ro элемента И и с прямым входом 2-i-ro элемента И второй группы, выходы (2i-1)-го и 2 i-ro элементов И второй группы соединены с.первыми входами (2i-1)-ro и 2 i-ro элементов И третьей группы и со вхоами i-ro элемента ИЛИ группы, выхо-с ы (2i-1)-ro и 2 i-ro элементов И ретьей группы -соединены соответственно с единичным и нулевым входом i-j-o разряда регистра кода, каждый

выход i-го элемента ИЛИ группы, где i 1-(т-1) соединен с (i+1) инверсными входами длементов И, от (21+1)-го до 2 т-го второй группы и с i-м входом второго элемента ИЛИ, выход m -го элемента ИЛИ группы соединен с т-м входом второго элемента ИЛИ, выходы элементов ИЛИ группы соединены с третьими входами соответствующих элементов И первой группы, выход первого элемента И соединен со вторыми входами элементов И третьей группы.

Источники информации, принятые во внимание при экспертизе

свидетельство СССР

т:7 Г tf

фиг. 2

Авторы

Даты

1983-02-23—Публикация

1981-07-02—Подача