рым выходами первой группы выходов блока управления, первый становочный вход блока формирования первого аргумента соединен с первым входом блока управления и является запускакнцим входом устройства, второй выход блока управления соединен с управляющим входом блока регистров третий и четвертый выходы блока управления соединены с управляющими входами соответственно первого и второго сумматоров и вторыми устано вочными входами соответстйенно блоков формирования второго и третьег аргументов, выходы второй группы выходов блока управления соединены соответственно с тактовыми входами блоков формирования первого, второго и третьего аргументов, первые информационные выходы блоков .формир вания первого , второго и третьего аргументов соединены с соответствующими входами первой группы входов блока управления, второй информацио ный выход блока формирования первог аргумента соединен с первым информа ционным входом первого сумматора, первыми информационными входами бло ков формирования второго и третьего аргументов, соответствующим входом второй, группы входов блока управления и первым и вторым информацион ными входами первой группы входов в рого мультиплексора, третий информационный вход группы является входо логической единицы устройства, выход первого сумматора соединен с соответствующим информационным входом второй группы входов второго мультиплексора, вторыми информационными вх дами блоков формирования второго и третьего аргументов и первым информа ционным входом второго сумматора, вы ход которого соединен с соответству ющим информационным входом.третьей группы входов второго мультиплексора и третьим информационным входом блока формирования третьего аргумента второй информационный.выход которого соединен с вторым информационным входом второго сумматора и соответствующим информационным входом третьей группы входов второго мультиплексора и вторым входом второй группы входов блока управления, второй информационный выход блока формирования второго аргумента соединен с вторым информационным входом первого сумматора, четвертым информационным входом блока формирования 96 третьего аргумента,с соответствующим информационным входом второй группы входов второго мультиплексора; и третьим входом второй группы входов блока управления, третий и четвертый выходы которого соединены с третьими информационными входами соответственно второй и третьей групп входов второго мультиплексора, первый, второй и третий выходы которого соединены соответственно с адресными входами первого и второго блоков памяти и управляющим входом сумматора по модулю М, причем блок управления содержит первый, второй и третий триггеры, первую, вторую, третью и четвертую группы элементов И, первый, второй и третий элементы задержки, распределитель импульсов, блок выбора аргументов, первый и второй элементы И, первый и второй элементы ИЛИ, регистр сдвига счетчик и дешифратор, выход которого соединен с первым входом первого элемента И, выход которого соединен с первым входом первого триггера, выход первого элемента ИЛИ соединен с вторым входом первого триггера, прямой выход которого соединен с первым управляющим входом распределителя импульсов,а адресный выход является первым выходом блока управления и соединен с входами счетчика и первого элемента задержки,выход которого соединен с вторым входом первого элемента И, выход счетчика соединен с входом дешифратора, первый выход распределителя импульсов соединен с первыми входами элементов И первой группы непосредственно и через второй элемент задержки - с первым входом сдвига регистра сдвига, второй выход распределителя импульсов соединен с первым входом второго элемента И непосредственно и через ретий, элемент задержки с первыми ходами элементов И второй группы, ыход второго элемента И соединен вторым входом сдвига регистра двига, первые входы второго и ретьего триггеров соединены соотетственно с выходами первого и втоого элементов И первой группы, перые входы элементов И четвертой групы соединены соответственно с инверсыми выходами второго и третьего риггеров-, а вторые входы объединеы с вторьми входами второго и третьго триггеров, выходы элементов И четвертой группы соединены с первыми входами соответствующих элементов И третьей группы, выходы которых сое динены соответственно с первым и вто рым входами второго элемента ИЛИ,выход которого соединен с вторым управ ляющим входом распределителя импульсов, прямой выход блока выбора аргуме тов соединен с третьим входом второго элемента ИЛИ, а инверсный выход с вторым входом второго элемента И, выход первого разряда регистра сдвига соединен с вторыми входами первых элементов И первой и второй групп,выход второго разряда регистра сдвига соединен с вторыми входами вторых элементов И первой и второй групп и первого элемента И третьей группы, выход третьего разряда регистра сдвига соединен с вторыми входами третьих элементов И первой и второй групп и второго элемента И третьей группы, выход четвертого раз ряда регистра сдвига соединен с четвертым входом второго элемента ИЛИ, первый, второй информационные и первый, второй управляющие входы блока выбора аргументов соединены соответственно с инверсным выходами второго и третьего триггеров и выходами второго и третьего разрядов регистра сдвига, прямые выходы второго и третьего триггеров являются третьим и четвертым выходами блока управления, выходы элементов И первой группы образу:от первую группу выходов блока управления , выходы первого, второго и третьего разрядо регистра сдвига образуют второй выход блока управления, а выходы элементов И второй группы являются вто рой группой выходов блока управлени первый вход первого элемента ИЛИ яв ляется первым входом блока управления, вторые входы первого элемента ИЛИ, второго и третьего триггеров образуют первую группу входов блока управления, группа входов блока выбора аргументов является второй гру пой входов блока управления, при этом блок формирования первого аргу мента содержит счетчик, схему сравнения и элемент ИЛИ, первый вход которого является установочным входом блока формирования первого аргу мента, выход элемента ИЛИ соединен с установочным входом счетчика, счетный вход которого является тактовьм входом блока формирования пер вого аргумента, первый вход схемы 1 6 сравнения соединен с шиной предельного значения аргументов суммирующий вход счетчика- соединен с шиной логической единицы, а его выход - с вторым входом схемы сравнения и является вторым информационным выходом блока, выход схемы сравнения соединен с вторым входом элемента ИЛИ и является первым информационным выходом блока формирования первого аргумента, блок формирования второго аргумента содержит счетчик, первую и вторую схемы сравнения, первый и второй элемен ты ИЛИ, элемент И, первый вход первого элемента ИЛИ является первым установочным входом блока, а второй вход первого элемента ИЛИ подключен к первому входу элемента И и является вторым установочным входом блока формирования второго аргумента, второй вход элемента И соединен с выходом первой схемы сравнения блока, пер,В1лй вход которой соединен с шиной предельного значения суммы аргументов,а второй вход первой схемы сравнения является вторым информационным входом блока формирования второго аргумента, счётный вход счетчика является тактовым входом блока, установочньй вход счетчика соединен с выходом первого элемента ИЛИ, суммирующий вход счетчика является первым информационным входом блока формирования второго аргумента,а выход счетчика соединен с первым входом второй схемы сравнения и является вторым информационным выходом блока, второй вход второй схемы сравнения соединен с шиной предельного значения аргументов, выход второй схемы сравнения соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом элемента И, а выход является первым информационным выходом блока формирования второго аргумента, блок формирования третьего аргумента содержит счетчик, первую, вторую, третью схемы сравнения, первьш второй мультиплексоры, первый второй элементы ИЛИ, и элемент И, первый вход первого элемента ИЛИ является первым установочным входом блока формирования третьего аргумента, второй установочный вход которого соединен с вторым входом первого элемента ИЛИ, управляющю входом второго мультиплексора и первым входом элемента И, второй вход которого соединен с выходом второй схемы сравнения, тактовый вход блока формирования третьего аргумента соединен со счетньм входом счетчика установочный и суммирующий входы которого соединены с выходами соответственно первого элемента ИЛИ и второго мультиплексора, первый информационный вход которого соединен с выходом первого мультиплексора управляющий, вход которого соединен с выходом первой схемы сравнения, первый информационный вход блока фор мирования третьего аргумента соединен с первым информационным входом первой схемы сравнения и первым информационным входом первого мультиплексора, второй информационный вход блока формирования третьего аргумента соединен с вторым информационным входом первой схемы сравнения и вторым информационным входом первого мультиплексора, третий и четвер тый информационные входы блока форми рования третьего аргумента соединены соответственно с первым информационным входом второй схемы сравнения и вторым информационным входом второго мультиплексора, выход элемента И соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом третьей схемы сравнения, а выход второго элемента ИЛИ является первым информационным выходом блока формирования третьего, аргумента, выход счетчика соединен с первым информационным входом третьей схемы сравнения и является вторым информационным выходом блока формирования третьего аргумента, вторые ,информационные входы второй и третье.й схем сравнения соединены с шинами предельного значения аргументов и суммы аргументов соответственно, блок выбора аргументов содержит первый и .второй мультиплексоры,схему сравнения, элементы И и НЕ, группа; информационных входов блока выбора аргументов соединена с группой информационных входов первого мультиплексора, первый и второй информационные выходы которого соединены с первым и вторым информационными входами схемы сравнения, выход которой соединен с первьм входом элемента И, второй вход которого соединен с выходом второго мультиплексора,первый и второй управляющие входы блока выбора аргументов соединены соответственно с первым и вторым управляющими входами первого и второго мультиплексоров.,первый и второй информационные входы второго мультиплексора являются первым и вторьм информационными входами блока выбора аргументов, выход элемента И является прямым информационным выходом блока выбора аргументов и соединен с входом элемента НЕ, выход которого является инверсным информационньм выходом блока выбора аргументов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения фазовых сдвигов | 1984 |

|

SU1226341A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Генератор функций Уолша | 1984 |

|

SU1166134A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ | 1988 |

|

SU1755650A1 |

| Устройство для вычисления квадратного корня | 1983 |

|

SU1141407A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1035604A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU940155A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| Цифровой анализатор спектра | 1987 |

|

SU1413545A1 |

| Устройство для определения взаимной корреляционной функции | 1990 |

|

SU1751779A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЯДЕР ВИНЕРА НЕЛИНЕЙНЫХ ОБЪЕКТОВ, содержащее блок обратного дискретного преобразования Фурье, первый блок буферной памяти, блок усреднения, а также последовательно соединенные исследуемый объект,аналого-цифровой преобразователь, второй блок буферной памяти и блок прямого дискретного преобразования Фурье,выход которого соединен с информационным входом первого блока памяти, о тличающееся тем, что, с целью повьшения быстродействия, в него введены датчик случайных чисел, блок постоянной памяти, первый и второй мультиплексоры, цифроаналоговый преобразователь, элемент ИЖ, сумматор по модулю М,блок регистров, второй блок памяти, третий блок буферной памяти, умножитель, блоки формирования первого, второго и третьего аргу ентов, первый и второй сумматоры и блок управления, причем выход датчика случайHbix чисел соединен с первым информационным входом первого мультиплексора - и информационным входом третьего блока буферной памяти, выход которого соединён с информационным входом второго блока памяти, выход блока постоянной памяти соединён с первым входом умножителя и входом блока обратного дискретного преобразования Фурье, выход которого через последовательно соединенные первый блок буферной памяти и цифроаналоговый преобразователь соединен с входом исследуемого объекта, выход первого мультиплексора соединен с входом блока постоянной памяти, выход сумматора по подулю М соединен с вторым информа§ ционным входом первого мультиплексора и информационным входом, блока (Л регистров, выход которого соединен с первым информационным входом сумматора по модулю М, выход первого блока памяти соединен с вторым входом умножителя, выход которого соединен с первым информационным входом блока усреднения, выход вто;о рого блока памяти соединен с вторым Oi 00 информационным входом сумматора по модулю М, первый выход блока со а управления соединен с управляющим входом первого мультиплексора,установочным входом блока усреднения и входами управления записью-считыванием первого и второго блоков памяти, первая группа выходов блока управления соединена с группой уп- равлякндих входов второго мультиплексора и группой входов элемента ИЛИ, выход которого соединен с тактовым входом блока усреднения, первые установочные входы блоков формирования второго и третьего аргументов соединены соответственно с первым и вто

I

Изобретение относится к айтоматике и вычислительной технике и может быть использовано в системах автоматического управления для идентификации нелинейных объектов, а также в экспериментальных исследованиях систем различной физической природы.

Цель изобретения - повышение быстродействия устройства.

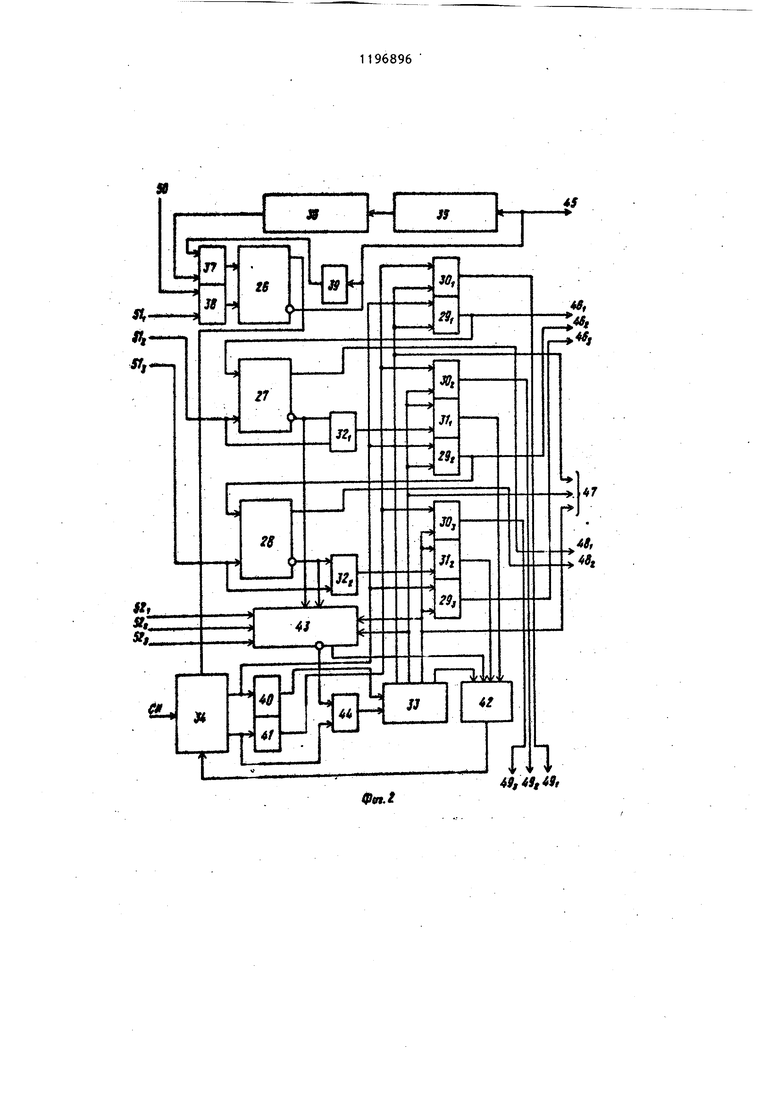

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 - блок-схема блока управления; на фиг. 3 - блок-схема блока формирования первого аргумента; на . 4 - блок-схема блока формирования второго аргумента; на фиг. 5 - блок-схема блока формирования третьего аргумента; на фиг.6 блок-схема блока выбора аргументов.

Устройство для вычисления ядер Винера нелинейных объектов содержит последовательно соединенные

блок 1 обратного дискретного преобразования Фурье (ДПФ), первый блок 2 буферной памяти, цифроаналоговый преобразователь (ЦАП) 3, исследуемый объект 4, аналого-цифровой преобразователь (АЦП) 5, второй блок 6 буферной памяти и блок 7 прямого ДПФ, первый блок 8 памяти, датчик 9 случайных чисел, второй

10 и третий 11 блоки памяти, постоянное запоминающее устройство 12, первый мультиплексор 13, сумма3

гор 14 по модулю М, блок 15 регистров, умножитель 16, блок 17 усреднения, элемент ИЛИ 18. блоки 19-21 формирования первого, второго и третьего аргументов, первьй 22 и второй 23 сумматоры, второй мультиплексор 24 и блок 25 управления.

Выход датчика 9 случайных чисел соединен с первым информационным входом первого мультиплексора 13 и информационным входом второго блока 10 памяти, выход которого соединен с информационным входом третьего блока 1 Г памяти.Выход первого мультиплексора 13 соединен с входом постоянного запоминающего устройства 12,выход которого соединен с первым входом умножителя 16 и входом блока 1 обратного ДПФ. Выход сумматора 14 по подулю М соединен с вторым информационным входом первого мультиплексора 13 и информационным входом блока 15 регистров, выход которого соединен с первым информационным входом сумматора 14 по модулю М. Выход первого блока 8 памяти соединен с вторым входом умножителя 16, выход которого соединен с информационным входом блока 17 усреднения. Выход третьего блока 11 памяти соединен с вторым информационным входом сумматора 14 по модулю М. Выход блока 7 прямого ДПФ соединен с информационным входом первого блока 8 памяти. Первый выход .блока 25 управления соединен с управляющим входом первого мультиплексора 13, управляющими входами первого 8 и третьего 11 блоков памяти и первым управляющим входом блока 17 усреднения.

Первая группа выходов блока 25 управления соединена .с управляющими входами второго мультиплексора 24 и входами элемента ИЛИ 18, выход которого соединен с вторым, управляющим входом блока 17 усреднения. Первые входы блоков 20 и 21 формирования второго и третьего аргументов соединены соответственно с первыми двумя выходами первой группы вь ходов блока 23 управления. Первый вход блока 19 формирования певого аргумента соединен с первым входом блока 25 управления и является установочным запускающим -бходом устройства Вторая группа выходов блока 25 упраления соединена с группой управляючи

6896

входов блока 15 регистров. Второй и третий выход| 1 блока 25 управления соединены с управляющими входами сумматоров 22, 23 и вторыми входами

блоков 20 и 21 формирования второго и третьего аргументов.

Третья группа выходов блока 25 управления соединена с вторым входом блока 19 формирования первого аргумента и третьими входами блоков 20 и 21 формирования второго и третьего аргументов. Выход первого сумматора 22 -соединен с первым информационным входом второго сумматора 23, пятыми

5 входами блока 20 формирования второго аргумента и блока 21 формирования третьего аргумента, шестой вход которого соединен с выходом второго сумматора 23. Первые входы блоков

0 19-21 формирования первого, второго и третьего аргументов соединены с первой группой входов блока 25 управления. Второй выход блока 19 формирования первого аргумента соеди5 ней с первым информационным входом первого сумматора 22 и четвертыми входами блоков 20 и 21 формирования второго и третьего.аргументов.Вторые выходы блоков 20 и 21 формирования второго и третьего аргументов соединены с вторыми информационными входами соответственно первого 22 и второго 23 сумматоров.

Вторая группа входов блока 25 J управления соединена с вторыми выходами блоков 19-21 формирования первого, второго и третьего аргументов. Второй выход блока 20 формирования второго аргумента соединен с седьQ мым входом блока 21 формирования

третьего аргумента. Первые два входа первой группы входов мультиплексора 24 соединены с вторым выходом блока 19 формирования первого аргумен-i j та, а третий вход данной группы

соединен с логической единидей.Выход первого сумматора 22, второй выход блока 20 формирования второго аргумента и второй выход блока 25 управления образуют вторую группу информационных входов второго мультиплексора 24. Выход второго сумматора 23, второй выход блока 21 формирования третьего аргумента и третий выход блока 25 управления образуют третью группу информационных входов второго мультиплексора 24, первый, второй и третий выходы которого соединены соответственно с адресными входами первого. 8 и трет его 11 блоков памяти и управляющим входом сумматора 14 по модулю М. Блок 25 управления (фиг. 2) содержит первьй 26, второй 27 и третий 28-триггеры, первую группу элементов И 29, вторую группу элементов И 30 - 30j, третью группу элементов И 31 и 31, четвертую группу элементов И 32., и 32- регистр 33 сдвига, распределитель 34 импульсов, счетчик 35, дешифратор 36, первый элемент И 37, первый элемент ИЛИ 38, первый 39, второй 40 и третий 41 элементы заде ки, второй элемент ИЛИ 42, блок 43 выбора аргументов,второй элемент И 44, первый выход 45, первую группу 46 - 46, выходов, вторую группу выходов 47, второй и третий выходы 48t И 48г, третью группу 491 - 493 выходов, первый вход 50, первую группу 5li- 523 входов и вторую группу 52.- 53 входов. счетчика 35 через дешифратор 36 соединен с первым входом пер вого элемента И 37, выход которого соединен с первым входом первого триггера 26. Выход первого элемент ИЛИ 38 соединен с вторым входом пер вого триггера 26, прямой выход кото рого соединен с первым управляющим входом распределителя 34 импульсов а инверсный выход - с входами счетч ка 35 и первого элемента 39 задержки, выход которого соединен с вторы входом первого элемента И 37, Первы выход распределителя 34 импульсов соединен с первыми входами элементо И 29., - 29i первой группы и через второй элемент 40 задержки с первым входом регистра 33 сдвига. Второй выход распределителя 34 ш пульсов соединен с входом третьего элемента 41 задержки и первым входом второго элемента И 44, выход которого соеди нен с вторым входом регистра 33 сдвига. Выход третьего элемента 41 задержки соединен с первыми вход4ми элементов И 30 30 j второй группы. Первые входы второго 27 и третьего 28 триггеров соединены соответственно с выходами первого 29., и второго 29, элементов ,., .. элементов И первой группы. Первые входы элементов И 32 и 32 четвертой группы соединены соответственно с инверсны ми выходами второго 27 и третьего 28 триггеров, а вторые входы - с вторыми входами второго 27 и третьего 28 триггеров. Выходы элементов И 32 и 32 четвертой группы соединены с первыми входами соответствующих элементов И ЗЦ и 3lj третьей группы, выходы которых соединены соответственно с первым и вторым входами второго элемента ИЛИ 42, выход которого соединен с вторым управляющим входом распределителя 34 импульсов. Выход первого разряда регистра 33 сдвига соединен с вторьми входами первых элементов И 29 , 30., первой и второй групп. Выход второго разряда регистра 33 сдвига соединен с вторьв4и входами вторых элементов И 292, 30j первой и второй групп и вторым входом первого элемента И 31 ., третьей группы Выход третьего разряда регистра 33 сдвига соединен с вторыми входами третьих элементов И 29,, 30j первой и второй групп и вторым входом второго элемента И 312 третьей группы. Выход четвертого разряда регистра 33 сдвига соединен с четвертьм входом второго элемента ИЛИ 42. Инверсные выходы второго 27 и третьего 28 триггеров соединены с первым и вторым входами блока 43 сравнения аргументов, прямой и инверсный выходы которого соединены соответственно с третьим входом второго элемента Ш1И 42 и вторым входом второго элемента И 44, выходы второго и третьего разрядов регистра 33 сдвига соединены с треть№1 и четвертым входами блока 43 сравнения аргументов. Инверсный выход первого триггера 26 является первым выходом 45 блока 25 управления, выходы первого, второго и третьего разрядов регистра 33 сдвига являются второй группой выходов 47 блока.25 управления. Выходы элементов И 29 3 первой группы образуют первую группу , 46j выходов блока 25 управления. Прямые выходы второго 27 и третьего 28 триггеров образуют второй и третий 48., и 48 j выходы блока 25 управления. Выходы элементов И 30., - 30 второй группы образуют третью группу 49д 49 вьцсодов блока управления. Первый вход первого элемента ШШ 38 является, первым входом 50 блока 25 правления. Вторые входы первого элемента ШШ 38 второго 27 и

7

третьего 28 триггеров образуют первую группу 51 з входов блока 25 управления. Группа входов блока 43 сравнения аргументов является второй группой 52 - 52, входов блока 25 управления, а информационный вход распределителя 34 импульсов является входом синхронизации устройства.

Блок 17 усреднения содержит блок 17 памяти ядер, счетчик 17 адреса и сумматор 17 , первый вход которого является информационным входом блока 17 усреднения, Выход счетчика 17 адреса соединен с адресным входом блока 17 памяти ядер, выход которого соединен с вторым входом сумматора 17j , выход которого подключен к входу блока 17 памяти ядер.Вход сброса счетчик 17j адреса является первым управляющим входом блока 17 усреднения, а его счетный вход - вторым управляющим входом блока 17 усреднения.

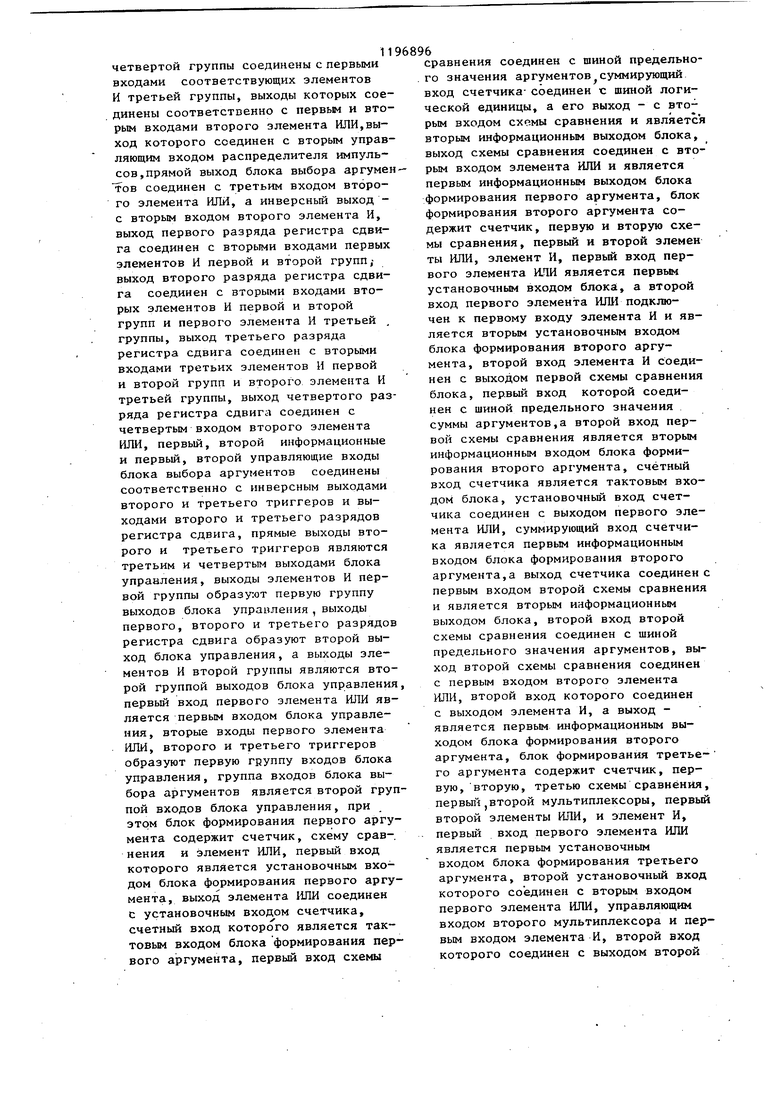

Блок 19 формирования первого аргумента (фиг. 3) содержит счетчик 19, схему 19 сравнения, выход которой является первым выходом блока, и элемент ИЛИ 19,,первый вход которого является первым входом блока. Выход счетчика 19, являющийся вторым выходом блока, соединен с первым входом схемы 192 с Р внения, на второй вход которой поступает код числа N)(.Выход схемы 19 сравнения соединен с вторым входом элемента И ,выход которого соединен с входом синхронизации счетчика 19 . Второй вход блока 19 является счетным входом счетчика 19,, на информационный вход которог поступает код числа 1.

Блок 20 формирования второго аргмента (фиг. 4) содержит счетчик 20. , первую 202 и вторую 20, схемы сравнения, элемент И 20. и два элемента ИЛИ 20J. и 20(j. Выход счетчика 20, являющийся вторым выходом блока 20, соединен с первым входом второй схемы 20 сравнения, на второй вход которой поступает код числа Njf. Первый вход блока 20 является первым входом элемента ИЛИ 20 выход которого соединен с входом синхронизации счетчика 20 . Счетньй вход счетчика 20 является вторым, а его информационней вход - пятым входом блока 20. Третий вход блока 20 является вторым входом элемента

68968

ИЛИ 206 и первым входом элемента И 20, второй вход которого соединен с выходом первой схемы 20 сравнения, а выход - с первым вхос дом элемента ИЛИ 20у, второй вход которого подключен к выходу второй схемы 20 сравнения. Четвертый вход блока 20 является первым входом первой схемы 202 сравнения, на второй вход которой поступает код числа NJ..

Блок 21 формирования третьего аргумента (фиг.5) содержит счетчик 21, первую схему 21 сравнения, первый 21з и второй 21 мультиплексоры, вторую 215- и третью 21, схемы сравнения, элемент И 21- и два элемента ИЛИ 21 g и 21 э . Выход счетчика 21.,, являющийся вторым выходом блока 21,

Q соединен с первым входом третьей схемы 21( сравнения, на второй вход ко-, торой поступает код числа N. Первый вход блока 21 является первым входом элемента ИЛИ 21 , выход которого соединен с входом синхронизации счетчика 21 , счетный вход которого является вторым входом блока 21 . Второй вход элемента ИЛИ 21д, управляющий вход второго мультиплексора 2 Ц и первый вход элемента И 21., образуют третий вход блока 21. Четвертый вход блока 21 является первым входом второй схемы 215 сравнения, на второй вход которой поступает код числа Ny. Первый

5 и второй входы первой схемы 2l2 сравнения, являющиеся соответственно пятым и шестым входами блока 21, соединены соответственно с первым и вторым входами первого мультиплексора 21j, управляющий вход которого соединен с выходом первой схемы 21 сравнения. Седьмой вход блока 21 является первым входом второго мультиплексора 21, второй вход которого соединен с выходами первого мультиг плексора 21j, а выход - с информационным входом счетчика 21., .. Выходы второй 21J и третьей 21 схем сравнения соединены с вторыми входами

0 соответственно элементов И 21 и ИЛИ 21 , причем выход элемента И 27., соединен с первым входом элемента ИЛИ 21g ..

Блок 43 выбора аргументов (фиг.6)

5 содержит первый 43 и второй 43, мультиплексоры схему 43j сравнения, элемент И 43 и инвертор 43j. Информационные входы второго мультиi9

плексора 43, являются первым и вторым входами блока 43. Выход второго .мультиплексора 432 соединен с первым входом элемента И 43. , второй вход которого соединен с выходом схемы 43J сравнения. Выход элемента И 43 соединен с входом инвертора 43.и является прямым выходом блока 43,инверсный выход которого является выходом инвертора 43.Управляющие входы мультиплексоров 43 и 43 являются третьим и четвертым входами блока 43.

Устройство работает следующим образом.

По сигналу Пуск в счетчик 19 блока 19 формирования первого аргумента записывается код 1 и первый триггер 26 блока управления срабатывается в О.Уровень логической 1,, являющийся при этом на первом выходе 45 блока 25 управления, поступает на управляющий вход первого мультиплексора 13 и разрешает прохождение Ny случайных чисел S. , ,. . . ,N с датчика 9 на адресный вход постоянного запоминающего устройства 12.В результате этого, в блок 1 обратного ДПФ из постоянного запоминающего устройства 12, содержащего массив комплексных чисел W(i) jx

j-- i, i 0,..., M-1 , случайным образом считываются NX комплексных коэффициентов X .,(k) ; ДПФ воздействия, равных W(S,), ,..., Nj..Одновременно с этим осуществляется запись N X случайных чисел S 1| во второй блок 10 памяти.После выполнения операции обратного ДПФ в блоке 1 над массивом X,(k) в первый блок 2 буферной памяти записьшается реализация yi(i) ,,. ..,10.-} псевдослучайного процесса x(i). Для формирования достаточно длительного воздействия на исследуемый объект 4 реализации X. (i) циклически считывается из первого блока 2 буферной памяти и преобразуется с помощью ЦАП 3 в аналоговую форму. По истечении переходных процессов в исследуемом объекте 4 (для чего, обычно, бывает достаточно 5 -7 циклических повторений реализации х (i) во второй блок 6 буферной памяти записывается дискретизированная с помощью АЦП 5 реализация y(i), ,...,m-1 реакции исследуемого объекта 4. Затем блоком 7 прямого ДПФ осуществляется вычисле

6896 0

ние коэффициентов Y (k) , ,... ,N, ДПФ записанной в блоке 6 реализации

y./i).

В процессе вычисления оценок ядер 5 Винера аналогичный эксперимент проводится L раз. При этом обработка экспериментальных данных Yg(k), полученных в цикле, осуществляется одновременно с выполнением очеред0 кого ( -D-ro цикла эксперимента. Сигналом, определяющим завершение f-ro цикла обработки экспериментальных данных и начало очередного (.1 f1)-ro цикла, является появление логической 1 на первом выходе 45 блока

25управления (на первбм цикле данный сигнал вызьшается командой Пуск) По данному сигналу одновременно .осуществляется: приращение содержимого

0 счетчика 35 циклов на единицу,переЛ

пись массива случайных чисел S ,сгенерированных на 6-ом цикле,из второ-го блока 10 памятТ в третий блок 11 памяти, передача коэффициентов

5 Yg(k) ДПФ реакции исследуемого объекта 4, полученных на -м цикле, из блока 7 прямого ДПФ в первый блок 8 памяти, генерирование очередного массива случайных чисел S , заQ пись их во второй блок 10 памяти . и передача коэффициентов X g+ (k) ДПФ воздействия, находящихся в постоянном запоминающем устройстве .12, по случайным адресам S / в блок 1 обратного ДПФ.После выполнения данных операций сигналов с выхода элемента 39 задержки первый триггер

26блока 25 управления устанавливается в единичное состояние, запускается распределитель 34 импульсов

и одновременно с выполнением (1 +1)го эксперим.ента начинается Е-й цикл вычисления оценок ядер Бинера на основе данных, полученных в результате 1-го эксперимента и находящихся в первом 8 и третьем 11 блоках памяти.

Каждый цикл вычисления оценок ядер Бинера осуществляется путем сканирования областей Н.,Н ,Н-, изменения аргументов ядер в соответствии с рассмотренными ранее принципами. Сканирование начинается с и продолжается до тех пор, пока не будут исчерпаны все точки (К,,..., к) областей Н, ,2,3.Пусть текущее состояние устройства характеризуется наличием логичвЛсой 1 на выходе п-го разряда (п 3) ре11

гистра 38 сдвига, что означает формирование оценки ядра Винера п-го порядка в некоторой точке (К ,..., :Кр), Предположим, что текущая точка (к,...,К|) е н .Б

этом случае на первом выходе блока формирования п-го аргумента будет присутствовать уровень логического О. В связи с этим независимо от состояния п-го триггера с выхода элемента ИЛИ 42 блока 25 управления на управляющий вход распределителя 33 импульсов будет поступать уровень логического О и очередной импульс синхронизации с первого выхода распределителя 33 импульсов череэ п-й элемент И 29 первой групп пройдет на п-й вход элемента ИЛИ 18 и п-й управляющий вход второго мультиплексора 24. В результате чего, код счетчика 172 1ДРбса блока 17 усреднения, определяющий порядковый номер текущей точки (К,..., 1) «увеличится на единицу, а на выходе второго мультиплексора 24 зафиксируется информация, поступающая на п-ую группу его входов. При этом на адресный вход первого блока 8 памяти притупит код суммы 6п К ... , на адресный вход третьего блока 11 памяти - код аргумента К„, а на управляющий вход сумматора 14 по модулю М - код выполняемой операции.В зависимости от кода операции сумматор 14 по модулю М осуществляет сложение числа s ,поступающего из К-й ячейки третьего блока 11 памяти, с частичной суммой S + , .. , взятой со знаком плюс (код 1) или .минус (код 0) из (n-l)-ro регистра блока 15 регистров. Адресация рабочих регистров блока 15, участвующих в операции сложения по модулю М, осуществляется кодом сигналов, поступающих на группу управляющих входов блока 15 регистров с второй группы выходов блока 25 управления Результат операции записывается в п-й регистр блока 15 и поступает на адресньй вход постоянного заломинающегй, устройства, с выхода которого на первый вход умножителя . 16 поступает код числа W (8ц +. ..+S) ,На второй вход умножитля 16 поступает код числа Y (Ц +... +kn) из (Kд.. .+К)-ой ячейки блока 8 памяти. Результат .операции умножения, складывается в сумматоре I усреднения с содер9689612

жимым ячейки блока 17 памяти ядер,адресуемой счетчиком 17..

Одновременно с вычислением оценки ядра в точке (К,...,К ) устройство формирует очередную точку области изменения аргументов. При этом импульсный сигнал с первого выхода распределителя 34 импульсов ,задержанный на втором элементе 40 задержки, пос--. тупает на первый вход регистра 33

10 сдвига, обеспечивая сдвиг логической 1 на один разряд вправо (из п-го в (п + 1)-ый разряд.

Рассмотрим два возможных случая. Если , то в результате сдвига на выходе элемента И 42 появится

уровень логической 1, который поступит на второй управляющий вход распределителя 34 импульсов,В результате этого, очередной импульс син20

хросерии с второго выхода распределителя 34 импульсов через элемент И 44 пройдет на второй вход регистра 33 сдвига и осуществит сдвиг влево на один разряд. Задержанный на время

сдвига третьим элементом 41 задержки данный импульс через третий элемент И 30 второй группы поступит на третий вход блока 21 формирования третьего элемента ,являющийся счетным входом

счетчика 21, и обеспечит приращение аргумента Кз на единицу.

Таким образом, вслед за точкой (К,К, Kj ) устройство сформирует точку (K.Kj, К5). В случае п 3 импульсный сигнал с первого выхода распределителя 34 импульсов через п-й элемент И первой группы поступит на первый вход блока формирования (п -f 1)-го аргумента и первый вход (п 1)-го триггера блока 25 управле-НИН, устанавливая его в единичное состояние. В результате чего, в счетчик блока фop fиpoвaния (п 1) -го аргумента заносится код аргумента К и формируется начальное значение аргумента К, Таким образом, вслед за точкой К или формируется точка (К,К), а вслед за точкой (К, К) - i: точка (К, Kj, К).

Дальнейшее функционирование устройства зависит от того, принадлежит или не принадлежит вновь сфсф- . лнрованная. точка (К,,...,К) множеству н - , порождаемому элементом (К,...,К). Проверка

принадлежности (К,,...,К) MHoxect11 К , ... , к ft.i

осуществляется

ву

п

3 1

блоком формирования п-го аргумента, причем в зависимости от состояния п-го триггера блока 25 управле.ния проверяется условие (К,..- К. , К) (единичное состояние) или условие (-К,,, ,

., -К, к) е-н (нулевое состояние). Пусть п-й триггер блока 25 управления находится в единичном состоянии.Тогда, в случае (К,... ,К)е- (уровень логического О с первого /выхода блока формирования п-го аргумента через элементы И 32 31 и ИЛИ 42 проходит на второй управляющий вход распределителя 34 импульсов и очередной импульс синхросерии поступит на его первый выход. По данному импульсу в устройстве начинает выполняться ранее рассмотренная последовательность действия, связанная с вычислением оценки ядра в точке (К,.. . ,К,) . В случае (К.... ,К) е выходе блока формирования п-го аргумента появится уровень логической 1, что приведет к установке п-го триггера в нулевое состояние. При это означает завершение сканирования областей Н,Н , Ilj изменения аргументов Адер, что приведет к появлению на первом выходе 45 блока 25 управления уровня логической 1 и началу очередного цикла работы устройства. При ,3 это приведет к занесению в счетчик блока формирования п-го аргумента кода начального значения аргумента К , равного аргументу К, если , или макс(-К, К + Kj), если . В этом случае, когда п-й триггер находится в нулевом состоянии, в блоке формирования п-го аргумента осуществляется проверка условия

(-к, ,....-к„ К,) е-н 1--- п- .

При этом, если данное условие выполняется, уровень логического О с первого выхода блока формирования п-го аргумента через элементы И .32п-1 и 31р пройдет на (п-1)-й вход элемента ИЛИ 42. Если текущая комбинация (-К „. ,... ,-К -,, Kj) не содержит аргументов, равных по абсолютной величине и противопоожных по знаку (т.е. не является запрещенной) с прямого выхода блока 3 сравнения аргументов на третий ход И 42 также поступает уровень огического О, что приведет к воч9689614

никновению логического О на втором управляющем входе распределителя 34 импульсов, В результате этого очередной импульс синхросерии, поступающий на вход распределителя 34 импульсов, пройдет на его первый выход и через элемент И 29 поступит на п-й выход 46 блока 25 управления. По данному импульсу в устройстве наfg чинает выполняться ранее рассмотренная последовательность действий,связанная с вычислением оценки ядра в точке (-К . ,. . .. ,-К ,К) .Если же текущая комбинация (-К. ,...,-К,

5 является запрещенной .уровень логической 1 с прямого выхода блока 43 сравнения аргументов через элемент ИЛИ 42 поступит на второй уп- . равляющий вход распределителя 34

,„ импульсов и очередной импульс синхрЬсерии пройдет на его второй выход. Так как уровень логического О поступающий с инверсного выхода блока 43 выбора аргументов, закроет

jc элемент И 44, данный импульс не пройдет на второй вход регистра 33 сдвига и операции сдвига в регистре не произойдет. С выхода третьего элемента 41 задержки синхроимпульс .через элемент И 30 поступит на третий вход блока формирования п-го аргумента, что приведет к увеличению аргумента К на единицу и формированию очередной точки (-К,. ..,

1 П4Ч

Рассмотрим случай, когда (-К ,, , ...,-К, KJ -Н - .В этом случае на первом выходе блока формирования п-го аргумента появится уровень логической l, который через элементы И 32 „. ,31 и ИЛИ 42 пройдет на второй управляющий вход распределителя 34 импульсов. Это приведет к тому, что очередной импульс

синхросерии поступит на второй вход регистра 33 сдвига и выполнит сдвиг влево на один разряд. Кроме того, данный импульс через третий элемент 41 задержки и элемент И 30„. поступит на третий вход блока формирования Сп-1)-го аргумента, что приведет к увеличению аргумента К , на единицу. В результате этого, при будет сформирована очередная

5 точка ,a при - точка (К , К 2 1) , если второй тригер 27 блока 25 управления находится в единичном состоянии, или точка (-К, К + 1),

15

если второй триггер 27 находится в нулевом состоянии.

Аналогичным образом устройство функционирует до тех пор, пока не будут вычислены оценки ядер во всех точках областей Н, H,j и Hj изменения их аргументов. Сигналом, определяющим окончание сканирования,.является появление уровня логической 1 на выходе схемы 19 сравнения блока 19 формирования первого аргумента. Это приведет к занесению в счетчик 19х, блока 19. начального значения . 1 и установке первого триггера 26 блока 25 управления в нулевое состояние. При этом на первом выходе 45 блока 25 управления появится уровень, логической 1, означающий окончание 1-го цикла ра9689616

боты устройства и начало очередного (i + 1)-го цикла. Если Е L,то после завершения операции генерирования очередного набора случайных чисел

5 датчиком 9 сигнал с выхода первого элемента 39 задержки, поступающий через элемент И 37 на первый вход первого триггера 26, устанавливает -его в единичное состояние. В результате чего, запускается распределитель 34 импульсов и начинается (1 + + 1.)-й. цикл вычисления оценок ядер Винера. Если I превысит предельное значение Ь,то на выходе дешифратора

15 36 появляется уровень логического О, который закрывает элемент И 37, очередного взвода первого триггера 26 не происходит и устройство завершает работу.

К,Кг-К,

(Риг. 5

Ki

43з

J/

4Л

Кз .

Фи.б

| Устройство для определения ядер нелинейных объектов | 1981 |

|

SU1008747A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Мармарелис П.,Мармарелис В, Анализ физиологических систем.Метод белого шума.М.: Мир, 1981. | |||

Авторы

Даты

1985-12-07—Публикация

1984-04-18—Подача