(5) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОЛИЧЕСТВА ЕДИНИЦ В ДВОИЧНОМ ЧИСЛЕ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля параллельного двоичного кода на четность | 1981 |

|

SU999057A1 |

| Преобразователь двоичного кода в число-импульсный код | 1980 |

|

SU943704A1 |

| Программное устройство для фиксации и документирования времени | 1989 |

|

SU1677691A1 |

| Устройство для сортировки чисел | 1989 |

|

SU1793438A1 |

| Пороговое устройство (его варианты) | 1984 |

|

SU1352449A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1056199A1 |

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587641A1 |

| Устройство для контроля двоичного кода по модулю К | 1990 |

|

SU1737736A1 |

| Устройство для сортировки двоичных чисел | 1986 |

|

SU1325462A1 |

| Устройство для определения количества единиц в двоичном числе | 1983 |

|

SU1171780A1 |

. 1

Изобретение относится к вычислительной технике и может быть испольг зовано в качестве устройства контроля цифровой техники.

Известно устройство определения количества единиц, обеспечивающее счет совпадающих по времени входных импульсов, содержащее генератор тактовых импульсов, сметчик Джонсона, двоичный счетчик, фиксирующие триггеры, элементы НЕ-И и инверторь Cl .

Недостатком данного устройства, счетчика является невысокое быстродействие, обусловленное необходимостью опроса всех фиксирующих триггеров..

Наиболее близким техническим решением к изобретению является уст- ройство для определения количества единиц в двоичном числе, содержащее трехвходовой элемент И, элемент И-НЕ, выходной элемент И, счетчик и триггер и элементы И и ИЛИ для каулдого из разрядов 2.

Недостатком данного устройства является невысокое быстродействие обусловленное подсчетом прямых сигналов значаи их разрядов двоичного числа. В случае присутствия единиц во всех разрядах д,воичного числа время подсчета их будет максимальным и равным

Z Т(п-1),

10

где t - время подсчета единиц в разрядах двоичного числа; Т - период следования тактовых

I импульсов-, п - число разрядов в двоичном

15

числе.

.Цель изобретени1Ч - увеличение быстродействия устройства.

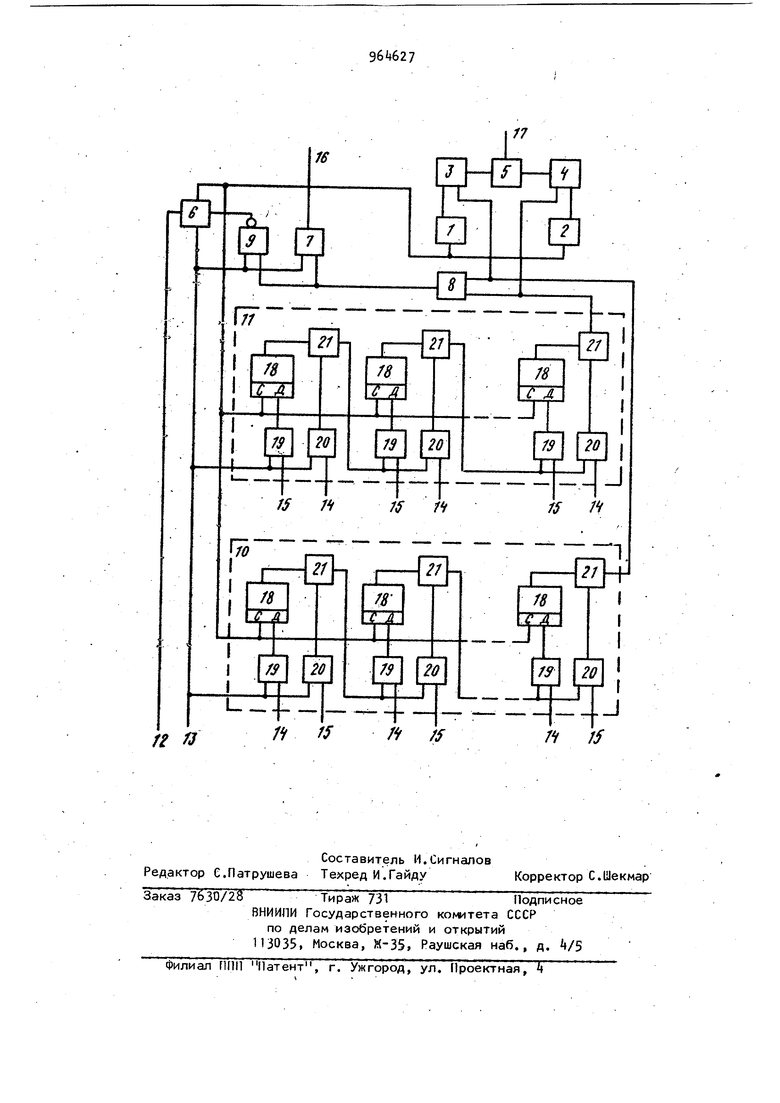

Поставленная цель,достигается тем, что в устройство для определения ко20личества единиц в двоичном числе, содержащее первый счетчик импульсов, первый элемент И, элемент И-НЕ, второй элемент И и канал фиксации единиц 8 прямом коде, состоящий из п триггеров, где п - количество разрядов двоичного числа, 2п элементов И и п элементов ИЛИ, единичныйвыход триггера 4-го разряда, где 1-f , соединен с первым входом соответствующего Г-го элемента ИЛИ, выход которого соединен с первыми входами (21+ +1)-го и (2i+2)-ro элементов И, вторые входы (2i+1)-ro и (2}+2)-го элементов И, где О i i 4 (п-1), соединены соответственно с единичным и нулевым входами i-ro разряда двоичного числа, выходы (2i+1)-ro и (2i+2)-ro элементов И соединены соответственно с D входом триггера i-ro разряда и вторым входом элемента ИЛИ, пер вые входы первого и второгоэлементов И канала фиксации иниц в прямо коде соединены с управляющим входом устройства, с первыми входами первого и второго элементов И и с первым входом элемента И-НЕ, выход -которого соединен со вторым входом первого элемента И, выход первого элемент И соединен со счетным входом первого счетчика, и с-входом синхронизаци всех триггеров канала фиксации единиц в прямом коде, тактовый вход уст ройства соединен с третьим входом первого элемента И, выход второго эл мента И является управляодим выходом устройства, введен второй счетчик, элемент ИЛИ, первая и вторая группы элементов И, группа элементов ИЛИ и канал ф.иксации единиц в.обратном коде, выполненный аналогично каналу фиксации единиц в прямом коде, причем первые входы (2i+1)-ro и (2 +2}элементов И канала фиксации единиц в обратном коде соединены соответстве но с нулевым и единичным входами i-ro разряда двоичного числа, где О 4 i $ П , управляющий вход устройства соединен с первыми в.ходами первого и второго элементов И канала фиксации единиц в обратном коде, выход п-го элемента ИЛИ этого канала соединен с первым входом элемента ИЛИ, выход которого соединен со вторыми входами второго элемента И и элемента И-НЕ,/выход первого элемента И соединен со входом синхронизации триггеров канала фиксации единиц в обратном коде и со счетным входом второго счетчика,информационные выходы первого и второго счетчиков сое динены соответственно с первыми входами соответствующих элементов И 96 4 первой и второй групп, выходы которых соединены соответственно с первыми и вторыми входами элементов ИЛИ группы, выходы элементов ИЛИ группы являются информационными выходами устройства, выход п-го элемента ИЛИ канала фиксации единиц в прямом коде соединен со вторым входом элемента ИЛИ, первые и вторые входы элемента ИЛИ соединен со вторыми входами элементов И соответственно второй и первой Групп.. На чертеже представлена блок-схема устройства для определения количества единиц в двоичном числе. Схема содержит первый счетчик 1, второй счетчик 2, работающий.на первую и вторую группы элементов И З-, группу элементов ИЛИ ij, первый и второй элементы И 6-/, элемент ИЛИ 8, элемент И-НЕ 9, канал 10 фиксации единиц Впрямом коде двоичного числа и канал 11 фиксации единиц в обратном коде двоичного числа, вход 12 тактовых импу.яьсов, управляющий вход 13 устройства, входы 1ч, 1Ь соответственно прямого и инверсного сигналов -го разряда двоичного числа, управляющий выход 16 и информационный выход 17 устройства. Каналы 10 и 11 фиксации единиц в прямом коде двоичного числа и в обратном коде двоичного числа содержит триггеры 18, элементы И 19-20 и элементы ИЛИ 21. Входы счетчика 1 и вычитающего счетчика.2 соединены с выходом элемен та И 6 и с синхронизирующими входами каналов фиксации единиц в прямом коде двоичного числа 10 и в обратном коде двоичного числа 11, которые сое- динены с синхронизирующими входами триггеров 18, а выходы - с первыми входами группы элементов И З-, выходы которых соединены через группу элементов ИЛИ 5 с выходом 17 устройства, а вторые входы - с входами Элемента ИЛИ 8 и с выходами элементов ИЛИ 21 последнего разряда каналов 10 и 11. Первый вход элемента И 6 соединен с Управляю1цим входом 13 устройства, с первыми входами элемента И 7, элемента И-НЕ 9 и элементов И 19-20 каналов 10-11, второй вход соединен с выходом элемента И-НЕ 9, а третий вход - с входом 12 тактовых импульсов устройства, второй вход элемента И-НЕ 9 соединен с выхорм элемента ИЛИ 8 и со вторым входом элемента И 7, выход которого является управляющим выходом 16 устройства.

Информационные входы триггеров 18 соединены с выходами элементов И 19, а единичные выходы - с первыми входами элементов ИЛИ 21, вторые входы которых соединены с выходами элементов И 20, а выходы - с первыми входами элементов И 13-20 последующих разрядов. Вторые входы элементов И 19-20 канала 10 фиксации единиц в прямом коде двоичного числа соединены с входами прямого и инверсного сигналов разрядов двоичного числа соответственно. Вторые входы элементов И 19-20 канала 11 фиксации единиц в обратном коде .двоичного числа соединены с входами 15-1 инверсного и прямого разрядов двоичного числа соответственно.

Устройство работает следующим образом.

В исходном состоянии триггеры 18, счетчик 1 находятся в нулевом состоянии, а счетчик 2 - в состоянии, кодовая комбинация разрядов которого соответствует максимально возможному количеству единиц в двоичном числе. На входы 14-15 подаются прямой и -инверсный сигналы от соответствующих разрядов двоичного числа.

При поступлении на вход 13 устройства управляющего сигнала происходит подготовка триггера 18 яервого разряда канала фиксации единиц в прямом коде двоичного числа К) к переходу в единичное состояние (через элемент И 19), если на входе Ш единичный сигнал либо передача управляющего сигнала на элементы И 19-20 второго разряда (через элемент ИЛИ 21 если единичный сигнал на входе 15), и аналогично подготовка триггера 18 первого разряда канала фиксации единиц в обратном коде двоичного числа 11 к переходу в единичное состояние (через элемент ИЛИ 19, если на входе 15 единичный сигнал), либо передача yпpaвляюl eгo сигнала на элементы И второго разряда (через элемент ИЛИ 21, если .единичный сигнал на входе }k}.

Распространение управляю1цего сигнала прекратится на разряде, имеющем на входе единичный сигнал для триггера 18 канала фиксации единиц, в прямом коде двоичного числа 10, и на разряде, имеющем на входе 15 единичный сигнал для триггера 18 канала фиксации единиц в о()ратном коде двоичного числа 11, причем триггеры 18 этих разрядов подготовлены к

ТОМУ, чтобы сигналу на синхронизирующем входе переключиться в единичное состояние.

При поступлении тактового импульса на вход 12 устройства трехвходовой элемент И 6 выдает сигнал и триггеры 18, подготовленные к переключению, переходят в единичное состояние, что вызывает дальнейшее распространение управляющего сигнала до

того разряда, на входе k которого имеется единичный сигнал для триггера 18 канала фиксации единиц в прямом коде двоичного числа 10, и на входе 15 - для триггера 18 канала фиксации

единиц - в обратном коде двоичного числа 11.

Указанный процесс продолжается до тех пор, пока на выходе элемента ИЛИ 21 последнего разряда канала фиксации единиц в прямом коде двоичного числа 10 или элемента ИЛИ 21 последнего разряда канала фиксации единиц в обратном коде двоичного числа 11 не появится сигнал, который через ;

элемент ИЛИ 8 и элемент И 7 поступит на управляющий выход 16 устройства, что озна.чает возможность чтения состояния счетчика 1 или вычитающего счетчика 2.

Выбор счетчика, содержимое которого будет показывать число единиц в двоичном числе, осуществляется сигналом с выхода элементов ИЛИ 21 последнего разряда канала фиксации единиц в прямом коде двоичного числа

10или канала фиксации единиц в обратном коде двоичного числа 11, который появится раньше, причем счетчик

11подсчитывает число единиц в прямом коде двоичного числа, а вычитающий счетчик 2 читает из максимально возможного количества единиц в контролируемом числе единицы в обратном коде .исла, т.-е. вычитает нули

в разрядах прямого кода двоичного числа.

Данное техническое решение по сравнению с иавестным за счет введения вычитаюи;его счетчика, двух групп элементов И, группы элемента ИЛИ, элемента ИЛИ и канала фиксаций единиц в обратном коде двоичного числа позволяет увеличить скорость подсчета количества единиц в двоичном 7 числе. Максимальное время подсчета единиц в двоичном числе уменьшается в два раза и равняется времени подсчета единиц в половине разрядов дво ичного числа. Формула изобретения Устройство для определения количества единиц в двоичном числе, содержащее первый счетчик импульсов, первый элемент И, элемент И-НЕ, второй элемент И и канал фиксации единиц в прямом коде, состоящий из п триггеров, где п - количество разрядов двоичного числа, 2 п элементов И и п элементов ИЛИ, единичный выход триггера i-по разряда, где 1 i п, соединен с первым входом соответствующего i-ro элемента ИЛИ, выход которого соединен с первыми входами (21+1)-го и (2i+2)-ro элементов И, вторые входы (2i+1)-ro и (21+2)-го элементов И, где О i i . (п-1), соединены соответственно с единичным и нулевым входами i-ro разряда двоичного ;ЧИсла, выходы (2 i + +1)- го и (2 i +2)- го элементов И соединены соответственно с D входакм триггера i-ro разряда и вторым входом i-ro элемента ИЛИ, первые входы первого и второго элементов И канала фиксации единиц s прямом коде, соединенные с управляющим входом устройств, с первыми входаж первого и второго элементов И и с первым входом элемента , выход которого соединен со вторым входом первого элемента И, выход первого элемента И соединен со счетным входом первого счетчика и с входом синхронизации всех триггеров канала фиксации единиц в прямом коде, тактовый вход устройства соединен с третьим входом первого элемента И, выход второго элемента И является управляющим выходом устройства, отличаюлякхции вход устройства соединен с

5 первыми входами первого и второго элементов И канала фиксации единиц в обратном коде, выход п-го элемента ИЛИ этого канала соединен с первым входом элемента ИЛИ, выход которого соединен со вторыми входами второго элемента И и-элемента И-НЕ, выход первого элемента И соединен с входом синхронизации триггеров канала фиксации единиц в обратном коде и с счетным входом второго счетчика, информационные выходы первого и второго счетчикор соединены соответственно с первыми входами соответствующих элементов И первой и второй групп, выходы которых соединены соответственно с первыми и вторыми входами элементов ИЛИ группы, выходы элементов ИЛИ группы являются информационными выходами устройства, выход п-го элемента ИЛИ канала фиксации единиц в прямом коде соединен со вторым входом элемента ИЛИ, первые и вторые входы элемента ИЛИ соединены со вторь/ми входами элементов И соответственно второй и первой групп,

Источники информации, принятые во внимание при экспертизе

ff 7160 1, кл, G 06 F 11/10, 15.02.80 {прототип),78щ ее с я тем, что, с целью увеличения его быстродействия, введен второй счетчик, элемент ИЛИ, первая и вторая группы элементов И, группа элементов ИЛИ и канал фиксации единиц в обратном коде, выполненный аналогично каналу фиксации единиц в прямом коде, причем первые входы (2i+1)-ro и (2tt2)-ro элементов И канала фиксации единиц в обратном коде соединены соответственно с нулевым и единичным входами i-ro разряда двоичного числа, где , управ14 //

//

/у //

/f //

Авторы

Даты

1982-10-07—Публикация

1981-03-16—Подача