в I-I

V ч/

/-J7/7ff2

Т- J- L

-л/ 70

(риг.1

н

ISu

24lf.f

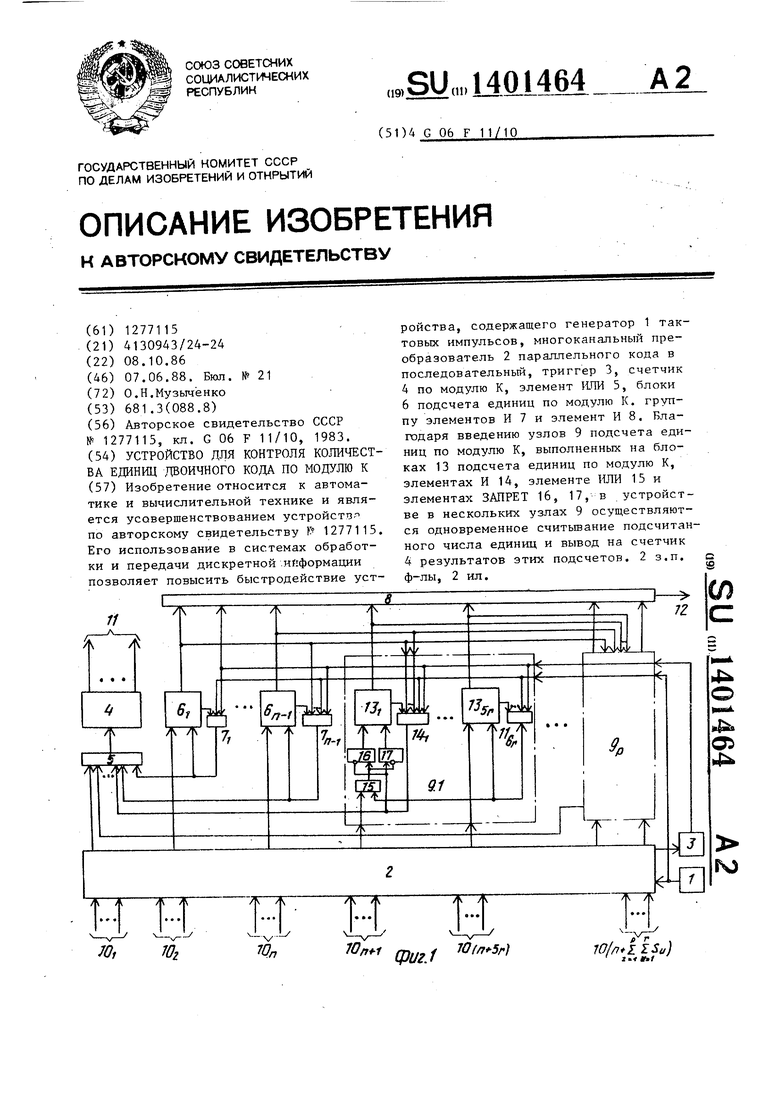

Изобретение относится к автоматике и вычислительной технике, может быть.использовано в системах обработки и передачи дискретной информации и является усоверпенствованием уст - ройства по авт. св. № 1277115.

Цель изобретения - повышение быстродействия устройства.

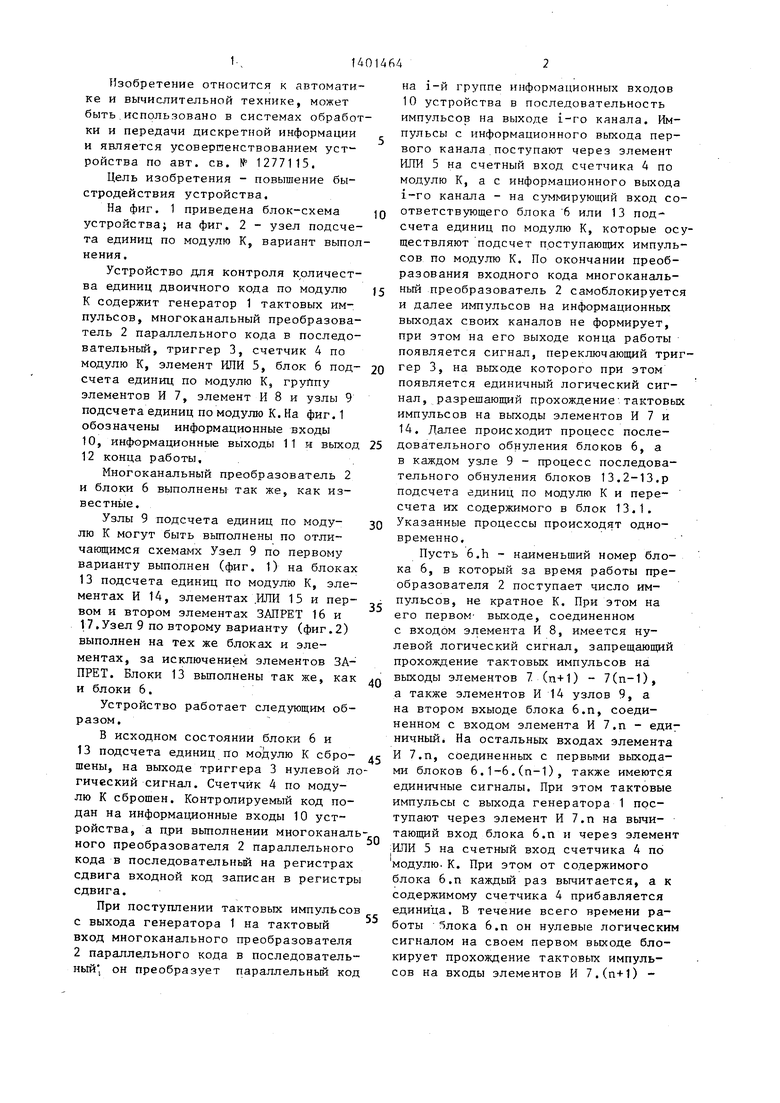

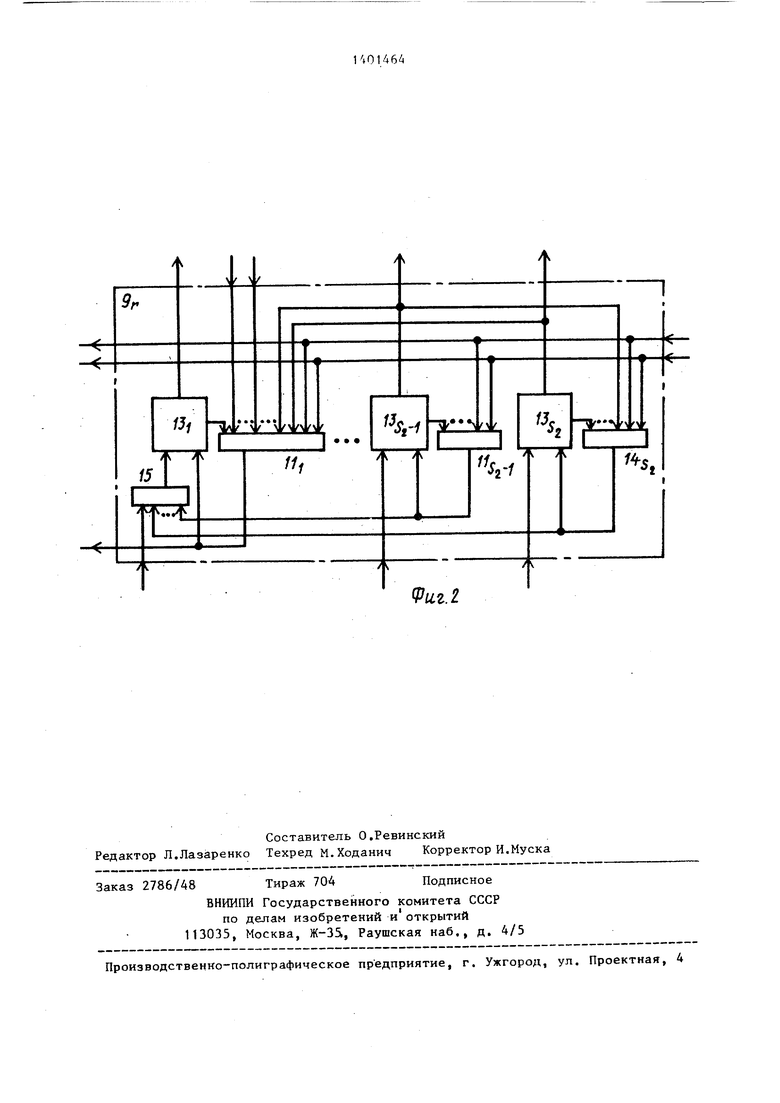

На фиг. 1 приведена блок-схема устройства; на фиг. 2 - узел подсчета единиц по модулю К, вариант выполнения.

Устройство для контроля крличест- ва единиц двоичного кода по модулю К содержит генератор 1 тактовых импульсов, многоканальный преобразователь 2 параллельного кода в последовательный, триггер 3, счетчик 4 по модулю К, элемент ИЛИ 5, блок 6 под- счета единиц по модулю К, группу элементов И 7, элемент И 8 и узлы 9 подсчета единиц по модулю К. На фиг. 1 обозначены информационные входы 10, информационные выходы 11 н выход

12конца работы. Многоканальный преобразователь 2

и блоки 6 выполнены так же, как известные.

Узлы 9 подсчета единиц по моду- лю К могут быть выполнены по отличающимся схемамх Узел 9 по первому варианту выполнен (фиг. 1) на блоках

13подсчета единиц по модулю К, элементах И 14, элементах .ИЛИ 15 и первом и втором элементах ЗАПРЕТ 16 и 17. Узел 9 по второму варианту (фиг. 2) выполнен на тех же блоках и элементах, за исключением элементов ЗАПРЕТ. Блоки 13 вьтолнены так же, как и блоки 6.

Устройство работает следующим образом.

В исходном состоянии блоки 6 и 13 подсчета единиц по модулю К сброшены, на выходе триггера 3 нулевой лгический сигнал. Счетчик 4 по модулю К сброшен. Контролируемый код подан на информационные входы 10 устройства, а при вьтолнении многоканап ного преобразователя 2 параллельного кода в последовательньй на регистрах сдвига входной код записан в регистр сдвига.

При поступлении тактовых импульсо с выхода генератора 1 на тактовый вход многоканального преобразователя 2 параллельного кода в последовательный он преобразует параллельный ко

g

5 0 5

о

5

0

5

0

5

на i-й группе информационных входов 10 устройства в последовательность импульсов на выходе i-ro канала. Импульсы с информационного выхода первого канала поступают через элемент ИЛИ 5 на счетный вход счетчика 4 по модулю К, а с информационного выхода i-ro канала - на суммирующий вход соответствующего блока 6 или 13 под- счета единиц по модулю К, которые осуществляют подсчет поступающих импульсов по модулю к. По окончании преобразования входного кода многоканальный преобразователь 2 самоблокируется и далее импульсов на информационных выходах своих каналов не формирует, при этом на его выходе конца работы появляется сигнал, переключающий триггер 3, на выходе которого при этом появляется единичный логический сигнал, разрешающий прохождение тактовых импульсов на выходы элементов И 7 и 14. Далее происходит процесс последовательного обнуления блоков 6, а в каждом узле 9 - процесс последовательного обнуления блоков 13.2-13.р подсчета единиц по модулю К и пересчета их содержимого в блок 13.1. Указанные процессы происходят одновременно.

Пусть 6.h - наименьший номер блока 6, в который за время работы преобразователя 2 поступает число импульсов, не кратное К. При этом на его первом выходе, соединенном с входом элемента И 8, имеется нулевой логический сигнал, запрещающий прохождение тактовых импульсов на выходы элементов 7 (п+1) - 7(п-1), а также элементов И 14 узлов 9, а на втором вхыоде блока б.п, соединенном с входом элемента И 7.п - единичный. На остальных входах элемента И 7.П, соединенных с первыми выходами блоков 6.1-6.(п-1), также имеются единичные сигналы. При этом тактовые импульсы с выхода генератора 1 поступают через элемент И 7.п на вычитающий вход блока б.п и через элемент ;ИЛИ 5 на счетный вход счетчика 4 по модулю.К. При этом от содержимого блока б.п каждый раз вычитается, а к содержимому счетчика 4 прибавляется единица. В течение всего времени работы 5лока б.п он нулевые логическим сигналом на своем первом выходе блокирует прохождение тактовьтх импульсов на входы элементов И 7.() 7.(n- t), a также племеитив И 14.1 узлов 9, После обнуления блока б.п нп его первом выходе появляется единич- .ный логический сигнал, разрешающий прохождение тактовых импульсов на выходы указанных элементов И, а на втором выходе - нулевой логический сигнал, запрещающий их прохождение на выход элемент И 7.п. Далее аналогичным образом обнуляются все остальные блоки 6. Одновременно в каждом узле 9 аналогичным образом происходит обнуление блоков 13.2-13.5 и переза10

15

пись их содержимого в блок 13,1.

Пусть 9.г наименьший номер узла 9, в котором к моменту обнуления блоков 6 имеются необнуленные блоки 13. Если необнулен только блок 13.1 (процесс обнуления блоков 13.2-13.5 в 20 данном узле 9 закончен), то на всех входах элемента И 14.1 единичные логические сигналы и тактовые импульсы с выхода генератора 1 проходят на его выход и через элемент ИЛИ 5 на счетный вход счетчика 4, а также на вычитающий вход блока 13.1. При этом от содержимого блока 13.1 каждый раз вычитается, а к содержимому счетчипроцесс последовательного обнуления блоков 6 и одновременно процесс пос ледовательного обнуления в каждом уз ле 9 блоков 13.2-13.р. После обнуления всех блоков 6 ос-,пцествляется последовательное обнуление блоков 13.1 узлов 9. Однако в отличие от узлов 9 по фиг. 2, в случае, когда все блоки 6 обнулены, а в узле 9.г не завершился процесс обнуления блоков 13.2-13.Р, работа устройства происходит след .тощим. образом. Обнуление блоков 13.2-13.Р продолжается, при этом импульсы с выходов соответствующих элементов И 14 поступают через элемент ИЛИ 15 на разрешающий вход элемента ЗАПРЕТ 16 и на запрещающий вход элемента 17. Одновременно оказывается разрешено прохождение та товых импульсов на выход элемента И 14.1, которые поступают на разрешающий вход элемента 17 и на запрещающий вход элемента 16 и через элемент 25 ИЛИ 5 на счетный вход счетчика 4.

Таким образом, тактовые импульсы проходят на оба входа блока 13.1, который в этом случае не изменяет своего

состояния. Работа продолжается таким ка 4 прибавляется единица. Работа про-30 образом до обнуления блоков 13,2- должается таким образом до обнуления 13.S, после чего поступление такто- блока 13.1. Если в узле 9.г процесс обнуления блоков 13 не окончен к моменту обнуления блоков 6, то он продолжается до завершения, при этом тактовые импульсы на входы элемента ИЛИ 5 не поступают. Далее аналогичным образом обнуляются блоки 13.1 остальных узлов 9.

вых импульсов через элемент ИЛИ 15 на суммирующий вход блока 13.1 прекра щается и происходит его обнуление так 3g товыми импульсами, проходящими через элемент И 14.1 и элемент ЗАПРЕТ 17. на его вычитающий вход.

После обнуления всех блоков 6 и 13 подсчета единиц по модулю К на

5

0

процесс последовательного обнуления блоков 6 и одновременно процесс пос ледовательного обнуления в каждом узле 9 блоков 13.2-13.р. После обнуления всех блоков 6 ос-,пцествляется последовательное обнуление блоков 13.1 узлов 9. Однако в отличие от узлов 9 по фиг. 2, в случае, когда все блоки 6 обнулены, а в узле 9.г не завершился процесс обнуления блоков 13.2-13.Р, работа устройства происходит след .тощим. образом. Обнуление блоков 13.2-13.Р продолжается, при этом импульсы с выходов соответствующих элементов И 14 поступают через элемент ИЛИ 15 на разрешающий вход элемента ЗАПРЕТ 16 и на запрещающий вход элемента 17. Одновременно оказывается разрешено прохождение тактовых импульсов на выход элемента И 14.1, которые поступают на разрешающий вход элемента 17 и на запрещающий вход элемента 16 и через элемент 5 ИЛИ 5 на счетный вход счетчика 4.

Таким образом, тактовые импульсы проходят на оба входа блока 13.1, который в этом случае не изменяет своего

состояния. Работа продолжается таким образом до обнуления блоков 13,2- 13.S, после чего поступление такто-

вых импульсов через элемент ИЛИ 15 на суммирующий вход блока 13.1 прекращается и происходит его обнуление так- товыми импульсами, проходящими через элемент И 14.1 и элемент ЗАПРЕТ 17. на его вычитающий вход.

После обнуления всех блоков 6 и 13 подсчета единиц по модулю К на

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для подсчета числа единиц двоичного кода по модулю К | 1986 |

|

SU1438006A1 |

| Устройство для подсчета числа единиц двоичного кода по модулю К | 1986 |

|

SU1427574A1 |

| Устройство для преобразования двоичного кода в код по модулю К | 1987 |

|

SU1492479A1 |

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587641A1 |

| Устройство для контроля двоичного кода по модулю К | 1990 |

|

SU1737736A1 |

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587642A1 |

| Устройство для выделения посылок сигналов | 1984 |

|

SU1338090A1 |

| Устройство для контроля количества единиц двоичного кода по модулю К | 1986 |

|

SU1401461A1 |

| Распределитель импульсов | 1983 |

|

SU1148022A2 |

| Устройство для определения моментов распределения случайных величин | 1987 |

|

SU1513476A1 |

Изобретение относится к автоматике и вычислительной технике и является усовершенствованием устройстпя по авторскому свидетельству Р 1277115. Его использование в системах обработки и передачи дискретной .информации позволяет повысить быстродействие устройства, содержащего генератор 1 тактовых импульсов, многоканальный преобразователь 2 параллельного кода в последовательный, триггер 3, счетчик 4 по модулю К, элемент НИИ 5, блоки 6 подсчета единиц по модулю К. группу элементов И 7 и элемент И 8. Благодаря введению узлов 9 подсчета единиц по модулю К, выполненных на блоках 13 подсчета единиц по модулю К, элементах И 14, элементе ИЛИ 15 и элементах ЗАПРЕТ 16, 17, в устройстве в нескольких узлах 9 осуществляются одновременное считьшание подсчитанного числа единиц и вывод на счетчик 4 результатов этих подсчетов. 2 ф-лы, 2 ил. 3. п. Q s

При обнулении всех блоков 6 и 13 40 выходе элемента И 8 появляется едина всех входах элемента И 8 оказыва- яичный логический сигнал, свидетель- ются единичные логические сигналы, что вызывает на выходе 12 единичньй

ствующий об окончании цикла работы устройства.

логический сигнал, свидетельствующий

об окончании цикла работы устройства, д ройство обеспечивает повышение быстроРезультат снимается с выходов счетчика 4 по модулю К на выходы 11 устройства.

Описание работы относится к случаю, когда узел 9 выполнен по схеме фиг. 2. gQ При выполнении узлов 9 по схеме фиг.1 работа происходит сл.едующим образом.

Сначала преобразователь 2 преобразует входной код в последовательности импульсов на информационных ее выходах каналов. Эти импульсы подсчитываются по модулю К счетчиком 4 и блоками 6 и 13. После завершения ра- оты преобразователя 2 происходит

выходе элемента И 8 появляется едияичный логический сигнал, свидетель-

ствующий об окончании цикла работы устройства.

Таким образом, предлагаемое устройство обеспечивает повышение быстр

действия за счет параллельного подсчета единиц по модулю К в группах разрядов входного кода и одновременный вьшод результата на отдельный счетчик, а затем на выходной счетчик.

Формула изобретения

ход W-ro блока подсчета единиц по модулю К соединен с (W-s-l )-м входом W-ro элемента И, выход которого подключен к вычитающему входу W-ro блоход W-ro блока подсчета единиц модулю К соединен с (W-s-l )-м входом W-ro элемента И, выход которого ключен к вычитающему входу W-ro

+ 1)-й управляющие входы узлов подсче- 15 ка подсчета единиц по модулю К и

та единиц по модулю К подключены к первым выходам соответственно первого - (п-1)-го блоков подсчета единиц по модулю К, первый 5,-й выходы г- го узла подсчета единиц по модулю К соединены соответственно с (п+1+ Т S „)-м - (,)-M входами злемен та И и ( -- (п+К X1S J-M управляющими входами (г+1)-го - р-го узлов подсчета единиц по модулю К, (З + О-й выход г-го узла подсчета единиц по модулю К соединен с (п+ +г)-м входом элемента ИЛИ,

2, Устройство по п. 1, отличающееся тем, что узел подсчета единиц по модулю К выполнен на первом - (Sp)-M блоках подсчета единиц по модулю К, первом - (8.)-м элементах И, первом и втором элементах ЗАПРЕТ и элементе ИЛИ, первый вход которого к суммирующие входы. второго - (S)-ro блоков подсчета единиц по модулю К являются соответственно первым - (S)-M информационными входами узла, первый и второй входы всех элементов И соответственно объединены и являются первым и вторым управляющими входами узла, третий - (п+1+iZlS,, )-й входы первого элемента И яв ляются одноименными управляющими входами узла, первый выход первого блока подсчета единиц по модулю К является первым выходом узла, первый выход W-ro ( to 2iS) блока подсчета единиц по модулю К под- ключей к (со+1)-м Входам (со+1)-го - (Sj,)-ro элементов И и является ш-м выходом узла, выход первого элемента И подключен к запрещающему входу первого и разрещающему входу второго элементов ЗАПРЕТ и является ()-м

20

25

30

35

40

45

50

55

W-му входу элемента ИЛИ. I

14646

выходом узла, выход элемента И.Ш сое- дине) с разрешающим входом первог-о и запрещаю11р1м входом второго элементов ЗАПРЕТ, выходы которых подключены соответственно к суммирующему и вычитающему входам первого блока подсчета единиц по модулю К, второй выход которого соединен с (п + 2+X1S.,}-м

ход W-ro блока подсчета единиц по модулю К соединен с (W-s-l )-м входом W-ro элемента И, выход которого подключен к вычитающему входу W-ro блока подсчета единиц по модулю К и

0

5

0

5

0

5

0

5

W-му входу элемента ИЛИ. I

иг.г

| Преобразователь двоичного кода в последовательность импульсов | 1983 |

|

SU1277115A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-06-07—Публикация

1986-10-08—Подача