1

I

...

3F

. ч

г; гтп

цгШ ш

Л

L

J

TIL

т

Ш ш

Л

L

J

TIL

(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор частот | 1988 |

|

SU1681374A1 |

| ЦИФРОВОЙ МНОГОКАНАЛЬНЫЙ СИНТЕЗАТОР СЕТКИ ЧАСТОТ | 1995 |

|

RU2108655C1 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2005 |

|

RU2310992C2 |

| Устройство для автоподстройки частоты | 1988 |

|

SU1653159A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 1991 |

|

RU2030092C1 |

| Устройство для передачи многочастотных сигналов | 1989 |

|

SU1700760A1 |

| Синтезатор частот | 1982 |

|

SU1067603A1 |

| Синтезатор частот | 1986 |

|

SU1478328A1 |

| Устройство синхронизации приемника многочастотных сигналов | 1984 |

|

SU1185627A1 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ЗАЩИТЫ ИНФОРМАЦИИ В СЕТЯХ СВЯЗИ | 2005 |

|

RU2295195C1 |

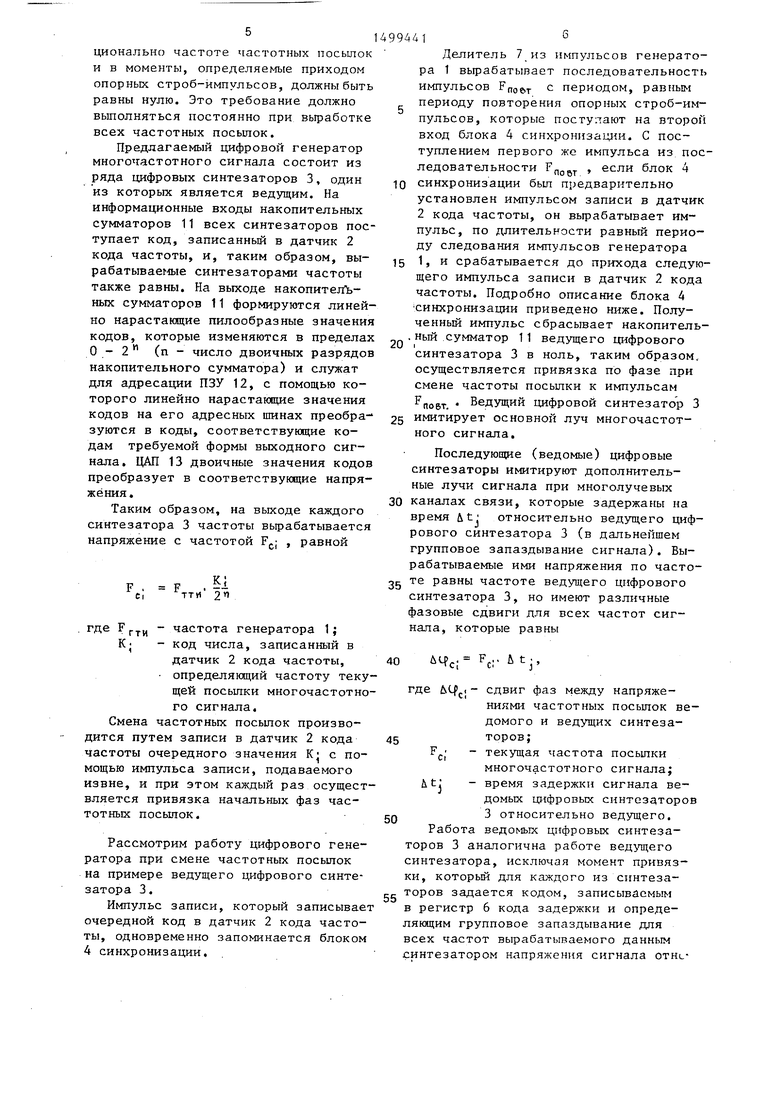

Изобретение может быть использовано для синтеза аналоговых сигналов цифровым методом. Цель изобретения - повышение стабильности работы за счет повышения стабильности фазовой синхронизации формируемых частотных сигналов, которая достигается за счет введения N блоков 4 синхронизации, осуществляющих синхронизацию моментов начала формирования частотных сигналов в N цифровых синтезаторах 3 с моментами появления импульсов на выходе N-1 блоков 5 сравнения, с тактовыми импульсами на выходе генератора 1 тактовых импульсов и с моментом смены кода в датчике 2 кода частоты. С помощью введенных N-1 регистров 6 кодов задержек осуществляется программирование длительностей задержек. Устройство также содержит N аттенюаторов 8, сумматор 9, фильтр 10 нижних частот. 2 ил.

гтп s

4

СО

со

4ib 4

3149944

тотных сигналов, которая достигается за счет введения N блоков 4 синхронизации, осуществляющих синхронизацию моментов начала формирования с частотных сигналов в N цифровых синтезаторах 3 с моментами появления импульсов на выходе N-1блоков 5 сравнения, с тактовыми импульсами на вы

Изобретение относится к радиотехнике может быть использовано для синтеза аналоговых сигналов цифровым мет тодом,в частности в аппаратуре, предназначенной для имитации многочастот-- ных сигналов, .

Целью изобретения является повыше- ние стабильности работы цифрового генератора многочастотного сигнала за счет повышения стабильности фазовой синхронизации формируемых частотных сигналов.

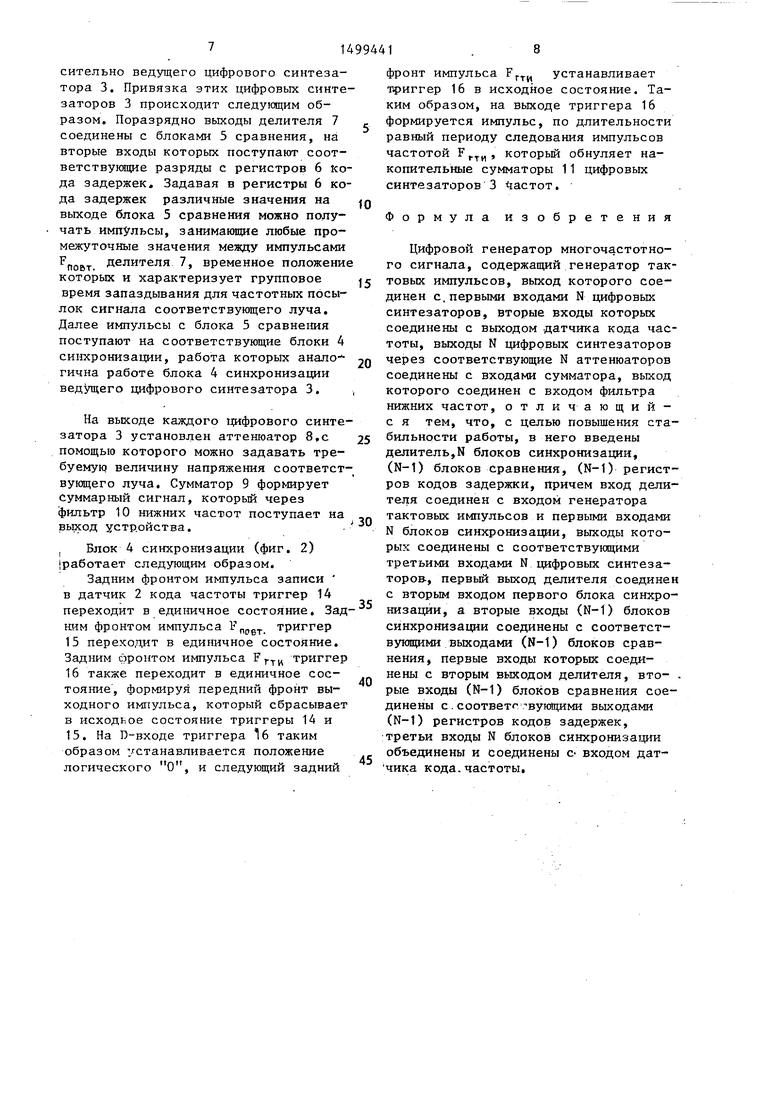

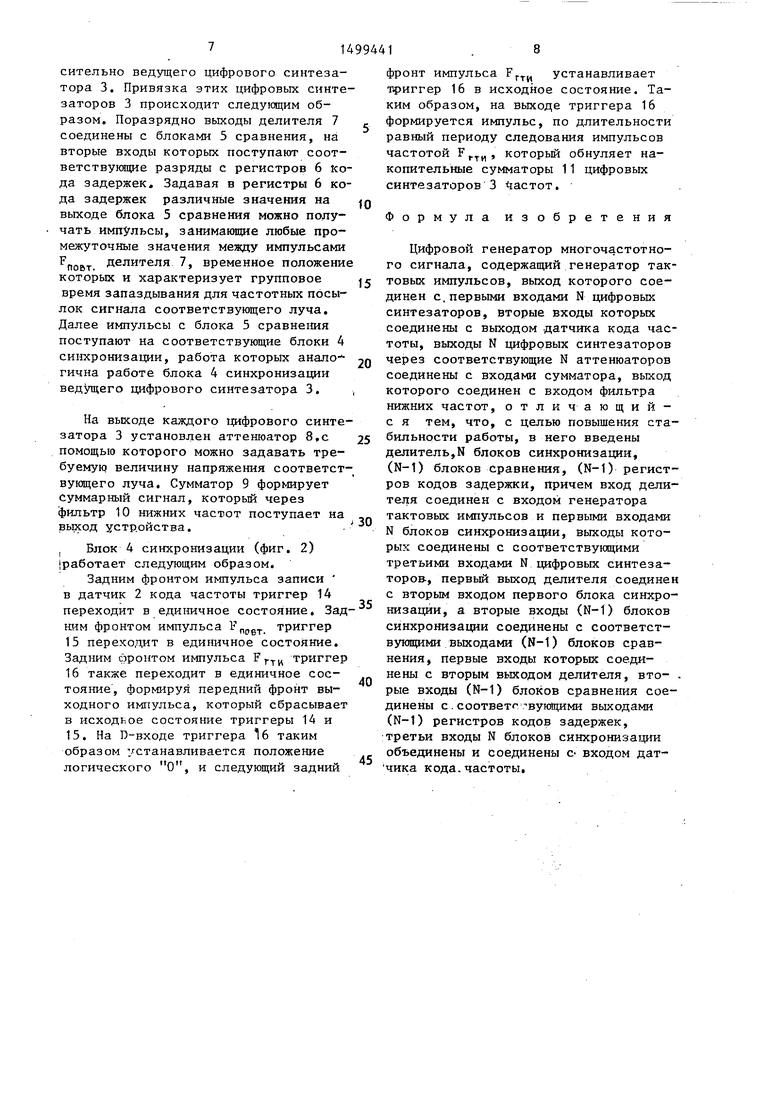

На.фиг. 1 представлена функцио-- нальная схема цифрового генератора многочастотного сигнала; на фиг. 2 - функциональная схема блока синхрони3ации.

Цифровой генератор многочастотного сигнала содержит генератор 1 тактовых импульсов, датчик 2 кода частоты, цифровые синтезаторы 3,

4синхронизации, блоки 5 сравнеютя, регистры 6 кодов задержек, делитель

7, аттенюаторы 8, сумматор 9, фильтр 10 нижних частот (ФНЧ).

Выход генератора 1 тактовых им

пульсов соединен с первыми входами

цифровых синтезаторов 3, блоков 4 синхронизации и входом делителя 7, первьй выход которого соединен с вторым входом первого блока 4 синхронизации. Второй выход делителя 7 сое- динен с первыми входами блоков 5 сравнения, с вторыми входами которых соединены выходы соответствующих регистров 6 кодов задержек. Выходы блоков 5 сравнения соединены с соответствующими вторьши входами блоков 4 синхронизации, третьи входы которых объединены и соединены с входом синхронизации датчика 2 кода частоты, выход которого соединен с вторыми входами цифровых синтезаторов 3, третьи входы которых соединены с соответствующими выходами блоков 4 синхронизации. Выходы цифровых син

ходе генератора 1 тактовых импульсов и с моментом смены кода в датчике 2 кода частоты. С помощью введенных N-1 регистров 6 кодов задержек осуществляется программирование длительностей задержек. Устройство также содержит N аттенюаторов 8, сумматор 9, фильтр 10 нижних частот. 2 ил.

5

5

0

0

5

0

5

тезаторов 3.соединены с соответствую- щими входами сумматора 9, выход которого соединен с фильтром 10 нижних частот. Цифровой синтезатор 3 содержит накопительный сумматор 11, постоянное запоминающее устройство (ПЗУ) 12, цифроаналоговый преобразователь (ДАЛ) 13.

Вход синхронизации накопительного сумматора 11 является первым входом цифрового синтезатора 3, второй вход которого является информационным входом накопительного сумматора 11, вход установки в нуль которого является третьим входом накопительного сумматора 11, выход которого соединен с входом ПЗУ 12, выход которого соединен с ЦДЛ 13, выход которого является выходом цифрового синтезатора 3.

Блок 4 синхронизации (фиг. 2) содержит триггеры 14-16. D-.вход триггера 14 соединен с источ1га ком напряжения логической 1, Прямой выход триггера 14 соединен с D-входом триггера 15, прямой выход которого соединен с D-входом триггера 16, пря-. мой выход триггера 16 соединен с входами предустановки триггеров 14 и 15. Тактовые входы триггеров 16, 15 и 14 являются соответственно первым, вторым и третьим входами блока 4 синхронизации.

Цифровой генератор многочастотного сигнала работает следующим образом.

Формируется многочастотный сигнал, который представляет собой сигнал большой длительности (единицы секунд) , которьй состоит из последовательности частотных посылок (длительностью десятки миллисекунд) несущие частоты которых являются гармо1шк - ми опорных строб-импульсон, следующих с частотой FtioBT. Начальные фазы частотных посыпок изменяются пропор u

ционально частоте частотных посьток и в моменты, определяемые приходом опорных строб-импульсов, должны быть равны нулю. Это требование должно выполняться постоянно при вьфаботке всех частотных посьток.

Предлагаемый цифровой генератор много шстотного сигнала состоит из ряда цифровых синтезаторов 3, один из которых является ведущим. На информационные входы накопительных сумматоров 11 всех синтезаторов поступает код, записанный в датчик 2 кода частоты, и, таким образом, вырабатываемые синтезаторами частоты также равны. На выходе накопительных сумматоров 11 формируются линейно нарастающие пилообразные значения кодов, которые изменяются в пределах 0-2 (п - число двоичных разрядов накопительного сумматора) и служат для адресации ПЗУ 12, с помощью которого линейно нарастаюпще значения кодов на его адресных шинах преобра- зуются в коды, соответствующие кодам требуемой формы выходного сигнала. ЦАП 13 двоичные значения кодов преобразует в соответствующие напряжения.

Таким образом, на выходе каждого синтезатора 3 частоты вырабатывается напряжение с частотой , равной

Ci

F

тти

51 2где , - частота генератора 1; Kj - код числа, записанный в

датчик 2 кода частоты, определяющий частоту текущей посылки многочастотного сигнала.

Смена частотных посыпок производится путем записи в датчик 2 кода частоты очередного значения Kj с помощью импульса записи, подаваемого извне, и при этом каждый раз осуществляется привязка начальных фаз частотных посылок.

Рассмотрим работу цифрового генератора при смене частотных посылок на примере ведущего цифрового синтезатора 3.

Импульс записи, который записывает очередной код в датчик 2 кода частоты, одновременно запоминается блоком 4 синхронизации.

994Д1

Делитель 7 из импульсов генератора 1 вырабатывает последовательность импульсов Fnog, с периодом, равным периоду повторения опорных строб-импульсов, которые поступают на второй вход блока 4 синхронизации. С поступлением первого же импульса из последовательности F(,gg , если блок 4

10 синхронизации был предварительно

установлен импульсом записи в датчик 2 кода частоты, он вьфабатывает импульс, по длительности равный периоду следования импульсов генератора

15 1 и срабатьтается до прихода следующего импульса записи в датчик 2 кода частоты. Подробно описание блока 4 синхронизации приведено ниже. Полученный импульс сбрасывает накопитель .ньш сумматор 11 ведущего цифрового синтезатора 3 в ноль, таким образом, осуществляется привязка по фазе при смене частоты посылки к импульсам . Ведущий цифровой синтезатор 3

25 имитирует основной луч многочастотного сигнала.

Последующие (ведомые) цифровые синтезаторы имитируют дополнительные лучи сигнала при многолучевых

30 каналах связи, которые задержаны на время &tj относительно ведущего цифрового синтезатора 3 (в дальнейшем групповое запаздывание сигнала). Вырабатываемые ими напряжения по часто25 те равны частоте ведущего цифрового синтезатора 3, но имеют различные фазовые сдвиги для всех частот сигнала, которые равны

20

40

F,:- -у

0

i.tj

где - сдвиг фаз между напряжениями частотных посылок ведомого и ведущих синтеза- 5торов;

- текущая частота посылки многочастотного сигнала; - время задержки сигнала ведомых цифровых синтезаторов 3 относительно ведущего. Работа ведомых цифровых синтезаторов 3 аналогична работе ведущего синтезатора, исключая момент привязки, который для каждого из синтеза- (- торов задается кодом, записываемым в регистр 6 кода задержки и опреде- лякщим групповое запаздывание для всех частот вырабатываемого данным синтезатором напряжения сигнала отнссительно ведутдего цифрового синтезатора 3. Привязка этих цифровых синтезаторов 3 происходит следующим образом. Поразрядно выходы делителя 7 соединены с блоками 5 сравнения, на вторые входы которых поступают соответствующие разряды с регистров 6 кода задержек. Задавая в регистры 6 кода задержек различные значения на выходе блока 5 сравнения можно получать импульсы, заниманпцие любые промежуточные значения между импульсами повт Делителя 7, временное положение которых и характеризует групповое время запаздывания для частотных посылок сигнала соответствующего луча, Далее импульсы с блока 5 сравне1ШЯ поступают на соответствующие блоки 4 синхронизации, работа которых анапо- гична работе блока 4 синхронизации ведущего цифрового синтезатора 3.

На выходе каждого 1 фрового синтезатора 3 установлен аттенюатор 8,с помощью которого можно задавать требуемую величину напряжения соответст- вукяцего луча. Сумматор 9 формирует суммарный сигнал, которьй через фильтр 10 нижних частот поступает на вьгход устройства.

I Блок 4 синхронизации (фиг. 2)

работает следующим образом.

Задним фронтом импульса записи в датчик 2 кода частоты триггер 14 переходит в единичное состояние. Зад ним фронтом импульса . триггер

15переходит в единичное состояние, Задним фронтом импульса триггер

16также переходит в единичное состояние, формируя передний фронт выходного импульса, который сбрасывает в исходное состояние триггеры 14 и 15. На D-входе триггера 1б таким образом устанавливается положение

.

логического О, и следующий задний

r л

5

ГТЦ

устанавливает

0

5

0

5

фронт импульса F

триггер 16 в исходное состояние. Таким образом, на выходе триггера 16 формируется импульс, по длительности равный периоду следования импульсов частотой РГТИ которьй обнуляет накопительные сумматоры 11 цифровых синтезаторов 3 iacTOT.

Формула изобретения

Цифровой генератор многочастотного сигнала, содержащий генератор тактовых импульсов, выход которого соединен с,первыми входами N цифровых синтезаторов, вторые входы которых соединены с выходом датчика кода частоты, выходы N цифровых синтезаторов через соответствующие N аттенюаторов соединены с входами сумматора, выход которого соединен с входом фильтра нижних частот, отли чающий - с я тем, что, с целью повышения стабильности работы, в него введены делитель,N блоков синхронизавди, (N-1) блоков сравнения, (N-1) регистров кодов задержки, причем вход делителя соединен с входом генератора тактовых импульсов и первыми входами N блоков синхронизации, выходы которых соединены с соответствующими третьими входами N цифровых синтезаторов., первый выход делителя соединен с вторым входом первого блока синхронизации, а вторые входы (N-1) блоков синхронизации соединены с соответст- вуклцими выходами (N-1) блоков сравнения, первые входы которых соединены с вторым выходом делителя, вто- . рые входы (N-1) блоков сравнения соединены с. соответгч вукйцими выходами (N-1) регистров кодов задержек, :третьи входы N блоков синхронизации объединены и соединены с- входом дат- чика кода.частоты,

14

(Лмп. записи

и

поВт. 15

гтн

16

Фие.2

| Авторское свидетельство СССР № 1200390, кл Н 03 К 3/84, 04.01.84., |

Авторы

Даты

1989-08-07—Публикация

1987-12-03—Подача