4

СО со

4

Изобретение относится к импульсно технике и может быть использовано в контрольно-измерительной технике.

Целью изобретения является повьппе ние быстродействия.

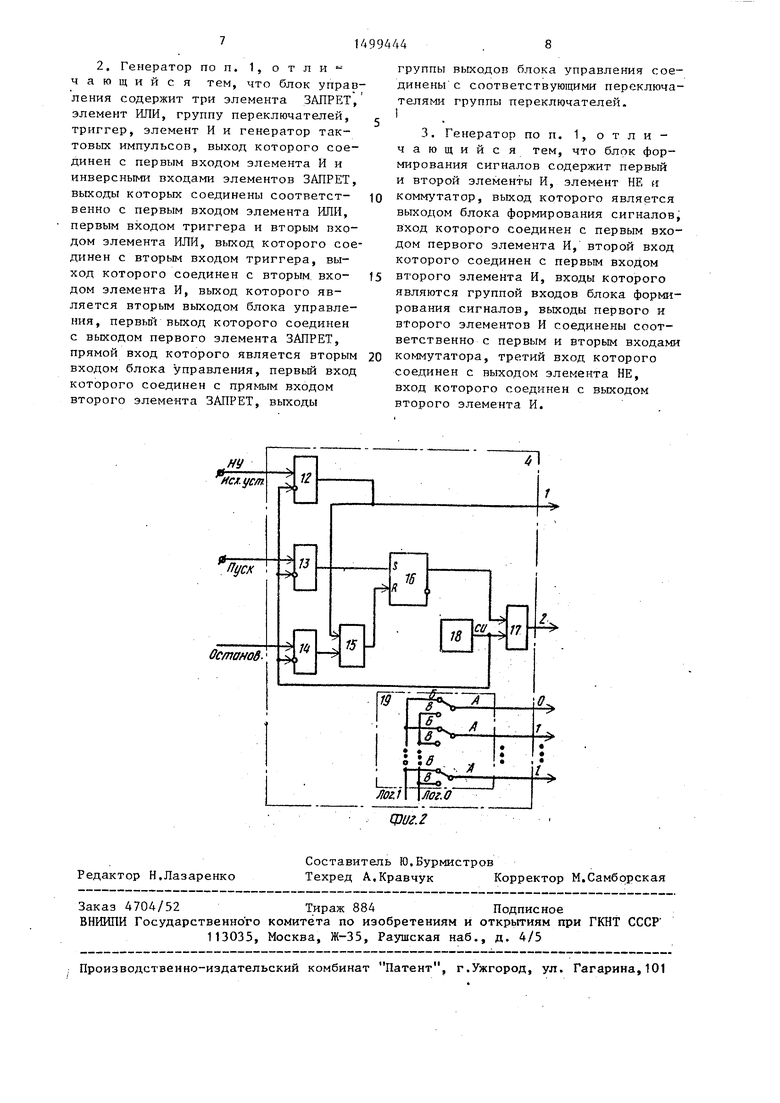

На фиг. 1 приведена схема структурная электрическая генератора псевдослучайных двоичных последовательностей; на фиг. 2 - схема блока управления.

Генератор псевдослучайных двоичных последовательностей содержит блок 1 памяти, адресные входы которого соединены с группой управляющих выходов генератора 2 псевдослучайных чисел, шину Пуск 3, соединенную с первым входом блока 4 управления, п блоков 5.1-5.П формирования сигналов шину 6 начальной установки, группу сумматоров 7,1-7.п по модулю два, первые входы которых соединены с выходами соответствующих блоков 5.1- 5,п формирования сигналов, группы входов которых соединены с соответствующими группами выходов генератора 2.псевдослучайных чисел, первьй и второй входы которого соединены соответственно с первым и вторым выходам блока 4 управления, второй вход которого соединен с шиной 6 начальной установки. Выходы группы выходов бло ka 4 управления соединены с вторыми входами соответствующих сумматоров, 7.1-7.П по модулю два. Выходы блока 1 памяти соединены с входами соответствующих блоков 5.1-5,п формирования сигналов.

Блок 5.1 (i 1, 2, ..., п) формирования сигналов (фиг. 1) содержит первый 3 и второй 9 элементы И, элемент НЕ 10 и коммутатор 11, выход которого является выходом блока 5.1 формирования сигналов, вход которого соединен с первым входом первого элемента И 8, второй вход которого соединен с первым входом второго элемента И 9, входы которого являются группой входов блока 5.1 формирования сигналов. Выходы первого 8 и второго 9 элементов И соединены соответственно с первым и вторым входами коммутатора 11, третий вход которого соединен с выходом элемента НЕ 10, вход которого соединен с выходом второго элемента И 9.

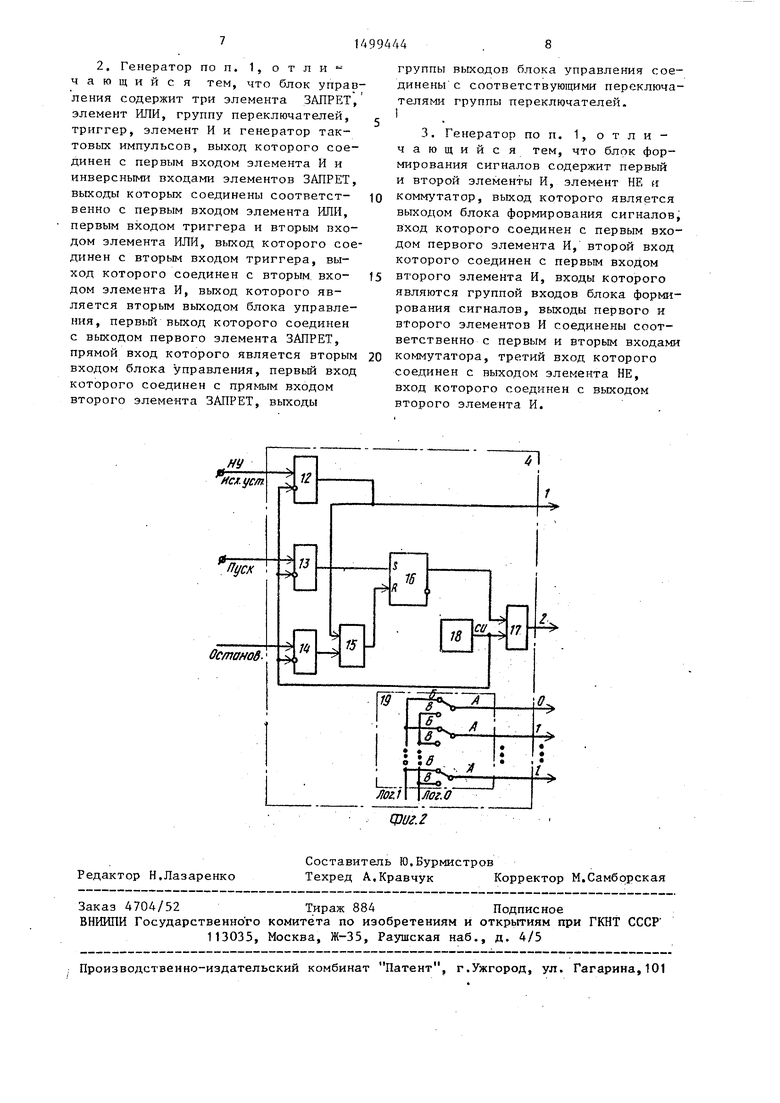

Блок 4 управления (фиг. 2) содержит первый - третий элементы ЗАПРЕТ 1 2- 14, элемент ИЛИ 15, выход которого

0

0

5

0

5

0

5

0

5

соединен с вторым входом триггера 16, выход которого соединен с вторым входом элемента И 17, первый вход кото рого соединен с выходом генератора 18 тактовых импульсов, группу 19 переключателей, выходы которых являются группой выходов блока 4 управления, второй выход которого соединен с выходом элемента И 17, первый вход которого соединен с инверсными, входами второго 13 третьего 14 элементов ЗАПРЕТ и инверсным входом первого элемента ЗАПРЕТ 12, выход Которого соединен с первым входом элемента ИЛИ 15 и является первым выходом блока 4 управления, первый и второй входы которого соединены с прямыми входами соответственно второго 13 и первого 12 элементов ЗАПРЕТ, Выход второго элемента ЗАПРЕТ 13 соединен с первым входом триггера 16. Выход третьего элемента ЗАПРЕТ 14 соединен с вторым входом элемента ИЛИ 15.

Генератор псевдослучайных двоичных последовательностей работает следующим образом.

При поступлении по шине 6 начальной установки на второй вход блока 4 управления единичного сигнала Исходная установка синхроимпульс с выхода его элемента ЗАЛРЕТ; 12 (первый выход блока 4 управления) устанавливает генератор 2 псевдослучайных чисел в начальное (некоторое ненулевое) состояние. Этот же синхроимпульс (СИ) через элемент ИЛИ 15 устанавливает триггер 16 в нулевое состояние, которое блокирует прохождение сигналов с выхода генератора 18 тактовых импульсов на второй вход генератора 2 псевдослучайных чисел. Затем на шину Пуск 3 подается единичный сигнал. По приходу сигнала СИ уровень логической 1 с выхода элемента ЗАПРЕТ 13 проходит на первый вход триггера 16, устанавливая его в единичное состояние и разрешая тем самым вьвдачу тактовых импульсов с выхода генератора 18 тактовых импульсов на вход генератора 2 псевдослучайных чисел, который начинает формировать псевдослучайные числа. Последние с группы его управпякящу. выходов поступают на адресные входы блока 1 памяти, в результате чего на выходы блока 1 памяти вьщается содержамое дайной ячейки памяти. Информация с кажцого

5

из выходов бпока 1 памяти чепез элемент И 8 соответствующего блока 5 формирования сигналов поступает на вхоц коммутатора 11.

При поступлении с соответствующе группы выходов генератора 2 псевдо- спучайных чисел на входы соответствующего элемента И 9 т-разрядного псевдослучайного кода, на выходе этого элемента И 9 устанавливается сигнал логической 1, если на всех его входах присутствует уровень логической 1, или устанавливается уровень логического О, если хотя бы на одном из входов этого элемент И 9 присутствует уровень логического О, Информаисия с выхода этого элемента И 9 поступает ка второй вход соответствующего коммутатора 11. На первый вход соответствующего элемента И 8, объединенный с одним из входов соответствующего т-входо- вого элемента И 9, поступает псевдослучайный двоичньй код, который управляет прохождением сигналов с соответствующего выхода блока 1 памяти на первый вход соответствующего коммутатора 11. Поступление уровня логического О на первый вход соот- ветству1ага;его коммутатора 11 приводит к вьщаче с его выхода информации, прошедшей элемент НЕ 10, а уровень логической 1 вызывает выдачу на выход коммутатора 11 информации, пришедшей непосредственно на второй вход коммутатора 11,

На выходах устройства (выходах сумматоров 7,1-7.п по модулю два) формируются псевдослучайные двоичные последовательности с заданным диапазоном, вероятности.. Это происходит следующим образом. На первые входы сумматоров 7,1-7.п по модулю два с выходов соответствующих блоков 5.1- 5.П формирования сигналов поступают псевдослучайные двоичные последовательности, а На вторые входы - сигналы с соответствуюпщх выходов группы выходов блока 4 управления (поступают уровни логического О или логи- .ческой 1). При наличии на втором входе соответствующего сумматора 7,1 7.П по модулю два уровня логического О Псевдослучайная двоичная последовательность с вьпсода соответствующег блока 5.1-5.П проходит на выход устройства без изменения, а при наличии уровня логической 1 на выход

0

5

0

устройства выдается ивертиронанная псевдослучайная двоичная последовательность.

Для останова ycTpoiicTBa на вход Останов блока 4 управления необходимо подать уровень логической 1. По приходу на инверсный вход элемента ЗАПРЕТ 14 сигнала СИ.уровень логической 1 проходит на его выход и далее через элемент НЛИ 15 на второй вход триггера 16.

Триггер 16 сбрасывается при этом в нулевое состояние, которое, поступая на второй вход элемента И 17,. запрещает вьщачу тактовых импупъ- сов на второй выход блока 4 управления.

Таким образом, устройство имеет длительность рабочего такта, определяемую временем переключения генератора 2 псевдослучайных чисел, блока 1 памяти и блока 5 формирования сигналов.

5

Формула изобретения

1. Генератор псевдослучайных двоичных последовательностей, содержащий блок памяти, генератор псевдо0 случайных чисел, первые выходы соответствующих групп выходов которого соединены с первым входами групп входов соответствующих п блоков формирования сигналов, входы которых

g соединены с соответствующими выходами блока памяти, блок управления, первьш и второй входы которого соединены соответственно с шиной Пуск и шиной начальной установки, а пер0 вый и второй выходы - соответственно с первым и вторым входами генератора псевдослучайных чисел, о т- личающийся тем, .что, с целью повышения быстродействия, в

5 него введена группа из п сумматоров по модулю два, первые входы которых соединены с выходами соответствующих п блоков фор 0-1рования сигналов, соответствующие входы, кроме первого,

0 групп входов которых соединены с соответствующими, кроме первого, выходами групп выходов генератора псевдослучайных чисел, группа управляющих выходов которого соединена с

5 группой входов блока памяти, группа выходов блока управления соединена с вторыми входами соответствующих сумматоров по модулю два группы из |П сумматоров по модулю два.

2, Генератор по п. 1, о т л и -- чающийс я тем, что блок управления содержит три элемента ЗАПРБ1Т, элемент ИЛИ, группу переключателей, триггер, элемент И и генератор тактовых импульсов, выход которого соединен с первым входом элемента И и инверсными входами элементов ЗАПРЕТ, выходы которых соединены соответственно с первым входом элемента ИЛИ, первым входом триггера и вторым входом элемента ИЛИ, выход которого соединен с вторым входом триггера, выход которого соединен с вторым входом элемента И, выход которого является вторым выходом блока управления, первьп выход которого соединен с выходом первого элемента ЗАПРЕТ, прямой вход которого является вторым входом блока управления, первый вход которого соединен с прямым входом второго элемента ЗАПРЕТ, выходы

группы выходов блока управления соединены с соответствующими переключателями группы переключателей.

3. Генератор по п. 1, о т л и - чающийс я тем, что блок формирования сигналов содержит первый и второй элементы И, элемент НЕ и

коммутатор, выход которого является выходом блока формирования сигналов, вход которого соединен с первым входом первого элемента И, второй вход которого соединен с первым входом

второго элемента И, входы которого являются группой входов блока формирования сигналов, выходы первого и второго элементов И соединены соответственно с первым и вторым входами

коммутатора, третий вход которого соединен с выходом элемента НЕ, вход которого соединен с выходом второго элемента И..

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования тестов | 1987 |

|

SU1444781A1 |

| Генератор псевдослучайных чисел | 1985 |

|

SU1272484A1 |

| Генератор случайных чисел | 1990 |

|

SU1817094A1 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1986 |

|

SU1332542A2 |

| Генератор псевдослучайных чисел | 1981 |

|

SU1010622A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Генератор псевдослучайных последовательностей | 1988 |

|

SU1636993A1 |

| Устройство для контроля логических блоков | 1983 |

|

SU1101825A1 |

| ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ (ВАРИАНТЫ) | 1999 |

|

RU2163027C2 |

| Устройство для профессионального отбора операторов | 1990 |

|

SU1777165A1 |

Изобретение относится к импульсной технике. Цель изобретения - повышение быстродействия-достигается введением в устройство сумматоров 71-7N по модулю два, образованию новых функциональных связей, а также соответствующим выполнением блока 4 управления и блоков 51-5N формирования сигналов. На чертеже также изображены блок 1 памяти, генератор 2 псевдослучайных чисел, шины 3 и 6 "Пуск" и начальной установки, элементы И 8 и 9, элемент НЕ 10 и коммутатор 11. 2 з.п. ф-лы, 2 ил.

| Генератор случайных сигналов | 1978 |

|

SU750709A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское,свидетельство СССР № 1256163, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| OcmoHoS | |||

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1989-08-07—Публикация

1988-01-07—Подача