30

12

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровая следящая система | 1988 |

|

SU1522152A1 |

| Двухотсчетный следящий привод | 1989 |

|

SU1700535A1 |

| Преобразователь угла поворота вала в код | 1990 |

|

SU1751850A1 |

| Двухканальный цифроаналоговый следящий привод | 1988 |

|

SU1631517A1 |

| Замкнутый шаговый электропривод с самокоммутацией и дроблением шага | 1988 |

|

SU1511842A1 |

| Преобразователь перемещения в код | 1986 |

|

SU1363462A1 |

| Регулятор | 1984 |

|

SU1260913A1 |

| Устройство для регулирования давления | 1984 |

|

SU1180853A1 |

| Устройство для позиционирования головок записи-воспроизведения | 1988 |

|

SU1550576A1 |

| Преобразователь угол-код | 1986 |

|

SU1336242A1 |

Изобретение касается автоматического управления и может быть использовано в контуре регулирования положения следящих приводов моделирующих стендов и имитаторов различных систем. Цель изобретения - повышение точности системы позиционирования. Система содержит цифроаналоговые 3 и аналоговый 5 блоки выделения ошибки, преобразователь 2 перемещения в код, задатчик 1 положения, инверторы 8, 13, 14, коммутаторы 7, 12 сигналов, масштабирующий усилитель 9, сумматор 6 коррекции. В системе позиционирования используются сигналы обратной связи: цифровой с заранее определенным дискретом и аналоговый, линейно нарастающий от минимального до максимального значения в промежутках между моментами изменения цифровых значений. 1 з.п. ф-лы, 4 ил.

о со

С tsD

1500992

Система содержит цифроаналоговые 3 и аналоговый 5 блоки выделения ошибки, преобразователь 2 перемещая в код, задатчик 1 положения, инверторы 8, j 13,14, коммутаторы 7, 12 сигналов, масштабирующий усилитель 9, сумматор 6 коррекции. В системе позициониро25

Изобретение относится к автоматическому управлению и может быть использовано для улучшения качества процесса регулирования следящих при- 15 водов моделирующих стендов и имитаторов.

Целью изобретения является повышение точности системы.

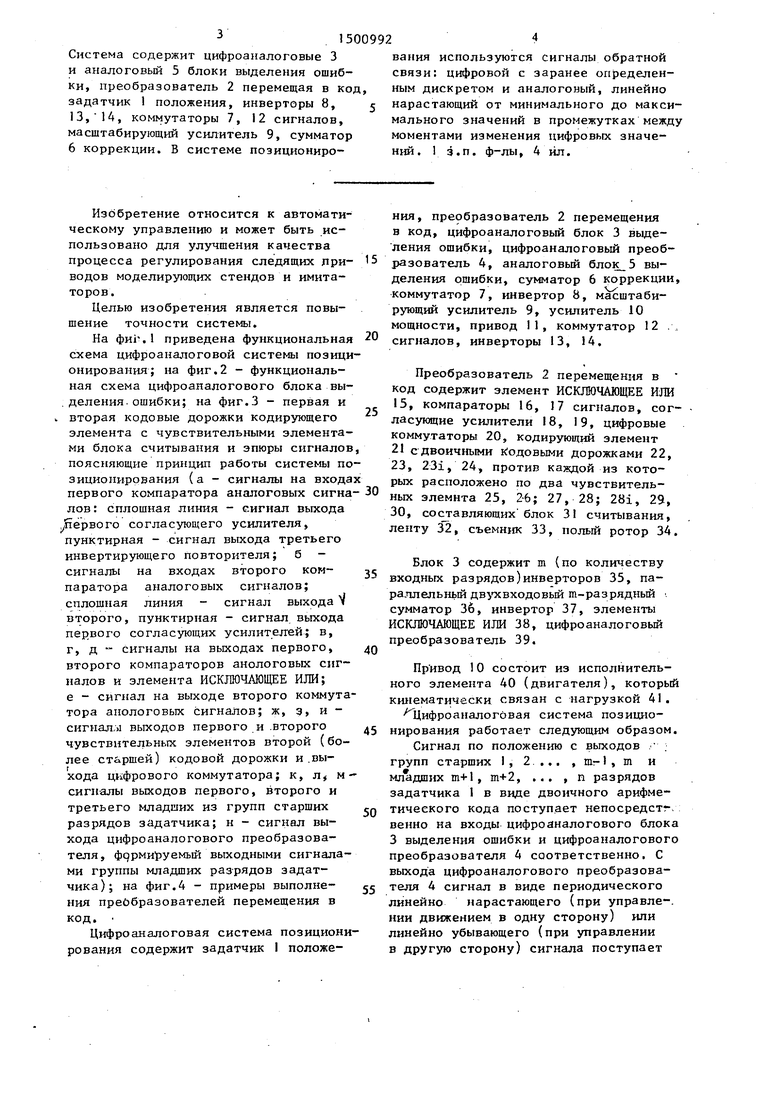

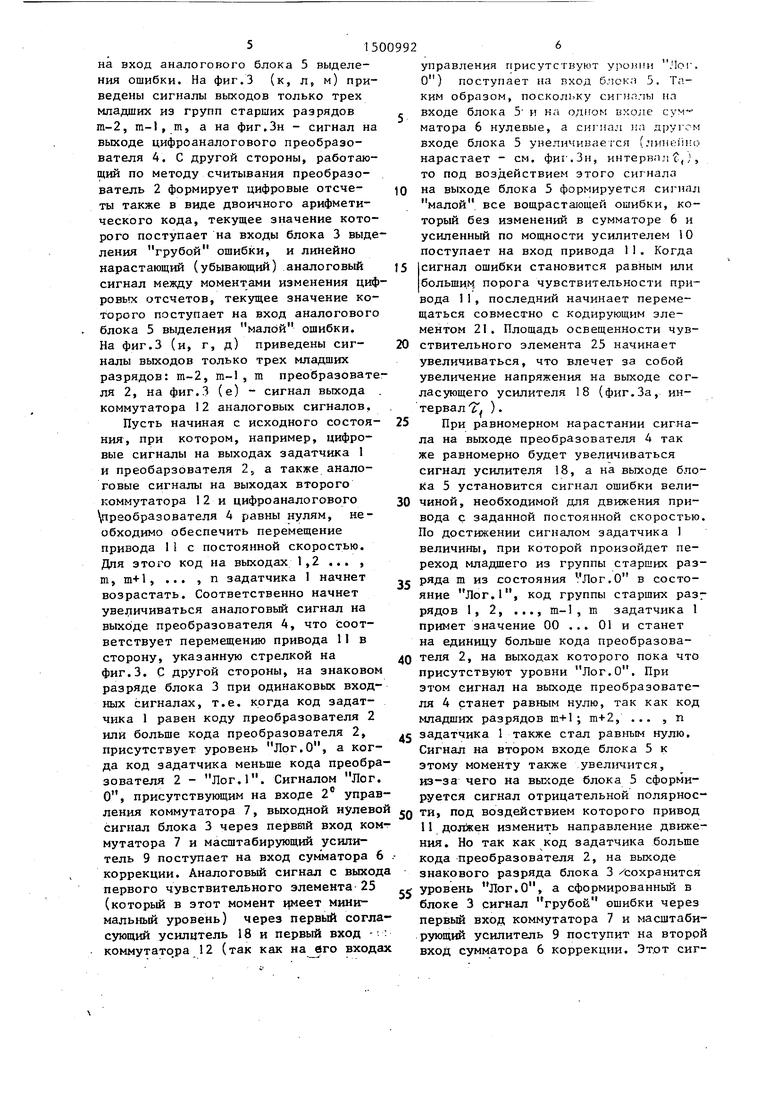

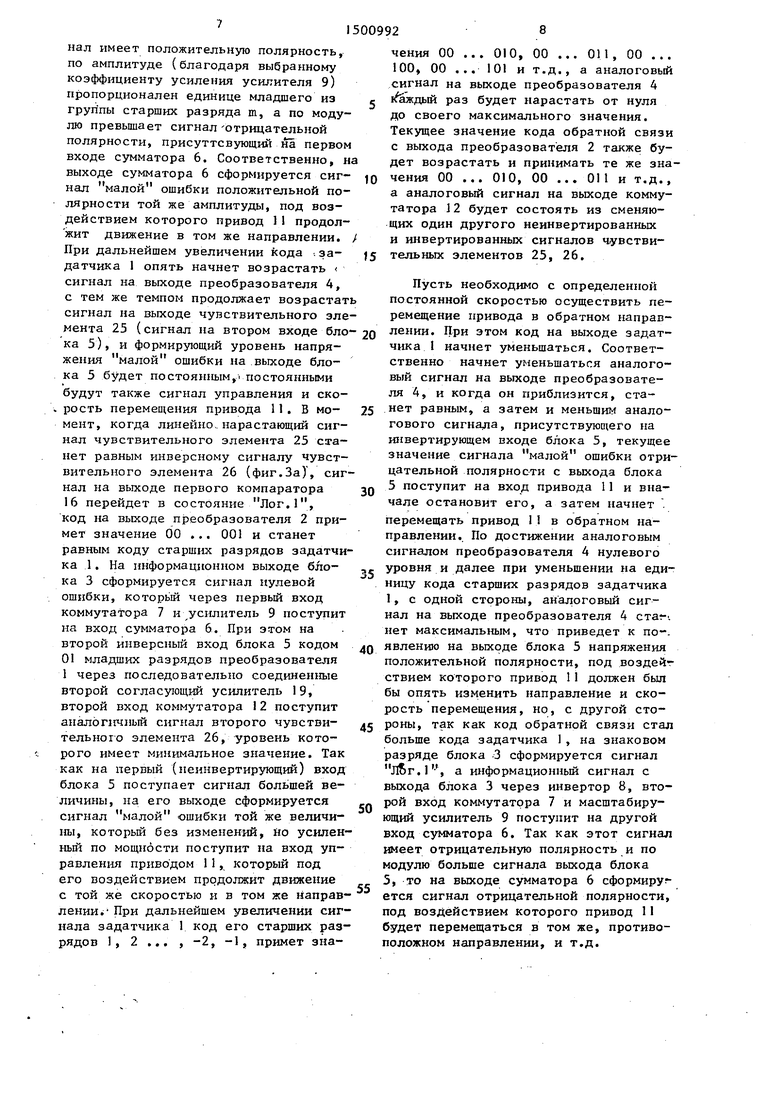

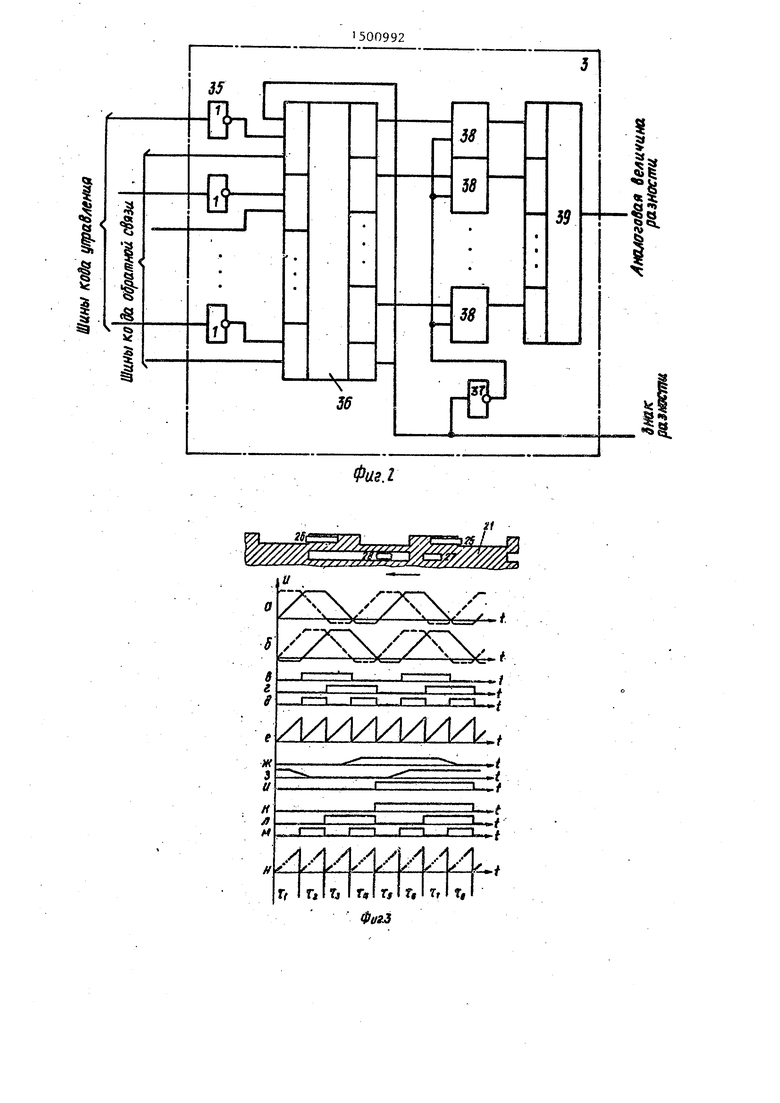

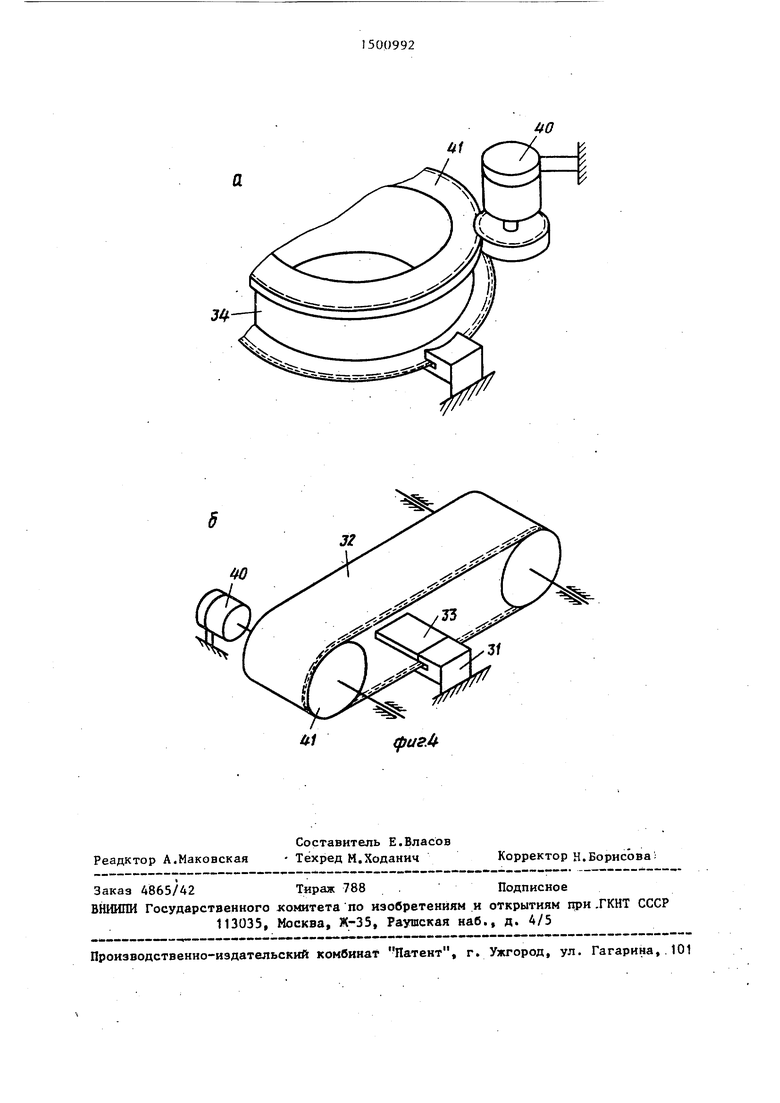

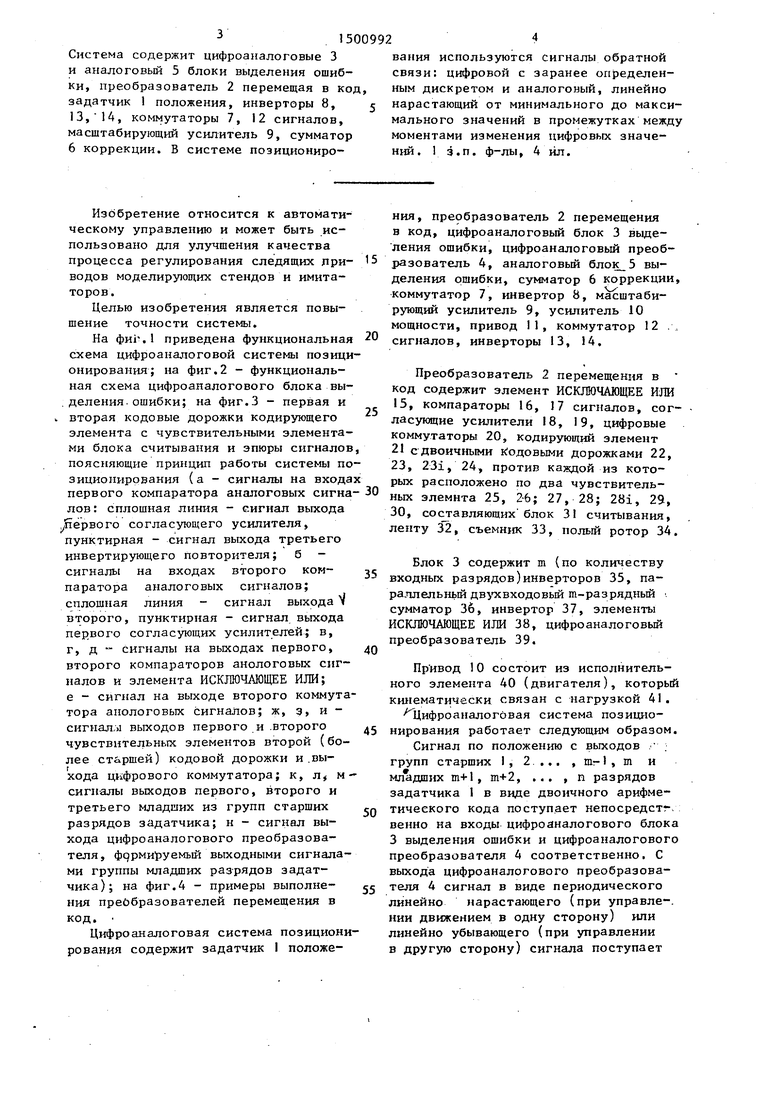

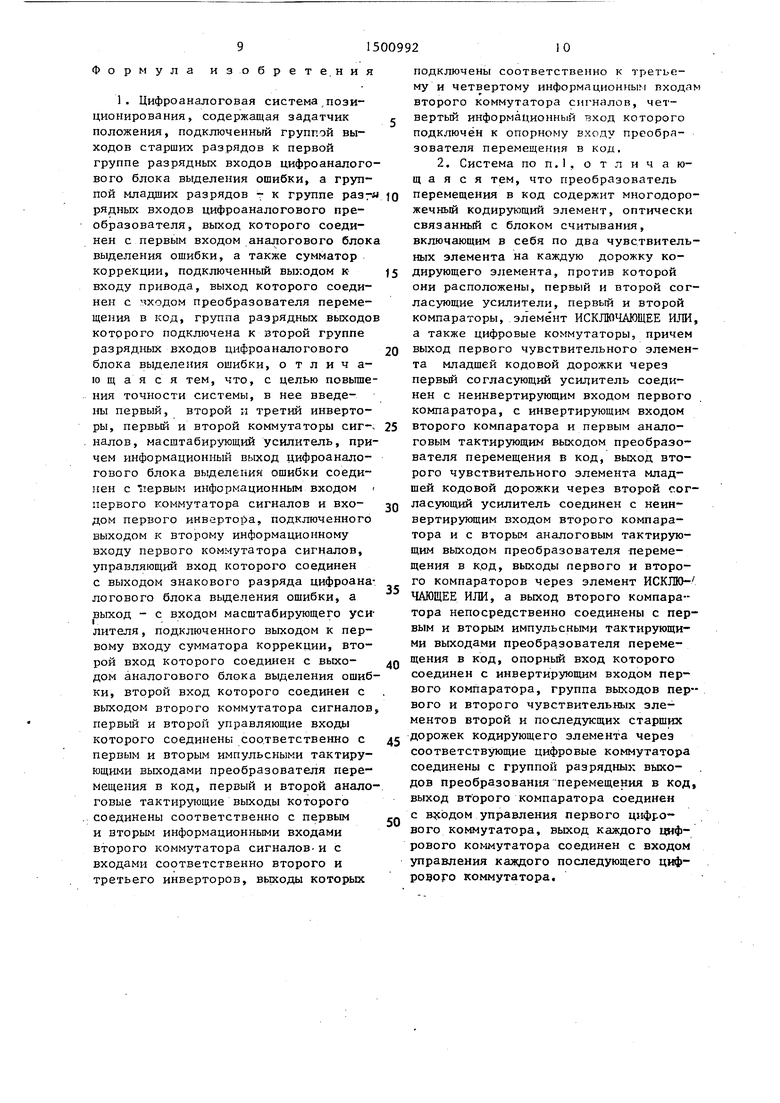

На фиг.1 приведена функциональная 0 схема цифроаналоговой системы позиционирования; на фиг.2 - функциональная схема цифроаналогового блока вы- . деления.ошибки; на фиг.З - первая и вторая кодовые дорожки кодирующего элемента с чувствительными элементами блока считывания и эпюры сигналов, поясняющие принцип работы системы позиционирования (а - сигналы на входах первого компаратора аналоговых сигма- 30 лов: сплошная линия - сигнал выхода yfiepBoro согласующего усилителя, пунктирная - сигнал выхода третьего инвертирующего повторителя; б - сигнальЕ на входах второго ком- ji; паратора аналоговых сигналов; сплошная линия - сигнал выхода V второго, пунктирная - сигнал выхода первого согласующих усилителей; в, г, д - сигналы на выходах первого, 40 второго компараторов анологовых сигналов и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ; е - сигнал на выходе второго коммутатора анологовых сигналов; ж, з, и - сигнал; 1 выходов первого и .второго чувствительных элементов второй (более старшей) кодовой дорожки и .выхода цифрового коммутатора; к, л м- сигналы выходов первого, второго и третьего младиих из групп старших ,,, разрядов задатчика; н - сигнал выхода цифроаналогового преобразователя, фqpмиt)yeмый выходными сигналами группы младших разрядов задат- чика); на фиг.4 - примеры выполне- j ния преобразователей перемещения в код. .

Цифроаналоговая система позиционирования содержит задатчик I положевания используются сигналы обратной связи: цифровой с заранее определенным дискретом и аналоговый, линейно нарастающий от минимального до максимального значений в промежутках между моментами изменения цифровых значений . 1 3.п. ф-лы, 4 йл.

5

5

0 0 i; 0 ,,

ния, преобразователь 2 перемещения в код, цифроаналоговый блок 3 выделения ошибки, цифроанапоговьй преоб- 1)азователь 4, аналоговый выделения ошибки, сумматор 6 коррекции, коммутатор 7, инвертор В, масштабирующий усилитель 9, усилитель 10 мощности, привод 11, коммутатор 12 .. сигналов, инверторы 13, 14.

Преобразователь 2 перемещения в код содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 15, компараторы 16, 17 сигналов, согласующие усилители 18, 19, цифровые коммутаторы 20, кодирующий элемент 21 с двоичными Кодовыми дорожками 22, 23, 231, 24, против каждой из которых расположено по два чувствительных элемнта 25, 2-6; 27, 28; 281, 29, 30, составляющих блок 31 считывания, ленту 32, съемник 33, полый ротор 34.

Блок 3 содержит m (по количеству входных разрядов)инверторов 35, па- раллельньш дв освходовый т-разрядный . сумматор Зб, инвертор 37, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 38, цифроаналоговый преобразователь 39.

Пр ивод 10 состоит из исполнительного элемента 40 (двигателя), который кинематически связан с нагрузкой 41. Цифроаналоговая система позиционирования работает следующим образом.

Сигнал по положению с выходов ; групп старших I, 2.... , т-1, m и мл адших т+1, т+2, ... , п разрядов задатчика 1 в виде двоичного арифметического кода поступает непосредстг, венно на входы цифроаналогового блока 3 выделения ошибки и цифроаналогового преобразователя 4 соответственно. С выхода цифроаналогового преобразователя 4 сигнал в виде периодического линейно нарастающего (при управле-. НИИ движением в одну сторону) или линейно убывающего (при управлении в другую сторону) сигнала поступает

515

на вход аналогового блока 5 выделения ошибки. На фиг.З (к, л, м) приведены сигналы выходов только трех младших из групп старших разрядов т-2, т-1, т, а на фиг.Зн - сигнал на выходе цифроаналогового преобразователя 4. С другой стороны, работающий по методу считывания преобразователь 2 формирует цифровые отсче- ты также в виде двоичного арифметического кода, текущее значение которого поступает на входы блока 3 выделения грубой ошибки, и линейно нарастающий (убывающий) аналоговый сигнал между моментами изменения циф ровьгк отсчетов, текущее значение которого поступает на вход аналогового блока 5 выделения малой ошибки. На фиг.З (и, г, д) приведены сиг- налы выходов только трех младших разрядов: т-2, т-1, m преобразователя 2, на фиг.З (е) - сигнал выхода коммутатора 12 аналоговых сигналов,

Пусть начиная с исходного состояния, при котором, например, цифровые сигналы на выходах задатчика 1 И преобарзователя 2, а также аналоговые сигналы на выходах второго коммутатора 12 и цифроаналогового преобразователя 4 равны нулям, необходимо обеспечить перемещение привода 1I с постоянной скоростью. Для этого код на выходах 1,2 ,.. , ш, т+1, ... , п задатчика 1 начнет возрастать. Соответственно начнет увеличиваться аналоговый сигнал на выходе преобразователя 4, что соответствует перемещению привода 11 в сторону, указанную стрелкой на фиг.З. С другой стороны, на знаковом разряде блока 3 при одинаковых входных сигналах, т.е. когда код задатчика 1 равен коду преобразователя 2 или больше кода преобразователя 2, присутствует уровень Лог.О, а когда код задатчика меньше кода преобразователя 2 - Лог.1. Сигналом Лог,

0, присутствующим на входе 2° управд5 задатчика 1 также стал равным нулю. Сигнал на втором входе блока 5 к этому моменту также увел1гчится, из-за чего иа вькоде блока 5 сформируется сигнал отрицательной полярнос- ления коммутатора 7, выходной нулевой ,JQ и, под воздействием которого привод сигнал блока 3 через первйй вход ком- i j должен изменить направление движения. Но так как код задатчика больше кода преобразователя 2, на выходе знакового разряда блока 3 /сохранится

первого чувствительного элемента 25 уровень Лог.О, а сформированный в (который в этот момент р4еет мини- блоке 3 сигнал грубой ошибки через

первый вход коммутатора 7 и масштабирующий усилитель 9 поступит на второй вход сумматора 6 коррекции. Этот сигмутатора 7 и масштабирующий усилитель 9 поступает на вход сумматора 6 коррекции. Аналоговый сигнал с выхода

мальный уровень) через первый согласующий усилитель 18 и первый вход -:: коммутат9ра 12 (так как входах

управления присутствуют уронии . loi . О) поступает на вход б.пок.ч 5. Таким образом, поскольку сигиллы на входе блока 5 и на одном входе сум- матора 6 нулевые, а сиг иал на другом входе блока 5 унеличивае г ся (.пинеГп с. нарастает - см. фих .Зн, интервал с , то под воздействием этого сигнала на выходе блока 5 формируется сигнал малой, все вощрастшощей ошибки, который без изменений в сумматоре 6 и усиленный по мощности усилителем IО поступает на вход привода 11. Когда сигнал ошибки становится равным или большим порога чувствительности привода I1, последний начинает перемещаться совместно с кодирующим элементом 21. Площадь освещенности J5 20

ствительного элемента 25 начинает увеличиваться, что влечет за собой увеличение напряжения на выходе согласующего усилителя 18 (фиг.За, ин- тервалТ ).

25 При равномерном нарастании сигнала на выходе преобразователя 4 так же равномерно будет увеличиваться сигнал усилителя 18, а на выходе блока 5 установится сигнал ошибки вели30 чиной, необходимой для движения привода с заданной постоянной скоростью По достижении сигналом задатчика 1 величины, при которой произойдет переход младшего из группы старших раз35 ряда m из состояния Лог.О в состояние Лог.1, код группы старших раз рядов 1, 2, ..., т-1, m задатчика 1 примет значение 00 ... 01 и станет на единицу больше кода преобразова40 теля 2, на выходах которого пока что присутствуют уровни Лог.О. При этом сигнал на вьсходе преобразователя 4 станет равным нулю, так как код младших разрядов т+1; т+2, ... , п

д5 задатчика 1 также стал равным нулю. Сигнал на втором входе блока 5 к этому моменту также увел1гчится, из-за чего иа вькоде блока 5 сформи10

15

25

1500992

нал имеет положительную полярность, по амплитуде (благодаря выбранному коэффициенту усиления усилителя 9) пропорционален единице младшего из груп пы старших разряда т, а по модулю превьшает сигнал отрицательной полярности, присуттсвующий на первом входе сумматора 6. Соответственно, на выходе сумматора 6 сформируется сигнал малой ошибки положительной полярности той же амплитуды, под воздействием которого привод 11 продолжит движение в том же направлении. При дальнейшем увеличении кода .за- датчика 1 опять начнет возрастать сигнал на выходе преобразователя 4, с тем же темпом продолжает возрастать сигнал на выходе чувствительного элемента 25 (сигнал на втором входе бло- 20 ка 5), и формирующий уровень напряжения малой ошибки на выходе блока 5 будет постоянным, постоянньми будут также сигнал управления и ско- рость перемещения привода 11. В момент, когда линейно, нарастающий сих- нал чувствительного элемента 25 станет равным инверсному сигналу чувствительного элемента 26 (фиг.За), сигнал на выходе первого компаратора 16 перейдет в состояние Лог.1, код на выходе преобразователя 2 примет значение 00 ... 001 и станет равным коду старших разрядов задатчи- ка 1. На информационном выходе блока 3 сформируется сигнал нулевой ошибки, которьм через первый вход коммутатора 7 и,усилитель 9 поступит на вход сумматора 6. При этом на второй инверсный вход блока 5 кодом 01 младших разрядов преобразователя 1 через последовательно соединенные второй согласующий усилитель 19, второй вход коммутатора 12 поступит аналопгчньй сигнал второго чувствительного элемента 26, уровень которого имеет минимальное значение. Так как на первый (неинвертирующий) вход блока 5 поступает сигнал большей величины, на его вьпсоде сформируется сигнал малой ошибки той же величины, который без изменений, йо усиленный по мощности поступит на вход уп- paвлeнliя приводом 1 1, который под его воздействием продолжит движение с той же скоростью и в том же направ лении - При дальнейшем увеличении сигнала задатчика 1 код его старших разрядов , 2 ... , -2, -1, примет зна30

35

40

45

50

,-55

ч с до с де че а та щи и те

по л чи ст вы ля не го ин зн ца ча пе пр си ур ни 1, на не яв по ст бы ро ро бо ра j вы ро ющ вх им мо 5, ет по бу по

0

5

5

0992

0

0

5

0

5

0

5

8

чения 00 ... 010, 00 ... 011, 00 ... 100, 00 ... 101 и т.д., а аналоговый сигнал на выходе преобразователя 4 1 аждый раз будет нарастать от нуля до своего максимального значения. Текущее значение кода обратной связи с выхода преобразователя 2 также будет возрастать и принимать те же значения 00 ... 010, 00 ... 011 и т.д., а аналоговый сигнал на выходе коммутатора 12 будет состоять из сменяющих один другого неинвертированньк и инвертированных сигналов чувствительных элементов 25, 26.

Пусть необходимо с определенной постоянной скоростью осуществить перемещение привода в обратном направлении. При этом код на выходе задатчика 1 начнет уменьшаться. Соответственно начнет уменьшаться аналоговый сигнал на выходе преобразователя 4, и когда он приблизится, станет равным, а затем и меньшим аналогового сигнала, присутствующего Fia инвертирующем входе блока 5, текущее значение сигнала малой ошибки отрицательной полярности с выхода блока 5 поступит на вход привода 11 и вначале остановит его, а затем начнет . перемещать привод 11 в обратном направлении. По достижении аналоговым сигналом преобразователя 4 нулевого уровня и далее при уменьшении на единицу кода старших разрядов задатчика 1, с одной стороны, аналоговый сигнал на выходе преобразователя 4 стаг-. нет максимальным, что приведет к по-. явлению на выходе блока 5 напряжения положительной полярности, под воздейг ствием которого привод 11 должен был бы опять изменить направление и скорость перемещения, но, с другой стороны, так как код обратной связи стал больше кода задатчика 1, на знаковом разряде блока 3 сформируется сигнал jftr.l - , а информационньш сигнал с выхода блока 3 через инвертор 8, второй вход коммутатора 7 и масштабирующий усилитель 9 поступит на другой вход сумматора 6. Так как этот сигиал имеет отрицательную полярность и по модулю больше сигнала выхода блока 5, то на выходе сумматора 6 сформиру; ется сигнал отрицательной полярности, под воздействием которого привод 11 будет перемещаться в том же, противоположном направлении, и т.д.

Формула изобрете.ния

5 0 5 O д 5 Q

5

подключены соответственно к третьему и четвертому информационным входам второго коммутатора сигналов, четвертый информационнь1Й вход которого подключён к опорному входу преобразователя перемещения в код,

I

«8

§

i

V

36

f f- 7Yjij fj j

$

N

ji

35

M t

IS.

S8

§.

Фиг.I

if

ФагЛ

f r

0

фиг.и

| Цифровая следящая система комбинированного регулирования | 1972 |

|

SU442458A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Аналого-цифровая следящая система | 1975 |

|

SU557351A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1989-08-15—Публикация

1987-12-01—Подача