1В

31501042

Изобретение относится к области вычислительной техники и может быть ис- псшьзовано при построении интегральных схем обработки цифровой информации- при многоуровневом представлении ий- формации.

Цель изобретения - снижение рассеиваемой мощности за счет уменьшения аппаратурных затрат.JQ

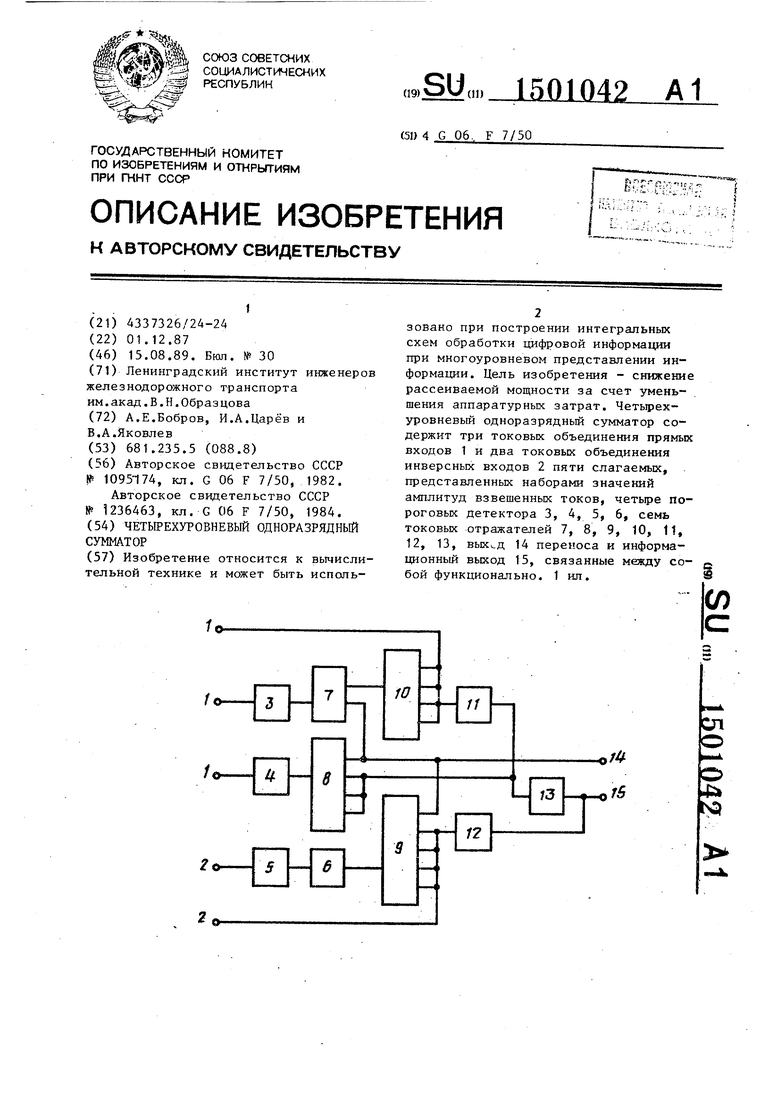

На чертеже представлена функциональная схема четьфехуровневого одноразрядного сумматора.

Сумматор содержит три токовых объе15 динения прямых входов 1 и два токовых объединения инверсных входов 2 пяти слагаемых, представленных наборами значений амплитуд взвешенных токов, первый-четвертый пороговые детекторы 0 3-6, первый-седьмой токовые отражатели 7-13, выход 14 переноса и информационный выход 15, связанные между

собой функционально.

25

перенос (14): О О О О 1 1 сумма (15) : 012301

Последовательности значений токов

во всех точках сумматора приведены 30 в табл.2.

Полное совпадение последовательностей значений, полученных в табл.2, с заранее вычисленными последовательностями значений токов на выходах05 14, 15 переноса и суммы сумматора свидетельствуют о правильности логики его работы.

Формула изобретения

Четырехуровневый одноразрядный сумматор, содержащий четьфе пороговых детектора и семь токовых отражателей, выполненных на базе составных транзисторов с инжекционным питанием причем прямые входы пяти слагаемых соединены с входами первого и второ- го пороговых детекторов, выходы которых соединены соответственно с входами первого и второго токовых отражателей, инверсный вход пяти слагаемых соединен с входом третьего порогового детектора, выход которого соединен с входом четвертого порого

вого детектора, выход которого соеди

I

1

I

Пороговые детекторы и токовые отражатели выполнены из составных транзисторов с неуправляемыми инжекторами, веса которых, а также схемы вклнтчения

представлены в табл.1.

Работа четырехзначного сумматора описывается с помощью последовательностей значений токов, упорядоченных относительно входной последовательности значений токов. Среди 1024 всевозможных конкретных значений комбинаций четырехзначных пяти слагаемьк только 16 имеют различные суммы значений компонентов: 0.1.2.3.4.5.6.7. 8.9.10.11.12.13.14.15. Считая, что на входы - объединения 1 поступает такая упорядоченная последовательность значений, можно соответствующими последовательностями значений в других точках сумматора однозначно и полно описать работу схемы. Гри этом на выходах переноса и суммы должны получиться последовательности:

1 22223333; 301230123,

1 нен с входом третьего токового отражателя, первый выход которого соединен с первыми вькодами первого и второго токовых отражателей и является выходом переноса сумматора, второй выход первого токового отражателя соединен с входом четвертого вого отражателя, четыре выхода которого соединены с прямым входом пяти слагаемых и с входом пятого токового отражателя, инверсный вход пяти слагаемых соединен с входом шестого токового отражателя, выход которого соединен с выходом седьмого токового отражателя и является информационным выходом сумматора, выход пятого токового отражателя соединен с входом седьмого токового отражателя, отличающийся тем, что, с целью снижения рассеиваемой мощности за счет уменьшения аппаратурнь х затрат, второй, третий и четвертый выходы второго токового отражателя соединены, с входом седьмого токового отражателя, а второй, третий, четвертый и пятый выходы третьего токового отражателя соединены с входом шестого токового отрс1жателя.

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Четырехуровневый однозарядный сумматор | 1984 |

|

SU1236463A1 |

| Одноразрядный К-значный сумматор | 1985 |

|

SU1312566A1 |

| Одноразрядный К- значный сумматор | 1987 |

|

SU1499336A1 |

| Четырехзначный сумматор | 1984 |

|

SU1193797A1 |

| Одноразрядный сумматор на инжекционных элементах | 1985 |

|

SU1275430A1 |

| СПОСОБ ПОЛНОГО СЛОЖЕНИЯ - ВЫЧИТАНИЯ ЧИСЕЛ, КОДИРУЕМЫХ СИГНАЛАМИ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1998 |

|

RU2132566C1 |

| СПОСОБ СЛОЖЕНИЯ-ВЫЧИТАНИЯ ЧИСЕЛ, КОДИРУЕМЫХ СИГНАЛАМИ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1997 |

|

RU2109325C1 |

| Многозначный сумматор | 1984 |

|

SU1251319A1 |

| Устройство для формирования остатков по модулю | 1986 |

|

SU1449986A1 |

| Четырехуровневый одноразрядный сумматор | 1982 |

|

SU1095174A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении интегральных схем обработки цифровой информации при многоуровневом представлении информации. Цель изобретения - снижение рассеиваемой мощности за счет уменьшения аппаратурных затрат. Четырехуровневый одноразрядный сумматор содержит три токовых объединения прямых входов 1 и два токовых объединения инверсных входов 2 пяти слагаемых, представленных наборами значений амплитуд взвешенных токов, четыре пороговых детектора 3, 4, 5, 6, семь токовых отражателей 7, 8, 9, 10, 11, 12, 13, выход 14 переноса и информационный выход 15, связанные между собой функционально. 1 ил.

Точка схемы

Последовательность значений токов

4444444 4 5 68 88 8

Вход 1 (условно) О 1 2 3 4 5 6 7 . . .. . .

Вход 2 (условно)15 14 13 12 11. 10 9 8 7 6 5 4 3 2 1

Вход ДЗ

Вход Д4

Вход Д5

Вход Д6

Вход Д7

Вход 08

Вход 09

Вход 010

Вход 011

Вход 012

Вход 0-13

Выход (14)

Выход (15)

0123 0123

44444444444 00000000000 11 1 10000000 1 1

1 1 1 1

000 о 1 45 6 74

777777 321032

1 1 1 6

7

1

1000

1111 1. 1 1 1

7777 7765

00001 1 1 1

01230123012

9 10 11 12 13 14

33 3 222

4 8 4 О О

о 1 1

7 4 3 2

4 8 3 1 О О О 1 7 7 3 3

4 8 2 1 О О О 1 7 6 3 3

о 1

3 3

Редактор О. Спесивых

Составитель В. Гусев

Техред Л.Олийнык Корректор Н, Король

Заказ 4868/44

Тираж 668

ВНИИПИ Государственного ко гатета по изобретениям и открытиям при ,ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Таблица 2

4444 8 88 8

8 7 6 5 4 3 2 1

4444 0000 0000

1000

1111 1. 1 1 1

7777 7765

1

3012

9 10 11 12 13 14 15

О 4 8 О 1 О О О

t

7 4 3 3 3

33 3 222

4 8 4 О О

о 1 1

7 4 3 2

4 8 3 1 О О О 1 7 7 3 3

4 8 2 1 О О О 1 7 6 3 3

1 1 О

о о 1

7 5 3 3

Подписное

Авторы

Даты

1989-08-15—Публикация

1987-12-01—Подача