Изобретение относится к вычислительной технике и может быть использовано при построении интегральных схем обработки цифровой информации, например, в умножителях и функциональных преобразователях.

Целью изобретения является расширение области применения за счет осуществления суммирования пяти операндов.

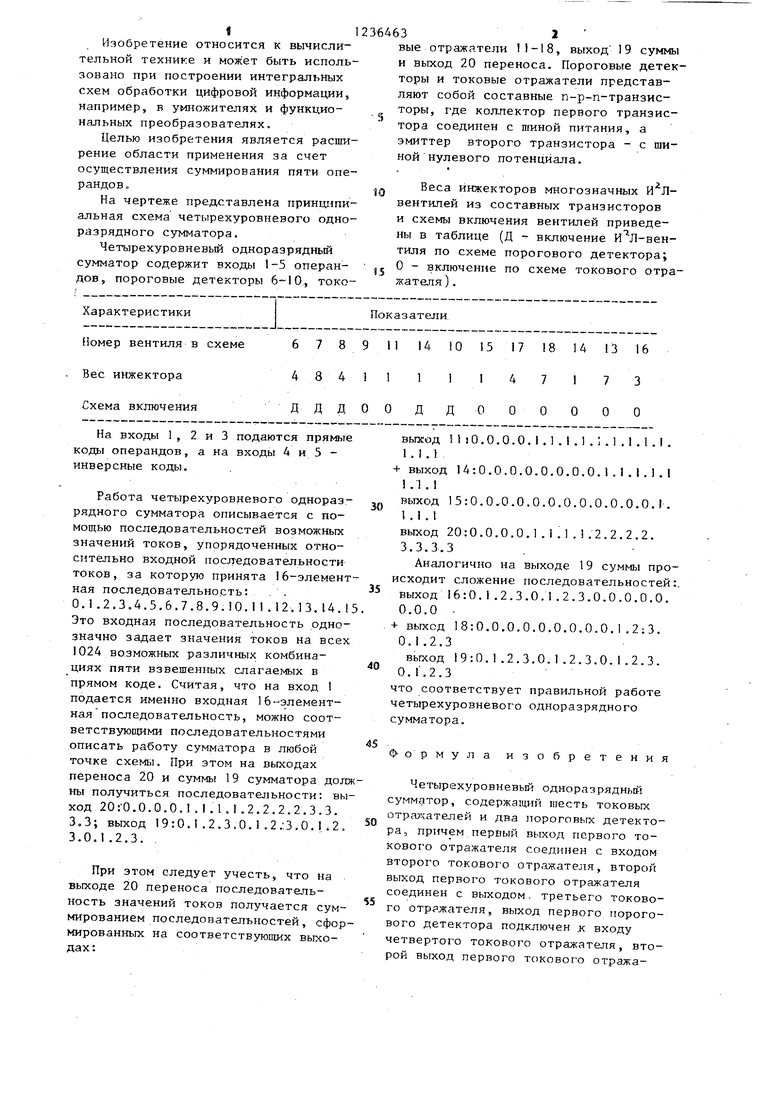

На чертеже представлена принципиальная схема четЕ)1рехуровневого одноразрядного сумматора.

Четырехуровневый одноразрядный сумматор содержит входы 1-5 операндов, пороговые детекторы 6-10, токоНа входы 1, 2 и 3 подаются прямые коды операндов, а на входы 4 и 5 - инверсные коды.

Работа четырехуровневого одноразрядного сумматора описывается с помощью последовательностей возможных значений токов, упорядоченных относительно входной последовательности токов, за которую принята 6-элемент- ная последовательность: . . 0.1.2.3.4.5.6.7.8.9. 10.П. 12. 13. 14. 15 Это входная последовательность однозначно задает значения токов на всех 1024 возможных различных комбинациях пяти взвешенных слагаемых в прямом коде. Считая, что на вход 1 подается именно входная 16-элементная последовательность, можно соответствующими последовательностями описать работу сумматора в любой точке схемы. При этом на выходах переноса 20 и суммь 19 сумматора должны получиться последовательности: вы- ход 20: 0.0.0.0,1 , I .1 , 1 .2.2.2.2.3.3. 3,3; вьпход 19:0,1 ,2.3.0.1 .2,:3.0,Ь 2, 3.0,1.2.3. .

При этом следует учесть, что на выходе 20 переноса последовательность значений токов получается суммированием последовательностей, сформированных на соответствующих выходах :

364632

вые отражатели I1-18, выход 19 суммы и выход 20 переноса. Пороговые детекторы и токовые отражатели представляют собой составные п-р-п-транзис- торы, где коллектор первого транзистора соединен с шиной питания, а эмиттер второго транзистора - с шиной нулевого потенциала.

S

10

Веса инжекторов многозначных вентилей из составных транзисторов и схемы включения вентилей приведены в таблице (Д - включение И Л-вен- тиля по схеме порогового детектора; J, О - включение по схеме токового отра- жатепя).

0

выход niO.0.0,0,1.1.1.1,;.1,1.1.1.

1.1.1

+ выход 14:0.0,0,0.0.0.0,0.1,1.1.1.1

1.1.1

выход 15:0.0.0.0,0.0,0.0,0.0,0.0.1.

1,1.1

выход 20:0.0.0,0.1.1.1,1,2.2,2,2.

3,3,3.3

Аналогично на выходе 19 суммы происходит сложение последовательностей: выход 16:0,1,2,3.0,1,2.3.0.О,0.0,0.

0.0,0 . выход 18:0.0.0.0,0.0,0.0,0,1,2:3,

0,1.2,3 выход 19:0.1.2,3,О,1.2.3,О,1,2,3.

0,1,2.3

что соответствует правильной работе четырехуровневого одноразрядного сумматора.

0

Ф-ормула изобретения

Четырехуровневый одноразрядный сумматор, содержащий шесть токовых отра : ателей и два пороговых детектора, причем.первый выход первого токового отражателя соединен с входом второго токового отражателя, второй выход первого токового отражателя соединен с выходом, третьего токового отрялсателя, выход первого порогового детектора подключен .к входу четвертого токового отражателя, второй выход первого токового отражателя соединен с выходом пятого токового отражателя, первый выход второго порогового детектора соединен с входом шестого токового отражателя, отличающийся тем, что, с целью расширения области применения за счет осуществления суммирования пяти операндов, он дополнительно содержит седьмой и восьмой токовые отражатели и третий, четвертый и пятый пороговые детекторы, причем вход первого токового отражателя соединен с выходом третьего порогового детектора, вход которого подключен к входу прямого кода первого операнда сумматора, вход четвертого порогового детектора соединен с входом прямого кода второго операнда сумматора, первый и второй выходы четвертого порогового детектора сое- динет соответственно с входом третьего токового отражателя и с входом первого порогового детектора, второй выход первого токового отражателя

является выходом переноса сумматора, вход пятого nDporoBoro детектора соединен с входом инверсного кода третьего операнда сумматора, выход пятого порогового детектора соединен с входом второго порогового детек1гора, второй выход которого соединен с входом пятого токового отражателя, первый, второй, третий и четвертый

выходы второго токового отражателя соединены с входом седьмого токового отражателя и подключены к .входу прямого кода четвертого операнда сумматора, выход седьмого токового

отражателя соединен с входом четвертого токового отражателя, выход которого объединен с выходом восьмого токового отражателя и подключен к выходу суммы сумматора, выход шее-

того токового отражателя соединен с- входом восьмого токового отражателя и подключен к входу инверсного кода пятого операнда сумматора.

Чгг

П 18

Редактор Н. Гунько

Составитель А. Степанов Техред М.Ходанич

Заказ 3091/51Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

Корректор В. Бутяга

| название | год | авторы | номер документа |

|---|---|---|---|

| Четырехуровневый одноразрядный сумматор | 1987 |

|

SU1501042A1 |

| Одноразрядный сумматор на инжекционных элементах | 1985 |

|

SU1277096A1 |

| Одноразрядный К-значный сумматор | 1985 |

|

SU1312566A1 |

| Одноразрядный сумматор на инжекционных элементах | 1985 |

|

SU1275430A1 |

| Одноразрядный К- значный сумматор | 1987 |

|

SU1499336A1 |

| Четырехуровневый одноразрядный сумматор | 1982 |

|

SU1095174A1 |

| Сумматор | 1985 |

|

SU1275429A1 |

| Конвейерный сумматор | 1983 |

|

SU1137460A1 |

| Устройство для суммирования двоично-десятичных кодов | 1976 |

|

SU691851A1 |

| Устройство для суммирования Фибоначчи-десятичных кодов | 1989 |

|

SU1649535A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении интегральных схем обработки цифровой информации при многоуроневом представлении информации. Данный сумматор имеет более широкую область применения благодаря возможности суммирования пяти одноразрядных операндов. Цель изобретения достигается введением в известный сумматор на п-р-п-транзис- торах с инжекционным питанием дополнительно двух токовых отражателей и трех пороговых детекторов, выполненных на составлных п-р-п-транзисто- рах, .а также новых связей. I ил. с S N СО о 4 о: со

| Четырехуровневый одноразрядный сумматор | 1982 |

|

SU1095174A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Ргос | |||

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

Авторы

Даты

1986-06-07—Публикация

1984-05-21—Подача